某型飞机1553B 总线控制功能故障分析

2023-04-26王海涛

徐 辉,王海涛

(海装驻南昌地区军事代表室,江西 南昌,330024)

0 引言

MIL-STD-1553B(简称1553B)总线是一种数字式命令/响应时分制数据总线,是第三代军用战斗机所使用的典型数据总线。总线中通信节点按照功能分为三种类型:总线控制器(Bus controller,BC)、总线监控器(Bus Monitor,BM)、远程终端(Remote Terminal,RT)。BC 负责总线消息收发组织和通信调度,MC 负责监控数据总线上的传输数据,对总线传输的消息进行监控和记录,RT 在总线控制器控制下进行数据收发[1-2]。实际应用中,1553B 总线一般采用两个总线控制器:主BC、备份BC,正常工作时主BC 控制整个1553B总线的调度和控制,备份BC 作为RT/MT 监听主BC 工作状态,主BC 发生故障时,备份BC 接管1553B 总线控制,避免BC 单点故障的发生。

某型飞机航电系统采用以1553B 总线为主总线的系统架构,显示与控制管理处理机作为1553B 总线的总线控制器,任务管理计算机作为备份总线控制器,在显示与控制管理处理机正常工作时,任务管理计算机作为远程终端(RT),当显示与控制管理处理机发生故障时,任务管理计算机作为总线控制器(BC),接管显示与控制管理处理机的总线控制功能。

本文介绍了某型飞机1553B 总线主/备份功能控制原理,针对飞机外场使用中出现的主BC 故障、备份BC 接管总线控制的故障现象,对故障发生的原因进行分析定位,对故障的机理进行深层次分析。针对系统故障,对相关软件设计逻辑进行完善,并对完善后的逻辑进行了验证。

1 某型飞机航电系统总线控制模式

某型飞机航电系统主总线采用1553B 总线,系统正常情况下显示与控制管理处理机(DCMP)作为1553B 总线的BC,对总线进行控制管理;当DCMP 故障后,任务管理计算机(MMC)接管1553B 总线的控制与管理权,充当1553B 总线的BC,航电总线系统进入备份控制模式。

DCMP 与MMC 之间的“交、接权”通过飞机座舱内总线控制开关、DCMP 发送给 MMC 的健康线、DCMP 发送给MMC 的1553B 总线信号共同控制。座舱内总线控制开关有三种工作模式:正常、备份1 及备份2。当开关位于“正常”位时,默认DCMP 为1553B 总线控制器,DCMP 故障后,MMC 接管 1553B 总线控制权;当开关位于“备份1”时,强制 DCMP 作为1553B总线控制器,DCMP 故障后,DCMP 重启;当开关处于“备份 2”时,强制MMC 接管 1553B 总线控制权,MMC作为1553B 总线控制器。

本次故障发生时,总线控制开关位于“正常”位,故本文仅考虑在“正常”工作模式时DCMP 和MMC交、接权的情况。 正常工作时,DCMP 每个周期通过1553B 总线向 MMC 发送“心跳”信息,通过 IOC 模块硬线向MMC 输出“健康线”标识。当MMC 在一定周期内未接收到“心跳”信息或“健康线”信号时,通过B总线询问BCMP 是否交权,若MMC 周期内未接收到DCMP 回复的“禁止接权”信号,则MMC 重构系统当BC。

2 故障现象及原因分析

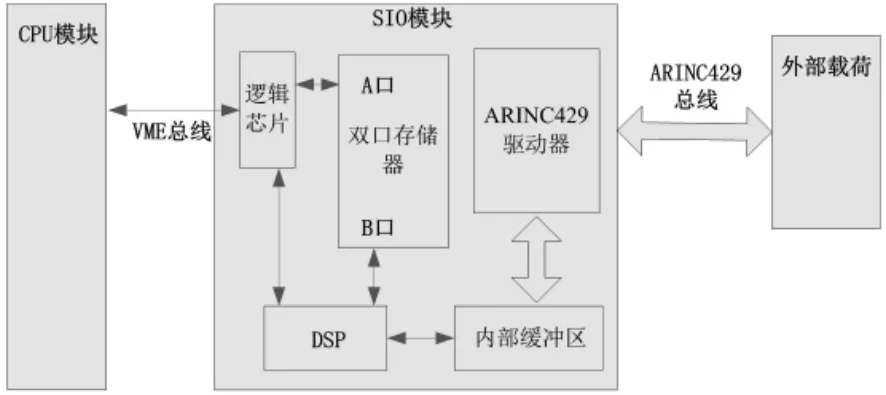

某型飞机航电系统在外场使用过程中多次发生DCMP 交出总线控制权、MMC 接管总线控制权的现象,出现时间不固定。查看DCMP 内非易失性存储器(NVRAM)中记录的信息,发现当故障发生时均记录到“0x300 例外”,其余记录信息正常。“0x300 例外”是指CPU 对系统未配置空间资源进行访问,即访问非法地址。 根据故障发生时记录到的PC 指针,对软件目标码进行反汇编,故障定位为SIO_429_ReadBlock驱动函数错误。 SIO_429_ReadBlock 驱动函数用于统计某一时刻所有ARINC429 通道的数据帧。其工作过程中涉及的硬件资源如图1 所示。

图1 SIO_429_ReadBlock 函数涉及的硬件资源

SIO 模块中的DSP 通过ARINC429 驱动器、内部缓冲区接收外部数据,按照数据格式,通过B 口存储在双口存储器中;CPU 模块经由VME 总线、逻辑芯片通过A 口访问双口存储器,调用SIO_429_Read-Block 函数统计ARINC429 接口接收到的数据帧。根据SIO_429_ReadBlock 函数工作原理及涉及的软硬件资源,建立如图2 所示的故障树,下面依次对故障树中各个底事件进行分析。

图2 0x300 例外的故障树

2.1 软件设计错误(PG1)

软件设计错误会导致程序进行非预期循环,进而导致数组越界,造成0x300 例外。SIO_429_ReadBlock函数的思想为:统计某一时刻各个通道的帧数目,然后将各个通道的帧数目相加,得到该时刻有效帧的计数。经检查,该部分软件算法实现无错误。

2.2 VME 协议实现故障(PG2)

CPU 模块按照VME 协议访问SIO 模块的双口存储器。若VME 协议实现有误,会导致程序进行非预期循环,造成数组越界。针对该情况,参考标准VME 时序,通过示波器采集DCMP、VME 时序并进行对比分析,发现VME 协议符合规定要求,故排除该故障事件。

2.3 VME 硬件走线故障(PG3)

VME 硬件走线是VME 协议的载体,若 VME 硬件走线存在故障,会导致CPU 端读写DPRAM 数据出现错误,进而引起应用程序进入预期外的分支,造成数组越界。针对该情况,对VME 硬件走线进行了静态测量(短路、开路测量)、DPRAM 非竞争模式的访问测试。静态测量表明硬件不存在开路、短路等问题;DPRAM 非竞争模式的访问测试结果表明处理器端的VME 访问控制逻辑功能正确。 测试结果表明硬件走线完好,不存在开路、短路、虚焊等问题。故排除该故障事件。

2.4 双口逻辑故障(PG4)

双口逻辑主要实现 CPU 模块与SIO 模块对DPRAM 的访问。双口逻辑无竞争时工作正常,下面分析双口逻辑在竞争下的访问过程。

CPU 模块通过A 口访问双口存储器 (CE# 置为低),逻辑先将DTACK#置为高,通知CPU 模块等待,若此时SIO 模块正通过B 口访问同一单元,双口会通过A 口发出BUSY#信号,逻辑根据BUSY#信号保持DTACK# 信号的高电平状态,通知CPU 模块继续等待,待BUSY# 信号结束后,将继续保持(1~3 个时钟周期),等待双口完成数据准备,随后逻辑使能读写信号,并通知CPU 模块数据已准备完毕,将DTACK# 信号置低,CPU 模块读取数据后,CE#置高,访问周期结束。若双口逻辑出错,会导致从双口获取的数据错误,影响条件判断,致使程序无法跳出循环。

在双口逻辑代码段加入打印,查看故障发生时的头尾指针和数组下标temp 值。发现当故障发生时,头指针为异常值(非3 的整数倍),temp 一直增加,数组越界,将栈区其他信息改写成采集的ARINC429 数据。另外,捕获双口发生竞争时的数据访问时序图,发现DSP 端在BUSY# 有效时,继续进行数据访问,未对DSP 端的ready 信号进行处理,造成双口数据访问错误。

3 故障机理分析

3.1 双口存储器工作原理分析

双口存储器(DPRAM)通过提供两套访问接口,允许两端设备同时进行访问。在本文中,当DCMP 运行时,CPU 访问DPRAM 某一单元,若此时DSP 端也同时访问该单元,正常情况下DSP 端应收到来自双口的BUSY#,并根据BUSY# 的持续时间维持ready为低状态,保持DSP 端等待。 待CPU 模块完成访问后,再由DSP 端进行访问。 对双口访问逻辑代码中进行走查测试,发现DSP 端访问双口逻辑部分未对BUSYL# 信号进行处理判断,故在CPU 端和DSP 端同时对同一地址进行访问时,会导致数据读取错误,发生故障。

3.2 故障形成过程机理分析

由于ARINC429 接收通道的头尾指针数据储存在DPRAM 中,当DPRAM 发生访问冲突时,逻辑缺陷导致获取的头尾指针发生错误,使软件流程进入非预期循环,导致数组越界。 DPRAM 缓冲区的存储容量为 144(0~143)word(16bits),且缓冲区为环形缓冲区,即当头指针指到143 时再接收数据,头指针将从0 位置重新接收。假定单通道进行数据收发前,缓冲区及头、尾指针位置如图3 中左图所示,某一时刻,SIO 模块接收了3 帧数据,一帧数据包括1 word 的通道号和2 word 的数据。 接收数据后头指针和尾指针在双口中的位置如图3(右)所示。 应用程序周期调用SIO_429_ReadBlock 函数,当检测到缓冲区不为空时,SIO_429_ReadBlock 函数统计该缓冲区接收到的数据。正常情况下,头指针的移动见图4(左)所示。故障发生时的情况如图4(右)所示,由于双口访问逻辑的缺陷,软件获取了错误的头指针位置(本例中错误值为10)。 其中头尾指针正常情况下都是从0 开始每次进行加3 操作,即头尾指针应为3 的整数倍。如果读到的值为非3 的整数倍,会导致while 的判断条件一直为真,循环继续,造成read_data[150]数组越界,栈区被DPRAM 缓存的ARINC429 数据帧改写,导致系统崩溃。

图3 故障机理分析图

图4 故障机理分析图

4 双口存储器处理逻辑改进及验证

4.1 双口存储器处理逻辑改进

针对故障现象及机理分析,对DPRAM 处理逻辑进行如下改进:在顶层文件连接BUSYL#,当DSP 端访问片选CE# 变为有效时,将ready 置低,等待双口的BUSY# 建立。然后根据BUSY# 情况进行判断,如果BUSY# 有效,则等待BUSY# 变为无效,待BUSY#变为无效后,再等待读数据的建立时间;最后待数据有效后,将ready 置高,通知DSP 端采样读数据,并结束访问。

系统驱动程序完善函数SIO_429_ReadBlock 中判断有无接收数据帧的控制逻辑:原控制程序中的循环条件为当前读取的尾指针和头指针不相等,而由机理分析可知,一旦出现头、尾指针读写错误的情况,造成数组下标temp 越界;故完善循环条件,增加对数组下标temp 值的判断,应小于149,否则上报错误并退出循环。

4.2 逻辑改进后的验证情况

将更改后的双口逻辑通过专用的双口竞争测试程序(“狗叫狗”)进行常温、高低温测试,结果显示双口读写正常。 模拟机上ARINC429 环境,DCMP 连接4个外部ARINC429 超载荷的情况下,应用软件循环调用SIO_429_ReadBlock驱动函数,DCMP 工作正常。

5 结语

本文介绍了某型飞机航电系统1553B 总线主/备份控制系统逻辑构型及工作模式,对外场中出现的1553B 主总线控制器异常故障、备份总线控制器接管总线控制权的故障现象进行了原因分析及定位,通过故障树分析法对可能引起故障的原因进行逐一分析,对产生故障的原因机理进行深层次分析研究。分析结果表明:DCMP 访问SIO 模块双口存储器逻辑设计存在缺陷,在特定条件下改写了栈区的数据,引发数组越界,最终造成系统崩溃。

针对故障发生的原因,对DCMP 内SIO 模块双口存储器访问逻辑进行了完善,并且优化了软件代码中缓冲区头、尾指针读取设计和while 判断条件。 经验证,改进措施有效,原故障排除。