驱控一体化多轴伺服系统的FPGA设计与实现

2023-03-19赖培锋吴建华韩勇

赖培锋,吴建华,韩勇

(上海交通大学机器人研究所,上海 200240)

1 引言

伺服系统主要由控制器、功率驱动装置、反馈装置和电动机构成,广泛应用于数控加工、工业机器人、包装加工等领域[1]。随着大规模集成电路和计算机自动控制技术的飞速发展,这些领域对伺服系统的定位精度、速度稳定度、动态响应性、指令响应性等指标提出了更高的要求[2]。目前,多轴运动控制系统中通常采用一个运动控制器加多个伺服驱动器的结构,存在信号传输易受干扰、占用空间大、硬件资源浪费以及成本高等问题。驱动控制一体化可集成运动控制器、驱动器控制电路等功能为一体,使系统结构更紧凑、可靠性增加并且大大降低了成本[3]。传统的电机控制多采用单片机,受限于CPU的运算速度慢,很难设计出优秀的控制系统。FPGA具有高度并行性、实时性好和丰富的资源等优点,使其对多个电机同时进行控制成为可能,FPGA已经越来越多的应用于电机控制等高性能控制领域。文献[4]提出了基于FPGA的多轴运动控制方案,并在SCARA机器人上进行了验证。文献[5]将FPGA运用于三自由度传输机器人,作为机器人运动控制器的核心处理器。文献[6]提出一种基于FPGA的三轴伺服驱动方案,并对系统电流环宽带进行拓展。

针对多个电机的驱动和控制要求,提出一种以FPGA为控制核心、以IPM为驱动核心的六轴控制驱动系统。采用id=0的矢量控制方法,使用硬件描述语言(HDL)设计各模块,并基于各模块集成的SOPC进行软件开发,最后实验验证系统的可行性。

2 系统总体方案

系统目的是通过FPGA完成六个永磁同步电机的电流环和速度环双闭环控制。采用id=0的矢量控制策略对电流进行解耦控制。进行电机电流闭环运算时,需要先获取电机位置和电流等反馈信息,矢量变换后还需通过SVPWM 算法,控制逆变器中功率开关的通断,实现对电机的控制。根据顶层设计思想,在FPGA中开发上述各功能模块,包括编码器反馈、电流采样、矢量控制运算、SVPWM 算法等模块。系统使用的FPGA 芯片是Altera 公司Cyclone IV系列的EP4CE30F23C6。该芯片具有28848个逻辑单元,594kB的内存,最大用户I/O数为535。

Qsys是Altera公司推出的基于图形界面的SOPC集成工具,Qsys库中包括软核处理器和大量的IP核及外设,系统集成工具自动生成互联逻辑,Qsys系统采用Avalon 总线接口来连接各IP核和子系统,从而显著节省了时间,减轻了FPGA设计量[7]。在将各IP核集成SOPC系统过程中,Qsys会为系统中添加的所有组件生成Verilog HDL源文件,然后顶层HDL文件将Qsys中生成的系统和顶层其他的IP核连接起来,Qsys模块实际就是一个功能更强的IP核。

系统总体框架,如图1 所示。在Quartus II 工具中的顶层HDL文件包括PLL锁相环、六个编码器读取IP核以及Qsys系统。其中,Qsys系统包括集成工具自带的Nios II软核处理器、电流采样、矢量控制运算、六个PWM波生成等独立开发的IP核。Nios II是SOPC 系统总的调控中心,相当于计算机系统中的CPU,最后Qsys工具将上述各IP核集成一个SOPC系统。系统实际运行时,编码器读取模块和电流采样模块先分别读各个电机的各相电流值和位置数据,Nios II将上述IP核的寄存器中读取的数据作为矢量控制运算IP核FOC的输入,FOC的输出是Park逆变换的计算结果uα、uβ,它们作为PWM波生成IP核的输入,通过SVPWM算法生成一定占空比的六路PWM控制信号,最后输出给功率驱控板上的各个IPM,实现同时对六个永磁同步电机的驱动控制。

图1 系统总体框架Fig.1 Overall Framework of System

3 系统模块化设计

3.1 编码器反馈

伺服系统中电机所使用的编码器为日本多摩川公司TS5667系列的单圈17位、多圈16位绝对值编码器,它与FPGA采用RS−485 异步串行通讯协议进行通信,通讯波特率为2.5Mbps。RS−485接口采用差分信号,具备对噪声的有效抑制能力、高效的数据传输速率、良好的数据传输的可靠性能,可进行远距离传输。

控制板卡上使用德州仪器公司的RS−485收发器SN65HVD0 8,该收发器需要(3~5.5)V的供电电源,它的静态功耗小,最高通讯波特率可达10Mbps。控制板卡上总共需要六个SN65HVD08芯片,对应六个电机的编码器,充分利用了FPGA的高度并行处理能力。

SN65HVD08收发器接口电路,如图2所示。差分信号Enc_A、Enc_B分别与编码器的A、B差分线连接,RX、CTRL和TX这三个信号与FPGA芯片的引脚相连。收发芯片有驱动器和接收器两种工作模式,FPGA通过控制CTRL信号确定芯片的工作模式。当CTRL为高电平时,DE信号有效,芯片处于驱动器工作模式,FPGA通过TX向芯片发送请求信号,然后芯片通过差分线将请求信号传送给编码器,编码器接收到信号后会返回对应的位置信号给FPGA端。当CTRL为低电平时,REn信号有效,芯片处于接收器的工作模式,芯片把编码器端的信号通过RX 传输给FPGA 的I/O 接口端,然后FPGA再将接收到的串行数据通过编码器IP核解码并转换成并行数据。IP核工作的时钟频率为20MHz,从FPGA发送请求信号到位置信息返回整个时间周期约为30.7μs。

图2 收发器接口电路图Fig.2 Transceiver Interface Circuit Diagram

3.2 电流采样

采用需采样电阻的隔离电流传感器对功率板上的智能功率模块输出给电机的电压模拟量进行采样、隔离放大,然后通过ADC78H89转换为数字量。该ADC是一款低功耗,7通道的12位串行模数转换芯片,转换速率可达500KSPS,能够兼容SPI通信协议。FPGA作为主设备与从设备ADC通过SPI协议进行通信获取各电机的反馈电流值。FPGA与ADC通信原理图,如图3所示。

图3 FPGA与ADC通信原理Fig.3 Communication Schematic Diagram of FPGA with ADC

永磁同步伺服电机可以看作是三相平衡负载的,故三相电流之和等于0,因此只需对电机三相电流中任意两项进行采用即可,2个ADC的多个转换通道分别采样六个电机的U相、V相电流模拟信号。为了保证可靠性,每个PMSM 的两相电流值应同时被FPGA端获取,充分利用FPGA能并行处理的优势,将FPGA发出的DIN、SCLK(50KHz~8MHz)、CSn 三个信号同时发送给两个ADC,实现FPGA同时与两个ADC从机通信,当所有电机电流采样完成后,IP核发出中断请求信号,Nios II通过Avalon总线读取IP 核的寄存器电流值,然后进行矢量控制运算。使用Verilog HDL开发电流采样IP核,它包括时钟分频、逻辑控制、发送寄存器、移位寄存器、U 相接收寄存器以及V 相接收寄存器等部分。FPGA 外部提供时钟为50MHz,因此需要对其8 分频才能满足ADC低于8MHz的工作时钟范围。

3.3 矢量控制

永磁同步电机矢量控制原理,如图4所示。可以通过Clarke变换和Park变换将永磁同步电机数学模型从三相静止坐标系转换到两相同步旋转坐标系:

图4 矢量控制原理图Fig.4 Field Oriented Control Diagram

式中:p—电机极对数;Ψf—永磁体磁链;Ld、Lq—直轴和交轴的等效电感;Ti—积分时间常数。采用id=0的矢量控制策略时,Te=pΨfiq,此时电机电磁转矩只与电流分量iq有关,通过控制其大小就可以控制电机输出转矩[8]。

矢量控制涉及大量的数学运算,为了加快系统的运行速度,基于模型设计的思想,使用DSP Builder工具设计矢量控制运算FOC IP 核。DSP Builder是Altera公司推出的一个算法级设计工具,它同时把算法仿真建模和RTL级的两个设计连接起来,使算法的开发到硬件的实现可以无缝地过渡[9]。在MATLAB/Simulink中建立、仿真并验证正确的算法模型(mdl文件),通过DSP Builder中的Signal Compiler模块转化成VHDL文件,或者作为一个自主定义的硬核集成到SOPC系统中,大大简化了FPGA功能模块的开发流程,同时关键算法模块的硬件实现提高了程序的执行效率。

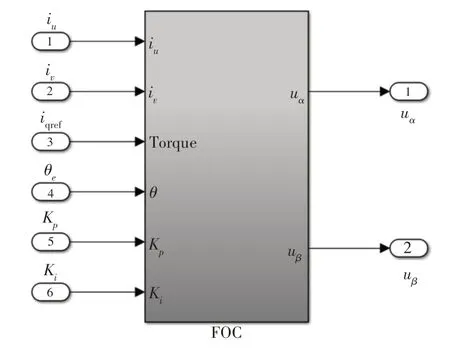

FOC模块包括Clarke变换、Park变换、Park逆变换和PI调节器。利用Simulink工具选择合适的模块组件搭建FOC控制算法模型,其中三角函数的运算使用查找表法实现。最后,将验证无误的FOC模型利用DSP Builder工具生成可以嵌入到FPGA的IP硬核。生成的FOC IP核,如图5所示。输入部分包括电流指令值iqref、PI控制参数kp和ki、电气角度θe以及反馈电流iu和iv,输出为uα、uβ,它们将用于SVPWM算法中。

图5 DSP Builder联合生成的FOC IP核Fig.5 FOC IP Core Jointly Generated by DSP Builder

3.4 SVPWM算法

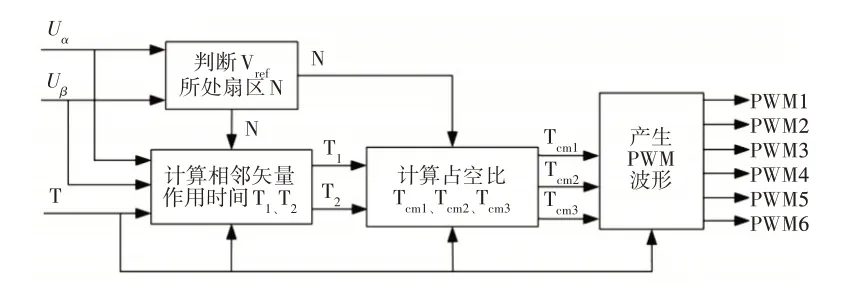

考虑到空间矢量调制SVPWM 算法具有能够优化输出电压波形、母线电压利用率高、易于数字实现等优点,采用SVPWM控制算法生成电机控制所需的PWM信号[10]。SVPWM算法原理结构框图,如图6所示。矢量运算FOC IP核计算输出的uα、uβ以及三相功率器件的开关周期T是该模块的输入,输出为六路PWM控制信号。通过uα、uβ的值判断空间电压矢量的扇区号N,根据扇区号计算出基本电压矢量的作用时间,然后转化为对应的占空比。为了使谐波畸变尽可能小,采用7段式SVPWM,并通过三角载波与占空比比较得到六路两两互补、带死区的PWM控制信号。使用Verilog HDL开发PWM波生成IP核,该模块包括硬件逻辑控制、三角波产生、比较寄存器、比较单元、死区插入单元等部分,输入为Avalon−MM总线和各相占空比,输出为六路PWM信号。扇区判断和各相占空比的计算通过软件实现,PWM波生成通过IP核硬件实现。

图6 SVPWM算法的原理结构框图Fig.6 Principle and Structure Diagram of SVPWM Algorithm

3.5 电机驱动部分

功率驱动部分的主要作用是通过PWM控制信号作用,把整流后的直流电转变成三相交流电供给伺服交流电机[11]。功率驱动核心部件是六个IPM模块,采用IR公司IRAMX20UP60A型号的IPM,它集成了三相逆变驱动器、三相逆变桥、内部自举元器件和多元化的保护电路,最高直流母线电压为600V,PWM 的最高载波频率为20kHz,需要(12~20)V 供电电压,具有过电流、欠电压、短路和过热保护等功能[12]。功率驱动板上弱电与强电之间使用HCPL0631 光电耦合器进行光耦隔离,增加抗干扰性和安全性,FPGA控制端输出的PWM信号经过光电耦合器后传给IPM。为保证控制电源能够为上桥臂功率器件提供正确的门级偏置电压,需要在IPM外围设计自举电路。此外,驱动部分还包括电流采样电路,IPM输出的三相正弦交流电通过采样电阻,再经过隔离电流传感器HCPL−7520隔离放大后获得ADC采样的模拟量。

4 系统软件设计

SOPC 系统使用32位嵌入式RISC 指令集,以Nios II软核处理器为核心,在FPGA上完成了系统各模块的开发后,在Qsys平台Nios II结合Avalon总线将各个IP核集成一个SOPC系统,要想实现对电机的控制,然还需对该SOPC 硬件系统进行软件开发。Quartus II上自带Nios II软核开发工具Eclipse,并提供了C/C++软件开发套件。

Nios II程序包括主函数和中断函数,主函数主要完成电机控制相关参数的初始化和注册中断服务函数。当电流采样IP核完成所有电机的两相电流采样后,会向Nios II发出中断请求信号,程序进入中断处理子函数。

中断处理函数主要实现以下功能:各个电机位置信息和反馈电流值读取、速度指令值接收以及速度环计算、矢量控制运算、计算SVPWM 扇区和占空比、记录电机实际运行数据至片上RAM中。FOC运算以及六路PWM波的输出都是通过硬件实现的。系统中断程序的流程,如图7所示。

图7 中断程序流程图Fig.7 Flow Chart of Interrupt Procedure

控制系统中,电机速度环和电流环控制采用PI控制器,连续PI控制器的调节规律为:

式中:u(t)—输出;e(t)—输入误差;Kp—比例系数;Ti—积分时间常数。数字PI控制有位置式和增量式两种实现方式,采用位置式,上式经离散化处理后可表达为:

式中:e(n)—第n个周期的采样误差;u(n)—第n个周期的输出。为避免系统受到冲击,需要对积分输出和PI控制器总输出均做出限幅处理。最后,在Eclipse平台编写函数实现PI控制器。

5 实验验证

对上述开发的IP核功能模块、集成的SOPC硬件系统以及基于Nios II控制程序进行实验验证。控制系统实验平台,如图8所示。包括以FPGA为核心的控制板卡、以六个IPM为核心的功率驱动板卡和六个永磁同步电机。实验均在电机空载下进行,永磁同步电机参数,如表1所示。

图8 实验平台Fig.8 Experimental Platform

表1 永磁同步电机参数Tab.1 PMSM Parameters

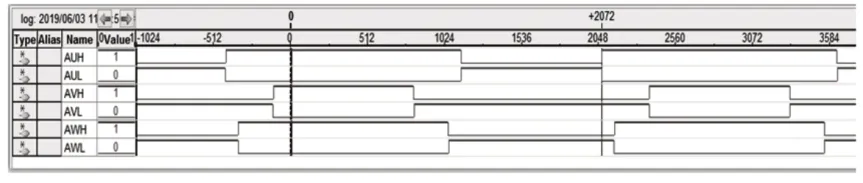

Quartus Ⅱ开发平台上使用嵌入式逻辑分析仪Signal Tap II对系统运行时PWM波生成IP核的功能进行验证,分析仪实时监测的实际运行结果,如图9 所示。该功能模块能正确生成带0.5μs死区时间、频率为8kHz的六路PWM控制信号。

图9 PWM波生成测试结果Fig.9 PWM Wave Generating Test

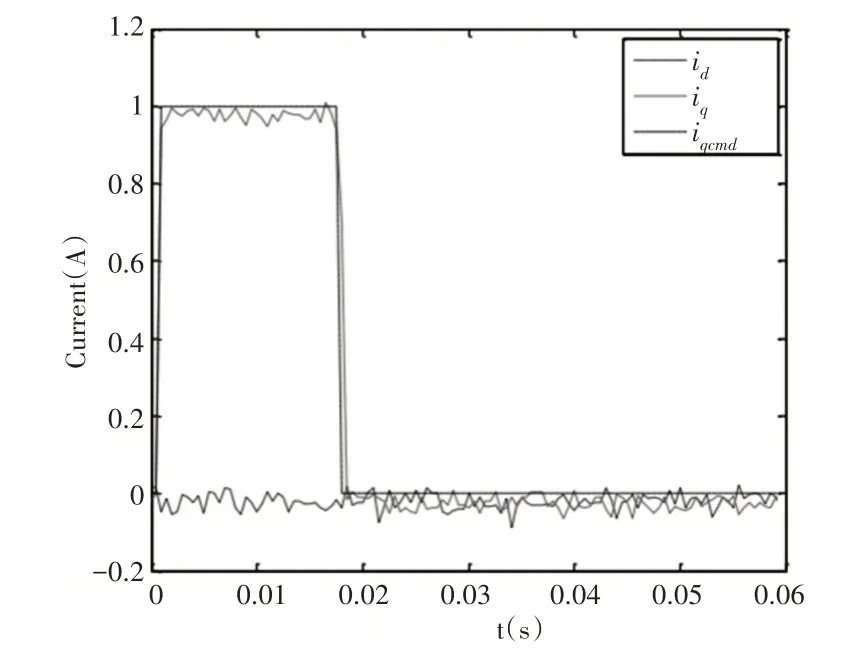

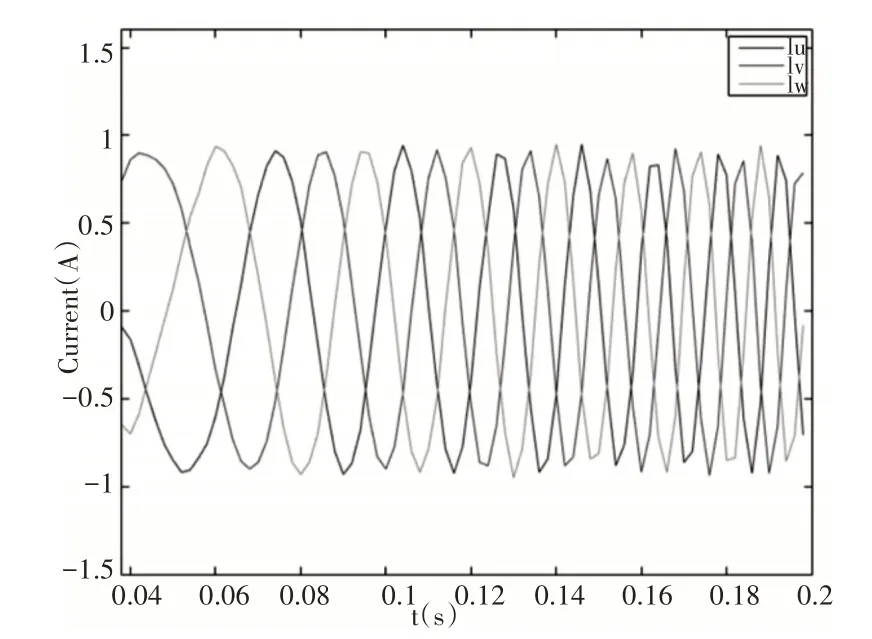

在SOPC中添加的FPGA片上RAM 用于对电机实际运行时三相电流值、iq反馈值、转速等数据进行记录。用所记录的数据在MATLAB 中绘制图形,电流环的阶跃响应实验结果,如图10 所示。电流环运行频率为8kHz,电流指令值iqcmd为1A,上升时间为0.83ms,iq反馈的平均值为0.978A。对应的电机实际三相定子电流值,如图11所示。

图10 电流环阶跃实验Fig.10 Step Test of Current Loop

图11 电机三相定子电流Fig.11 Three Phase Stator Current

电机转速阶跃响应实验结果,如图12所示。速度指令值为366r/min,上升时间约为7ms,速度平均值为365.6 r/min,实验结果表明系统具有良好的响应特性。

图12 速度环阶跃实验Fig.12 Step Test of Speed Loop

6 结论

设计了一种以FPGA为控制核心,以IPM为驱动核心的驱控一体化多轴伺服系统。基于FPGA使用硬件描述语言实现了电机编码器数据采集、电流采样、矢量控制运算和PWM信号生成等功能模块的开发,并在各模块集成的SOPC上进行嵌入式软件编程,实现了同时对六个永磁同步电机的驱动控制。通过实验验证了伺服系统响应速度快,稳态误差小。使用FPGA对各功能模块硬件实现,使运算能够并行执行,大大提高了程序运行效率、缩短开发周期,开发的伺服系统具有较高实用价值。