基于浮栅型薄膜晶体管的光控多值存储器

2023-03-04李博文张国成秦世贤邢俊杰李志达赖秉琳

李博文,张国成,秦世贤,邢俊杰,李志达,赖秉琳

(福建理工大学 微电子技术研究中心,福建 福州 350118)

1 研究背景

人机交互设备的兴起,对电子设备的柔性、透明及温度敏感等性能提出了新的要求[1]。有机材料具有来源广、成本低、范围宽的光响应能力等优势,用有机材料制作的设备和器件材质轻薄、韧性高,更易做成大面积柔性器件[2]。20世纪70年代,有机半导体聚合物的问世使得有机薄膜晶体管得到快速发展[3]。有机材料的成膜方法多样,将有机物配成溶液后进行薄膜加工,低温(<200 ℃)退火,能有效控制薄膜的厚度与表面粗糙度,且对设备要求低,使晶体管的加工效率提升[4~5]。由于大数据背景下摩尔定律失效及冯·诺伊曼计算构架的限制,存储元件及其他电子器件的功能势必迎来一次革新,以应对硬件性能限制信息处理效率的局面。近年来,浮栅层加辅助层的新型器件结构逐渐成为热门研究方向。Wang等[6]提出了一种基于二维材料的浮栅型非易失性存储器,采用双栅结构以降低工作电压、提高数据保持时间。Li等[7]通过插入半导体层以增强存储器的性能。Gao等[8]制备了一种异质结构垂直有机光电存储器晶体管,该器件可以从非易失性存储器转变为人工突触,展示了一种制造高性能非易失性光电存储器和人工突触的新技术。Chiang等[9]利用一种基于聚合物/钙钛矿量子点(QD)混合纳米复合材料作为光响应浮栅的光电晶体管存储器,实现了完全可光切换的存储器件。Fu等[10]采用串联结构,由发光电阻式开关存储器和钙钛矿太阳能电池组成了一种电阻式开关存储器,器件的状态可以进行电和光编码,具有高电阻状态和低电阻状态。

在溶液法加工过程中,若相邻两层薄膜的材料的溶质、溶剂的相容性不正交,会造成薄膜交界面互溶、损坏。而无机材料与有机材料的特性在某种程度上能够搭配、互补。无机材料通常被认为是热稳定性、化学稳定俱佳的材料。但许多无机薄膜生长过程中常伴随着高温、高压,对生产设备要求极高,导致生产成本提高,大面积生产受限。随着技术进步,无机薄膜的制备工艺逐渐完善,甚至出现溶液法制备无机薄膜的工艺。因此,除了纯有机晶体管,有机-无机薄膜晶体管器件的研究也得到关注。

本研究制备了一种可光调控的异质结晶体管信息存储器,器件结构结合了有机材料与无机材料的优点,通过PN半导体层异质结、有机浮栅层掺杂与控制无机隧穿层厚度达到控制存储器性能的作用[11],存储器性能可光调制、存储窗口为60 V、开关比为104。另外,通过使用吸光的共混半导体,使器件具备了一定的光传感、光检测的功能,在光电协同控制下,具有3个等级的电流水平信号。同时对光、电两种信号敏感的有机晶体管存储器,在电子设备中可作为基本信号存储单元与光感受器,在信息处理、运算和显示等场景中也具有较强的应用潜力,可在智能手机、计算机、显示器等功能日趋多样化的电子设备中发挥作用。

2 器件的制备

2.1 器件结构

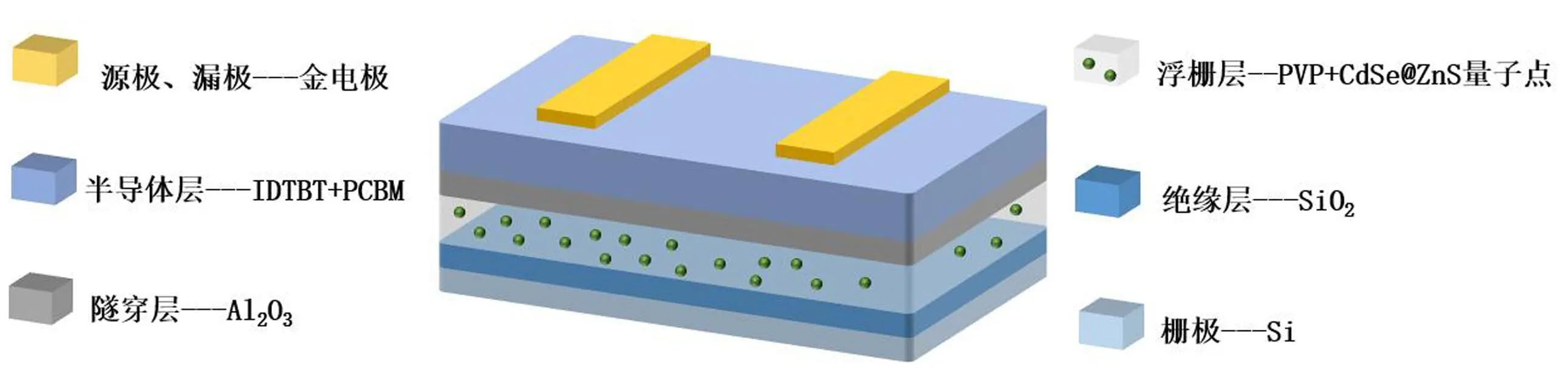

器件制备使用的基底是单面抛光的氧化硅片,纯Si层充当栅电极,SiO2层充当绝缘层,如图1所示。源漏极是用掩模版真空热蒸发下形成的图案化电极,电极间沟道尺寸1 000 μm*30 μm;半导体层是溶液旋涂法制成的P型、N型半导体共混异质结;隧穿层为Al2O3;浮栅层为内部分散有CdSe@ZnS量子点的PVP绝缘层。

图1 器件结构图Fig.1 Device structure diagram

2.2 材料

本研究所采用的晶体管衬底、栅极及绝缘层为单面抛光SiO2,购于苏州晶矽电子科技有限公司;浮栅层为掺有量子点的聚合物PVP薄膜,其溶液由PVP和交联剂HAD溶解于溶剂PGMEA组成(均自Sigma-Aldrich);电荷捕获材料为CdSe@ZnS量子点,购买于普加福光电;隧穿层材料为原子层沉积的Al2O3;半导体层材料为聚合物IDTBT和PCBM溶解于溶剂CHCl3,其中,聚合物IDTBT和PCBM来自1-Material;电极材料Au颗粒来自普加福光电;溶剂CHCl3及硅片清洗试剂丙酮(99.9%)、异丙醇(99.9%)来自国药集团化学试剂有限公司。

2.3 晶体管工艺制备过程及参数

(1)基片清洗与溶液配制

第一步,使用丙酮、异丙醇、去离子水依次对基片进行清洗,用氮气(N2)喷枪吹干衬底表面残留的液体。

第二步,按 CdSe@ZnS 量子点:先配制 PVP 溶液,将150 mg PVP和15 mg HDA交联剂溶解在1 mL的 PGMEA溶剂中,并在磁力搅拌器上60 ℃搅拌溶解24 h。

第三步,取 CdSe@ZnS 量子点溶液(溶剂为CHCl3、5 mg/mL)加入PVP溶液中(CdSe@ZnS:PVP的质量比为1∶10)配成浮栅层溶液。

第四步,配制半导体溶液,ITDBT∶PCBM质量比为4∶1,混合溶解在CHCl3中,60 ℃加热2 h。

(2)各层薄膜制备

浮栅层的制备是利用设备型号为Therom/EZ6的旋涂机,用直径为0.22 μm的过滤头将浮栅层溶液滴到基片上,使用两步旋涂法,600 r/min旋涂5 s,2 000 r/min旋涂30 s,后将样品移入手套箱,120 ℃退火2 h。

隧穿层的制备是利用设备型号为Beneq TFS 200型的原子沉积设备(ALD),在浮栅层上利用原子沉积法(ALD)制作8 nm厚的Al2O3作为隧穿层。

半导体层制备所利用的设备与浮栅层相同,将半导体溶液滴在Al2O3上,1 000 r/min旋涂60 s 后,140 ℃退火10 min。

电极的制备是利用设备型号为BOX-RH400型的真空蒸镀机,利用特制掩模版蒸镀上一对金电极作为源极和漏极,用设备型号为Keysight B2912A的半导体测试仪进行器件性能测试。

3 实验结果分析与讨论

晶体管的转移曲线如图2所示,栅极电压Ug在40~-40 V变化,源漏极电流Ids也随之变化。Ug=2 V时,Ids有明显的上升趋势;至Ug=-35 V时,Ids趋于稳定,电流饱和,可以读取到最大的开态电流。这个过程中,Ug=2 V被称为阈值电压或开启电压,是晶体管源漏极开始导通的一个临界电压值。

图2 晶体管的转移曲线Fig.2 Transistor transfer curve

浮栅型有机场效应晶体管存储器的工作原理为:栅极施加正电压Ug> 0 V,使半导体层中部分激子分离成空穴与电子,电子受栅极电压的影响,越过隧穿层进入浮栅层,并被天然具有电子捕获能力的CdSe@ZnS 量子点所捕捉[12]。撤去栅压后,电子无法立刻回到半导体层,在浮栅层聚集形成一个内建电场,吸引半导体层中的空穴在隧穿层上表面聚集,逐渐形成高电导的沟道,存储器沟道电流Ids呈高电平“1”,并且由于内建电场持续存在,该高电平可以被保留一段时间。栅极施加负电压Ug<0 V,则空穴被浮栅层捕获,沟道电导下降,存储器沟道电流Ids呈低电平“0”。

首先对存储器的存储窗口和开光比进行测量。栅极正脉冲电压:+40 V、2 s(编程电压),晶体管阈值电压增大,转移曲线右移,在理想情况下Ug=0 V时,读取到开态电流Ion(“1”);栅极负脉冲电压:-40 V、2 s(擦除电压),晶体管阈值电压减小,转移曲线左移,此时在UG=0 V时,可读取关态电流Ioff(“0”)。

如图3所示,在黑暗条件下,分别加栅极电压(±40 V、2 s)后,转移曲线右偏趋势弱,在Ug=0 V读取的电流水平Ids较低,开关比Ion/Ioff=102,存储窗口为30 V。而在200 mW/cm2、675 nm的红光光源照射下[13],分别加栅极电压(±40 V、2 s)后,转移曲线右移幅度增加,此时Ug=0 V,读取到开关比Ion/Ioff≥104,存储窗口为60 V,高低电平(“1”与“0”)区分度很高。

图3 黑暗条件下与红光照射下存储器的编程态、擦除态的转移曲线Fig.3 Transfer curve of programmed state and erased state of memory under dark condition and red light irradiation

根据以上分析可知,光照前后,晶体管的存储窗口由30 V升至60 V,Ug=0 V读取电压下开关比相差20倍。并且一个场效应晶体管上可以表达出3种逻辑电平,即675 nm红光下的“1”、黑暗下的“中间态”和“0”,呈明显的光可调制的逻辑状态。

为验证PN共混半导体层的光电特性对提高器件开关比的作用,做了对照试验。第一种情况是仅IDTBT做半导体层的器件,UG=0 V时,Ion/Ioff=103。第二种情况是用IDTBT与PCBM共混做有源层的器件,Ug=0 V时,Ion/Ioff=104。两种情况在0 V读取下的电流开关比相差10倍,如图4(a)所示。这一差距在线性度坐标下更加明显,如图4(b)。因为IDTBT混入少量PCBM后,两种半导体材料能级不同,PCBM的低能级也能够捕获IDTBT的高能级电子[13~14],如图4(a)所示。在红光照射下施加正栅压,更多的激子分离成空穴、电子,一部分电子进入浮栅层,另一部分来不及被浮栅层捕获的电子被半导体层中离散分布的PCBM捕获[15],导致半导体层中产生更多的空穴,空穴沟道的电导进一步提高,开态电流Ion增大,如图5所示。因此PN共混半导体结构的器件开关比会更大。

图4 PN共混半导体层的光电特性对提高器件开关比的作用Fig.4 Effects of photoelectric properties of PN blend semiconductor layer on improving switching ratio of devices

图5 IDTBT有源层与ITDBT∶PCBM=4∶1有源层下器件的导电沟道变化Fig.5 Change of conductive channel of devices under IDTBT active layer and ITDBT∶PCBM=4∶1 active layer

为了测试存储器的信息保留时间,栅极施加编程+40 V电压2 s后,保持Ug=0 V、源漏极Uds=-20 V 读取存储器的电平信号,信号持续时间即信息的保持时间。加栅压后3 000 s内仍能维持稳定高电平信号,并且电平信号下降趋势减缓,预估高电平信号可以至少维持10 000 s,如图6所示。

图6 存储器的信息保持时间Fig.6 Information retention time of memory

4 总结与展望

本研究提出了一种可光调制的浮栅型场效应薄膜晶体管存储器,结合了有机材料与无机材料的优势,使器件具有接近60 V的大存储窗口,具备实现多级存储器的潜力。

当Ug为0 V时,675 nm红光下可读取到开关比大于104的高电平信号,黑暗条件下读取的电平信号略有下降,开关比为102。器件表达出“1”“中间态”“0”3种具有明显区分度的电平状态,有望实现三值逻辑存储,提高信息存储密度。实验证明了PN共混结构的半导体有源层(IDTBT:PCBM),比纯IDTBT有源层结构,能更加有效提高存储器的开关比,为改善薄膜晶体管存储器的性能提供了一个新的思考方向。