一种具有基极补偿技术的高速运算放大器

2023-02-28李洪品杨发顺

李洪品,杨发顺,2,3,马 奎,2,3

(1 贵州大学大数据与信息工程学院,贵阳 550025;2 贵州大学半导体功率器件可靠性教育部工程研究中心,贵阳 550025;3 贵州大学贵州省微纳电子与软件技术重点实验室,贵阳 550025)

0 引 言

作为电子系统的基本单元,集成运算放大器是由多级放大电路直接耦合而成的高增益模拟集成电路,按照不同的需求、应用可以分为多种类型[1]。本设计的电路属于高速运算放大器,一般泛指带宽高于50 MHz 的运放,应用于光学ToF 系统的高速运放甚至能达到8 GHz。 高速运算放大器具有宽带、高转换速率、低失真和噪声小等突出特点,像ADI、TI 等公司甚至能在维持性能的基础上,较大限度地降低电路功耗。 目前,高速运放广泛应用于A/D 和D/A 转换器、波形发生器和视频放大器以及一些光学应用中。

本文采用了一种高速互补双极工艺。 相比于CMOS 工艺,高速互补双极工艺能为集成电路提供更大的跨导、更大的增益以及低噪声、低失调等特性;并且该工艺采用SOI 全介质隔离技术为器件提供高封装密度以及低寄生电容,从而在提升集成度的同时,提高了电路的运行速度。

基于该工艺,本文设计了一款可用于包括视频监控器、CATV、彩色复印机、图像扫描仪和传真机等许多高速应用的高速运算放大器。 本文的电路采用的是普通β 管;因为一般三极管基极电流在微安级别,在外围电路上产生的压降会增大失调,因此该设计会采用基极电流补偿技术,使电路满足高速的同时,也提高了运放的精度。

1 电路设计与分析

1.1 高速互补工艺特点

优良的电路结构能够优化并进一步提升电路性能,而工艺则决定了电路的上限。 本文所使用的高速互补工艺采用由SOI 和深槽隔离技术组成的全介质隔离技术:SOI 是一种在绝缘层上生长一层具有一定厚度的单晶硅薄膜材料的技术[2-3],其通过绝缘层实现了器件和衬底的全介质隔离;该技术与传统体硅技术相比具有无闩锁、功耗低、集成度高、耐高温等特点,并且其寄生电容小,因此相比于体硅技术器件,SOI 器件能够有效提高电路运行速度。 深槽隔离技术能够增强晶体管的传输特性,降低寄生电容,提高晶体管的高频特性。

综合前文论述的优点,并结合互补双极工艺纵向NPN 晶体管和PNP 晶体管性能接近这一特点,该高速工艺有极小的寄生电容,NPN 管与PNP 管都有很高的特征频率fT,能够在同一功耗的情况下,极大提高整体电路速度并使电路具有很好的高频响应特性。

1.2 高速输入级电路设计

本文介绍输入级电路结构如图1 所示。

图1 采用基极补偿技术的输入级Fig. 1 The input stage with base compensation technology

由Q1、Q2、Q17、Q20组成折叠式共射-共基串接组态,其有源负载是由Q18、Q21、Q19、Q22组成的改进型威尔逊电流镜。 该结构从折叠点看进去的等效电阻大约为1/ gmP,则输入管上密勒电倍增效应大概为:

其中,Cμ为输入管上的寄生电容。 可以看到该结构大大降低了输入管上密勒效应对带宽带来的影响,并且为增大输入级带宽,输入对管Q1、Q2上的寄生应尽可能小。

减小输入级等效跨导可以降低频率补偿所要求的电容值。 以图2 所示采用密勒补偿电容的二级运放为例。

图2 采用密勒补偿二级运放Fig. 2 Two stages op-amp adopting Miller compensation

第一级的等效跨导表达式为:

第二级高频传递函数约为:

则整个二级运放的传递函数为:

假设在w0处传递函数为1,并且电路系统稳定;那么当减小第一级等效跨导时,为维持w0处传递函数依然为1,那么补偿电容也应做相应的减小;并且大信号的响应取决于偏置电流对结点处等效电容的充电速度;因此对于给定的偏置电流在输入对管上增加射极电阻可以使补偿电容所需的容值降低[1+(gmN RE)],而压摆率将提高[1+(gmN RE)]倍,大大提高了电路对大信号的响应速度;当电路带宽大时,即使在高频信号下电路也依然有很短的建立时间。

因为增大尾电流能够有效增大压摆率,但同时也会增大运放输入偏置电流;若采用图3 中的传统基极电流补偿结构,会由于工艺偏差的问题,使得跟随管Q3、Q4的β值不会跟Q1、Q2完全匹配,并且由于Q5、Q6与Q7、Q8存在基极电流以及厄尔利效应的影响,使得补偿电流会与Q1、Q2的基极电流存在偏差;并且2 个电流镜结构也无法做到完全对称,因此补偿电流的不对称会极大地增加失调电流。

图3 传统基极电流补偿结构Fig. 3 Classical base current compensation structure

综上所述,本文设计了一种基极电流补偿结构来解决上述提到的问题。Q6、Q7、Q8、Q10、Q12、Q13组成基极电流消除电路,电路结构见图1 虚线框。 其中,Q6、Q7、Q8、Q10起到基极电流消除的作用,Q12、Q13钳住Q10的基极电位;Q10的基极电位为:

为使Q10的基极电位与Q1、Q2的基极电位相同,要求Q10与Q1、Q2匹配,R8与R3匹配,Q3与Q11匹配,R9的阻值为R5的2 倍,分配到R9上的电流为R5上的一半,则Q10的发射极电位等于Q1、Q2的发射极电位,则VBE10=VBE1,且皆有相同的基极电流;Q10管的基极电流通过Q6、Q7、Q8所组成的电流镜结构,将Q10管的基极电流分别送入Q1、Q2的基极[4],补偿输入对管的基极电流。 相比于2 个电流镜结构,该多输出电流镜的匹配性更佳,避免了补偿电流不对称的问题。 因为厄尔利效应的影响会使Q10与Q1、Q2的基极电流存在偏差,故要使Q9、Q14~Q16、R6、R10与Q4、Q20~Q22、R1、R12匹配,从而使Q10与Q1、Q2的集电极电位相同,最终使VCE10=VCE1=VCE2,消除厄尔利效应的影响。 因此,该补偿结构的对称性要好于传统补偿结构,不会因工艺流程中的偏差而带来较多的失配。

1.3 偏置电路设计

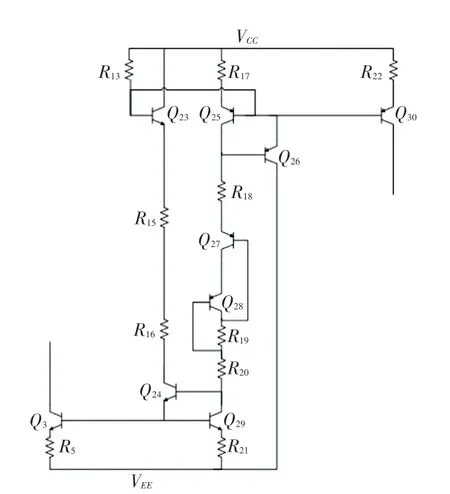

偏置电路为整个电路提供基准电流和偏置电压,使电路能够处于正常的工作状态,其电路结构如图4 所示。

图4 偏置电路Fig. 4 The bias circuit

图4 中,R17~R21所在支路上会产生基准电流,并分别通过Q25、Q29按比例分配到Q3、Q30所在支路上。 基准电流大小为:

该偏置电路采用由Q25、Q26、Q30和Q24、Q3、Q29组成的2 个β -helper 电流镜结构;相比于普通电流镜结构,该结构降低了由晶体管基极电流造成的电流误差,提高了电流镜精度。

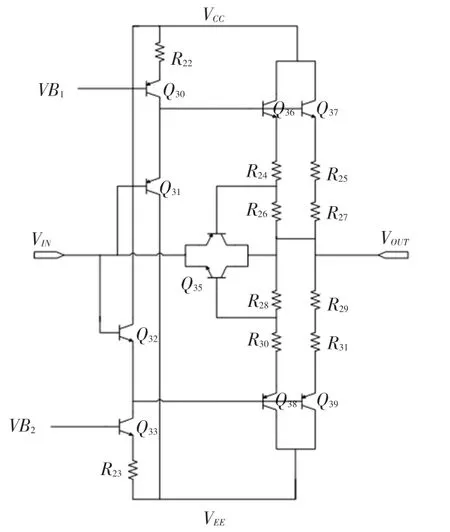

1.4 输出级电路设计

输出级电路主要是由Q31、Q32、Q36、Q37、Q38、Q39组成的双缓冲AB 类输出级,电路结构如图5 所示。其中,Q31、Q32的作用类似于二极管:当VIN为0时,Q36、Q37的基极电位为VBE31,Q38、Q39的基极电位为-VBE32,则此时Q36、Q37、Q38、Q39处于临界导通状态,能够有效避免交越失真的问题。 该结构带负载能力强,能够降低前级受到的负载效应,并为负载提供较大功率。

图5 双缓冲输出级Fig. 5 The double buffered output stage

输出级电路工作原理:由KVL 关系得VBE36,37+;当输入信号为正时,会降低Q31、Q38,39的BE压降,提高Q32、Q36,37的BE压降,降低Q31的导通,提高Q32的导通,使流入Q36,37的基极电流增加,而流出Q38,39的基极电流减少,此时负载上的电流主要取决于流出Q31的发射极电流;若输入信号持续增加,Q31会截止,而Q30会进入饱和状态,Q30的电流会全部流进Q36,37,此时最大正向输出为:

当输入信号为负时则相反,其最大负向输出为:

研究可知,Q34、Q35管为Q31、Q32、Q36、Q37、Q38、Q39管提供保护,其工作原理为:当输出短路到VCC时,若输入信号为正时Q35启动,并将输入强行拉高到,防止Q31、Q38,39被反向击穿;若短路到Vee 时Q34启动,并将输入强行拉低到VEE +IC36R26+VBE34≈VEE +VBE34,防止Q32、Q36,37被反向击穿。 短路到地工作原理类似。

1.5 电路频率响应

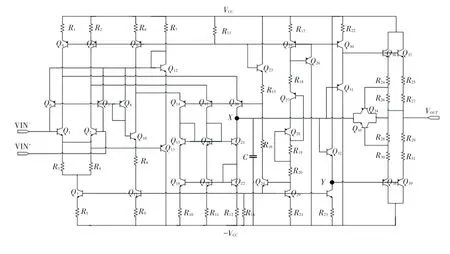

整体电路结构如图6 所示。 电路总电压增益近似为:

图6 整体电路结构Fig. 6 Overall circuit structure

X结点处等效电阻非常大,因此该结点处的寄生电容引入的极点就是主极点;在该结点处接上一个较大的电容降低主极点频率,实现主次极点分离,增大相位裕度,使系统更加稳定。 主极点可近似为:

其中,RX为输入级电路等效输出电阻,即为电压增益表达式后面的负载项;CX为该结点处的等效寄生电容。 整体电路压摆率约为:

考虑到输出级采用的是功率管,而功率管面积大,相应的寄生也很大,分析可知该点处的时间常数也会很大;因此经过仿真验证,电路次极点在结点Y处,该处的等效阻抗大约为1/ gm32,故次极点近似为:

其中,CY为该结点处的等效寄生电容。

2 性能仿真分析验证

本设计在Cadence 平台下使用Spectre 仿真器对电路进行仿真验证。 仿真条件为温度25 ℃(部分直流特性参数为全温范围)、电源电压±15 V、共模电压0 V、1 kΩ 负载电阻和10 pF 负载电容。

将运放接成电压跟随器的形式,通过改变补偿电容的大小观察其反向端大信号建立的速度,仿真结果如图7 所示。 可以看到当补偿电容在1p 以下时,其压摆率在938 V/μs 以上,补偿电容2p 时、为515.2 V/μs,补偿电容3p 时、为367.4 V/μs。

虽然补偿电容较小时,电路有很大的响应速度,但是其相位裕度也会很小,同样带入不同电容值观察电路相位裕度变化,仿真结果如图8 所示。 当补偿电容在1p 以下时,相位裕度在8.36 deg 以下,整个闭环系统极其不稳定;当补偿电容在3p 以上时,此时相位裕度在53 deg 以上,虽然电路系统此时很稳定,但响应速度也会呈倍数地降低。 因此最终做了一个折衷的选择,将补偿电容定在2.5p,此时相位裕度为46.66 deg,系统仅会有很小的减幅振荡,压摆率为428.1 V/μs,0.01%建立时间为42.3 ns。

补偿电容为2.5p 时,运放的开环频率响应特性仿真结果如图9 所示。 运放增益带宽积有365 MHz,即使得在高频时电路也具有短的建立时间。 因此本电路设计符合高速运放的特性。

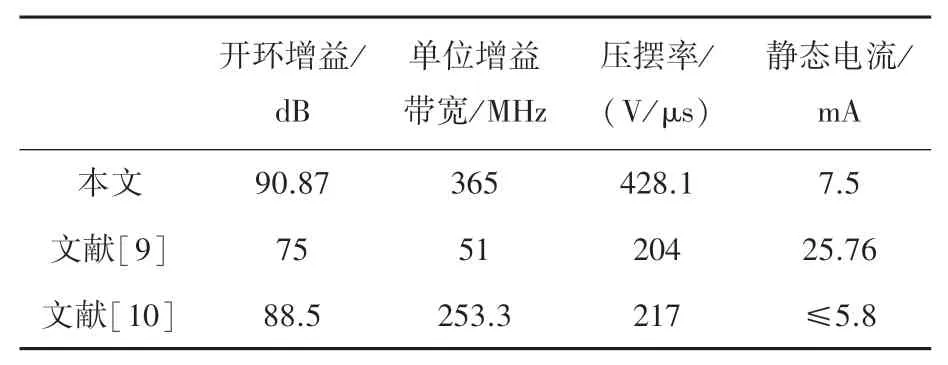

表1 给出了本设计的电路与其他文献电路的性能对比。 通过对比可以看出,本设计采用高速互补双极型工艺使得电路能够在较低的电流下获得较大的压摆率和带宽,有效降低了功耗;并且在保持电路性能参数不变的前提下,对晶体管面积做后续优化来降低寄生,则电路静态功耗可以进一步降低。

表1 本文电路与其他文献电路性能参数对比Tab. 1 Performance comparison of circuits between this paper and references

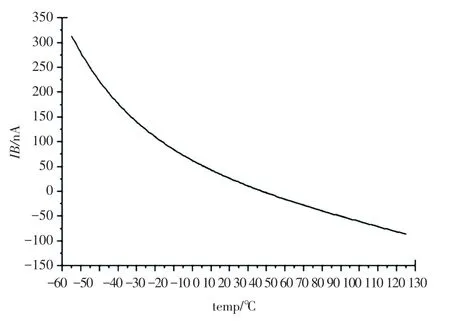

全温范围(-55 ℃~125 ℃)直流特性仿真结果如图10 所示。

图10 输入偏置电流仿真结果Fig. 10 Simulation of input bias current

三极管基极电流通常在μA 级别,由图10 看到基极补偿结构可以将输入偏置电流维持在nA 级别。 若对管采用超β 管或JFET 管,可将偏置电流降低至pA 级别;但超β 管在高频时会使电路不稳定,而JFET 管温度特性不好,在高温下反向饱和电流会剧增,可能会使输入偏置电流不减反增。 因此应视情况选用对管。

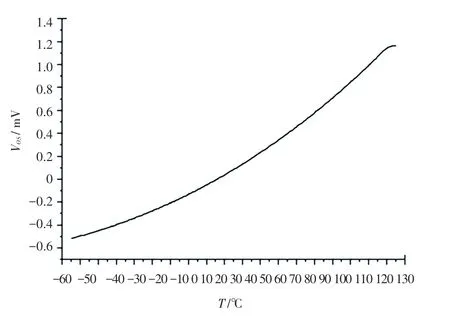

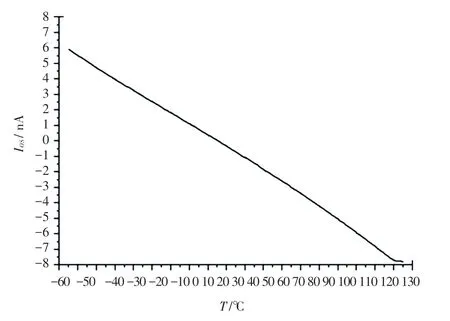

运放失调特性仿真结果如图11、图12 所示。输入级结构不具对称性;因为2 个共基管的电流不匹配,使得输入对管的电流不匹配,导致电路产生了系统失调。 虽然有源负载采用的是威尔逊结构,使得两管上的电流具有很高的对称性,但依然会存在一定的误差。假设Q19、Q22完全匹配,且IC19=IC22,则Q20集电极电流与Q17集电极电流的关系为:

图11 输入失调电压仿真结果Fig. 11 Simulation of input offset voltage

图12 输入失调电流仿真结果Fig. 12 Simulation of input offset current

上式可看出,纵使β匹配并且很大的情况下依然会存在很小的误差,且受到基区宽度调制效应的影响,Q21集电极电位和Q18集电极电位不同也会引入电流镜误差,因此结构仍会存在一定的系统失调。 其他重要性能参数见表2。

表2 部分性能参数Tab. 2 Partial performance parameters

3 结束语

本文基于高速互补双极工艺设计了一种高速运算放大器。 经仿真验证在±15 V,25 ℃,1 kΩ 负载电阻和10 pF 负载电容的条件下,得以运放开环增益90.87 dB,相位裕度46.66 deg,单位增益带宽接365 MHz,压摆率428.1 V/μs,0.01%精度建立时间为42.3 ns,静态电流7.5 mA,输入噪声电压1.026 nV/√Hz,通过采用基极电流补偿技术将运放输入偏置电流降到34.8 nA,满足高速运算放大器的要求。 该运放能够应用于有源滤波器、宽带放大器、ADC 驱动器、视频放大器、缓冲器等应用中。