硅衬底氮化镓大失配应力调控方法研究

2023-02-18王欢,田野

王 欢,田 野

(哈尔滨师范大学 物理与电子工程学院,哈尔滨 150025)

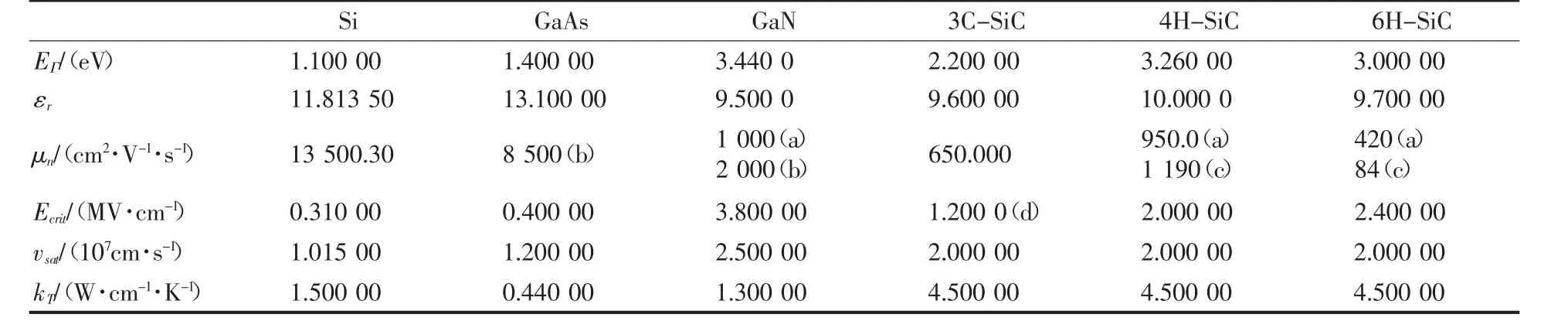

Ⅲ族氮化物,主要包括GaN、AlN、InN 及三元Al-GaN、GaInN、AlIn 和四元AlGaInN 合金材料。表1 为GaN 与其他几种半导体材料基本性能的比较。由于GaN 和AlGaN 的热导率较高,而且介电常数较低,适合制作小尺寸低功率中压至高压电力电子器件。且AlGaN/GaN 异质结处形成的二维电子气面密度高达1013cm-2以上,较其他半导体异质结的二维电子气(2DEG)面密度高近一个数量级,因此很适合制作微波高温、高功率器件,即用于卫星、空间站及空间太阳能电站耐辐照全光谱太阳能电池器件;此外,GaN 是宽禁带直接带隙半导体,又很适合于制作短波长光器件;另外,利用GaN 禁带宽,与AlN 和InN 形成三元或四元合金带隙调控范围超宽(0.7~6.2 eV)的特点,使得GaN适合研制可见光、紫外及近红外波段光电器件(LED、LD 探测器)。赤崎勇等教授获得了2014 年的诺贝尔物理学奖,因为研究的GaN 基蓝光LED 开启了人类新的照明市场。显然,作为第三代半导体材料代表的GaN已经成为当前最具产业开发价值的宽禁带半导体材料。而高质量、大尺寸GaN 材料的制备也就自然而然地成为了研究GaN 材料的前提和关键。

表1 GaN 与其他几种半导体材料基本性能的比较

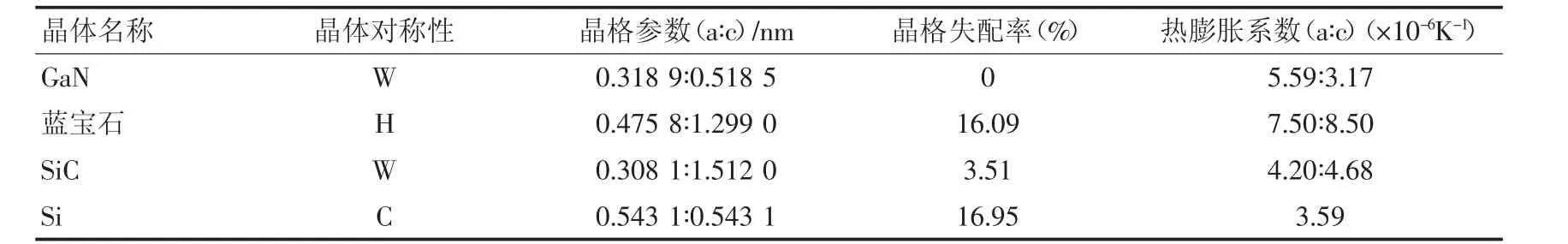

由于GaN 的熔点和饱和蒸汽压较高,大尺寸的块体GaN 非常不容易通过传统的制备技术来获得。就生长GaN 薄膜来说,GaN 单晶是最理想的衬底材料,其可以在很大程度上降低位错密度,从而提高外延材料的晶体质量,延长GaN 基器件的工作寿命,提高发光效率。但是大尺寸GaN 单晶衬底制备困难、成品率低,还不能规模化生产,由此造成了大尺寸GaN 单晶衬底材料价格昂贵且稀缺,因而利用同质外延生长GaN 薄膜更加难以实现。所以目前,GaN 的生长主要采用异质外延法,用于异质外延的衬底有蓝宝石衬底、碳化硅(SiC)衬底和Si 衬底。表2 为GaN 与常用衬底的各项参数。

表2 GaN 与常用衬底材料的参数

相较于蓝宝石衬底和SiC 衬底,Si 衬底具有很多优势:①Si 衬底的尺寸大且价格低廉(8 英寸Si 衬底仅需要300 元);②导热导电性能好(可制备垂直结构器件并缓解功率器件散热问题);③器件工艺成熟(可利用成熟硅微电子器件工艺,成本降幅可达75%)。GaN电子器件和Si(100)互补金属氧化物半导体(CMOS)电路的集成允许将Si 电路的高度复杂性和灵活性与GaN 支持的大量新设备相结合,如发光二级管(LED)、晶体管(HEMT)、能量收集设备和滤波器等。目前,Si 基GaN 材料被广泛研制于光电器件(激光器、探测器等)、射频微波器件(射频微波器件已开始在5G 无线通讯基站建设中应用)、功率电子器件(功率电子器件已在快充、节能家电及光伏发电逆变器大范围推广,并向汽车电子渗透)。

然而,以Si 为衬底异质外延GaN 是典型的大失配外延,需要面临以下问题:①表面界面能问题。当GaN生长在Si 衬底上时,Si 衬底表面会先氮化形成不利于高密度GaN 成核生长的非晶氮化硅层,而且Si 表面会先与Ga 接触,Ga 回熔会腐蚀Si 衬底表面,高温下Si表面分解会高度扩散进入GaN 外延层形成黑色硅斑。②GaN 和Si 之间晶格常数(~17%)失配较大,通常会导致高密度的穿线位错(TDD,通常为109~1010cm-2)和微裂纹网络的形成。③GaN 和Si 之间热膨胀系数的巨大失配(~54%),会使得GaN 从较高的生长温度(高于100 ℃)降至室温时,引入巨大的热应力,从而导致GaN外延层出现裂纹,一般当GaN 外延层的厚度大于1μm时就会发生开裂,严重限制了GaN 外延层的厚度,而制作LED 器件所需要的GaN 薄膜厚度通常要高于2μm。以上这些问题的出现严重限制了Si 基GaN 光学器件、射频微波器件和功率电子器件的发展。因此,如何改善Si 衬底上GaN 外延材料的质量,是Si 基GaN 器件研究的重点领域。

通过大量的文献调研,本文从3 个方面综述了Si 衬底GaN 大失配应力的调控方法:①缓冲层技术;②图形化衬底技术;③柔性衬底技术。最后,针对现有方法的优缺点,展望了Si 衬底GaN 大失配应力调控的主要优化方向。

1 缓冲层技术

缓冲层(buffer)技术,是目前解决异质外延体系中应力和缺陷问题应用最广的一类中间层技术。具有一定厚度的单层或多层结构的缓冲层,主要是通过阻止或抑制外延层中失配应变弛豫的方式来减少乃至消除材料体系中的位错和缺陷产生。现有的缓冲层可归纳为3 种:晶格匹配缓冲层、组分渐变缓冲层和应变超晶格缓冲层。

1.1 晶格匹配缓冲层

与衬底晶格常数较接近的缓冲层称为衬底匹配型晶格匹配缓冲层。这一类缓冲层通常适用于失配较小的异质外延体系,由于与衬底的晶格常数更为匹配,可以使衬底表面更加光滑平整,以提高后续的外延层质量。与外延层晶格常数较接近的缓冲层称为外延层匹配型晶格匹配缓冲层。这一类缓冲层通常适用于失配较大的异质外延体系,比如以Si 为衬底异质外延GaN,虽然与外延层的晶格常数更为匹配,可以为外延层提供更合适的晶格生长模板,但与衬底之间的失配度并不小于外延层与衬底之间的失配度,所以内部依旧有存在缺陷和位错的可能。但也正是因为这些位错和缺陷的存在,弛豫掉了一部分失配应变,进而提高了外延层的晶体质量。

2000 年,Krost 通过引入薄的低温AlN 夹层,在Si衬底获得了厚度为1.3 μm 的无裂纹GaN。2002 年,R.Armitage 利用分子束外延法(MBE 法)在Si 衬底生长200 nm 厚的HfN(与Si 晶格失配仅为0.02%)缓冲层,随后在Si(111)面和Si(001)面外延获得了厚度分别为1.2 μm 和1.0 μm 的无裂纹GaN,且外延薄膜表面几乎无应力。2011 年,利用多次插入低温AlN 夹层方法,获得了总厚度为14.3 μm 的无裂纹GaN 外延层。除此之外,ZnO、3C-SiC 也被用作Si 衬底GaN 异质外延时的缓冲层。

目前,在Si 衬底上生长GaN 应用最广的是AlN缓冲层,其优势在于:①AlN 可以阻挡Ga 和Si 的直接接触,降低了Ga 和Si 反应的可能性;②当AlN 作为缓冲层时,Si 衬底上GaN 的张应力会转变为压应力,可以大大减少GaN 外延层的裂纹;③AlN 在Si 衬底表面有较好的浸润性,很薄的AlN 即可在衬底表面形成连续性很好的展布,说明AlN/Si 的界面比AlN/真空的表面能小,非常适合作Si 衬底外延生长的缓冲层。因此关于AlN 作为缓冲层的研究比较深入,具体包括生长AlN 缓冲层的温度、预铺Al 的时间、厚度、TMAl 流量、Ⅴ/Ⅲ比对GaN 外延层的影响。

1.2 组分渐变缓冲层

组分渐变缓冲层是一种多层结构,每一单层的晶格常数可以从与衬底匹配逐渐过渡到与外延层相匹配,即衬底与外延层的晶格失配借以分布到各单层,达到降低或消除失配的目的。

2016 年,徐小青等借助AlN 缓冲层和多层AlxGa1-xN组分渐变缓冲层,在4 英寸Si 衬底上利用MOCVD(金属有机气相沉积)生长了1.25 μm 厚的GaN。实验结果表明:通过优化4 英寸Si 衬底GaN 制备生长温度和材料生长工艺,并降低AlGaN/GaN 异质结构中的O 和C杂质,将金属接触结构由正方形转变为十字形,HEMT器件的2DEG 迁移率实现了高度均匀性(标准偏差降至0.72%),并提升到了2 161.4 cm2/V/s,超越了生产成本高昂的SiC 衬底GaN HEMT 器件的性能,展现了微波射频技术的应用潜质。

同年,杨学林等利用MOCVD 在4 英寸p 型Si(111)衬底上外延生长出的AlxGa1-xN/GaN 异质结构,在室温下2DGE 提高至2 260 cm2/V/s。X 射线衍射(XRD)结果显示,其表面光滑且带有清晰的原子台阶,电流-电压(I-V)测试结果显示,其上的肖特基二极管显示出2×10-5A/cm2的超低反向泄漏电流密度和-30 V 的门偏压,在室温下的最大电子迁移率可达2 260 cm2/V/s。这表明AlN/AlxGa1-xN可以提高晶体的外延质量,而高质量的无裂纹表面可以显著改善AlGaN/GaN 异质结构的电学性能。

2019 年,孙钱等借助于精心设计的Al 成分阶梯梯度AlN/AlGaN 缓冲层,首次在Si 上获得了10 μm 厚的无裂纹连续GaN,其TDD 为5.8×107cm-2。外延得到的10 μm 厚GaN 层具有镜面和无裂纹表面,TDD 约为5.8×107cm-2,与阴极荧光光谱测试(CL)结果一致,此外,生长的GaN 外延层具有原子光滑的表面和清晰的台阶流动形态,在5 μm×5 μm 的面积上显示出0.21 nm的均方根(RMS)粗糙度。这为在Si 衬底上构建高性能的GaN 器件,如探测器、功率器件甚至激光二极管奠定了基础。

2020 年,Li Yue 等在4 英寸硅衬底上的制造了准垂直GaN 肖特基势垒二极管(SBD),I-V 特性曲线显示,所制备的SBD 在3 V 下具有1.6 kA/cm2的高通态电流密度,在-3 V 下具有10-7A/cm2的低反向电流密度,其通断电流比高达1010,接近于GaN 衬底上SBD的通断电流比。表明硅基GaN 上的垂直功率器件有望在低成本领域得到进一步应用。

1.3 应变超晶格缓冲层

在组分渐变缓冲层基础上发展而来的应变超晶格缓冲层技术,是在衬底上先生长一组单层很薄的应变超晶格层,应变超晶格会引入一个应力场,应力场与穿透位错相互作用后,能使位错线被弯曲或拆断而不能进入外延层中,其作用犹如一个位错过滤器,可以提高外延层的质量。

2001 年,E.Feltin 通过插入AlN/GaN 超晶格,在Si上生长了0.9~2.5 μm 厚的无裂纹GaN 层。2009 年,Susai Lawrence Selvaraj 利用7 μm 厚AlN/GaN 超晶格,在Si 上制备了2 μm 厚的无裂纹GaN 层。2015 年,Jie Su等通过在AlN/AlGaN 与GaN 之间插入50~100 个周期的AlN/GaN 超晶格,实现了在Si 上生长2 μm 厚的无裂纹GaN 层。

缓冲层技术被用来解决Si 衬底GaN 大失配异质外延体系的核心在于:①先在Si 衬底表面预沉积一层Al 可以解决Si 衬底被氮化以及被Ga 回熔腐蚀的现象,即Al 与NH3先反应形成的AlN 充当了GaN 在Si 衬底上生长过程中阻挡层的作用;②AlxGa1-xN 组分渐变缓冲层作为GaN 在Si 衬底上生长的应力调控层,通过引入压应力去补偿GaN 生长过程中的张应力;③超晶格缓冲层作为GaN 在Si 衬底上生长的缺陷抑制层,可以阻挡位错向上延伸。通过在Si 衬底上设计合理的缓冲层结构,不仅可以改善GaN 外延层的质量,还可以提高GaN 基器件的性能。

2 图形化衬底

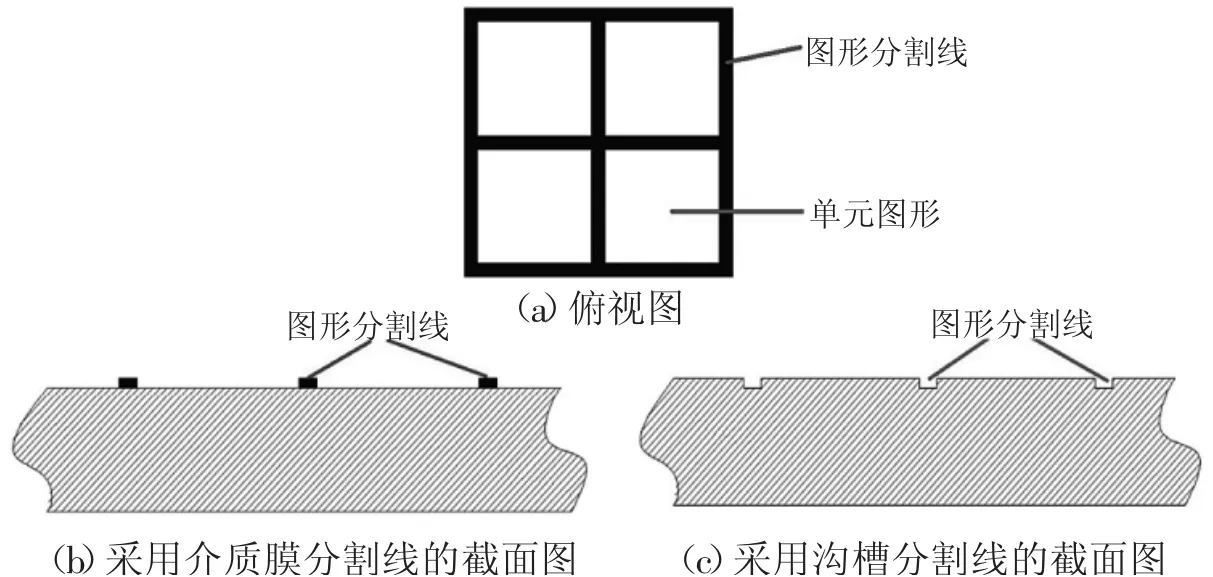

图形化衬底技术,是指利用特殊手段(多为刻蚀手段)将衬底材料进行分割,使得一块衬底材料被分割成具有周期性的小面积图形结构。衬底的图形化一般有2 种方式,一种是通过引入SiNx 或SiO2等介质膜,再利用光刻技术获得介质膜分割线,将衬底分割成周期性的小面积图形结构。另一种是利用物理或化学刻蚀的方法直接将衬底腐蚀出沟槽分割线,进而在衬底上形成周期性的小面积图形结构。如图1 所示。南昌大学江风益教授提出,于介质膜分割线,比较理想的尺寸为宽度5~8 μm,高度0.1~0.3 μm,沟槽分割线的理想尺寸为宽度10 μm 左右,深度15~20 μm。衬底材料被图形化处理后,外延GaN 薄膜会有选择性的先在衬底的部分区域进行生长,进而形成各个独立的GaN 生长板块,那么GaN 生长过程中的部分热应力就会在没有GaN 生长的区域进行释放,GaN 薄膜的裂纹也随着减少。另一方面,在图形化Si 衬底上进行GaN 外延,避免了因GaN 硬度大难以刻蚀的问题,可实现GaN 在MEMS(微机电系统)中的应用。

图1 图形Si 衬底示意图

2018 年,T. Hossian 等对图形化Si 衬底上厚GaN的裂纹进行了统计并对应力进行分析。研究发现:随着Si 衬底尺寸的增加,GaN 外延层内裂纹增加,应力也随之上升;图形间间隔高度的增加反而降低了GaN 层内的裂纹百分比,从而降低了其中应力;而图形间间隔的宽度对GaN 层内的裂纹没有显著影响。拉曼光谱(Raman)测试结果显示:对于12 μm 厚的GaN 薄膜,在结构中没有集中应力的缺陷的情况下,产生裂纹的临界应力约为1.8 GPa。

在图形化衬底思想的指导下,研究者们引入了选择性区域生长技术(SAG)和横向过外延生长技术(ELO)。

2017 年,Tanaka 等利用SAG 法在Si 上生长了19 μm厚、无裂纹且纯的GaN 层。在暴露的底层Si 表面上形成多面六角形盘,能够在Si 上生长超过18 μm 厚的GaN,并将TDD 密度降低到107cm-2。为了突出厚且无裂纹的低TDD 硅上GaN 的潜力,以19 μm 厚的GaN为漂移层制作了金属绝缘体半导体场效应晶体管(MISFT),结果表明可以在Si 上制造MISFT,并为在硅CMOS 平台上集成垂直GaN 功率和光电器件铺平道路。

图形化硅衬底生长GaN 薄膜的应力控制主要源于2 个方面:一是通过图形化生长减小GaN 膜的应变,单元图形尺寸越小,则张应力降低的幅度越大;二是通过应力补偿技术来进一步减小GaN 膜的张应力。图形化衬底技术对于GaN 基器件十分重要。

3 柔性衬底

柔性衬底技术也称作可协变中间层技术,是20 世纪90 年代初在缓冲层技术的基础上发展而来的一类新中间层技术。其指导思想完全不同于传统的缓冲层,是通过一薄层材料的弹性形变来吸收或释放体系中的失配应变,从而减少乃至消除界面处或外延层内部位错和缺陷产生。

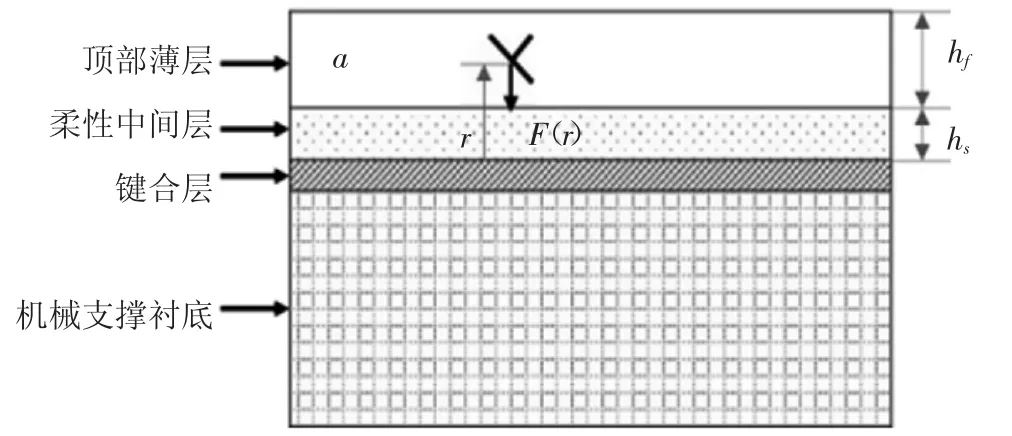

由图2 可知,氧化物键合的SOI 衬底是由“顶层薄Si—SiO2绝缘埋氧层—底层Si”组成的三明治结构Si衬底材料。SOI 衬底的制备工艺相对简单,是将具有高能量的大量氧离子利用工艺成熟的注氧技术注入到Si基体中,通过控制注入氧离子的剂量可以达到调控键和强度的目的。1997 年,J.Cao 提出“滑移理论”,阐释了SOI 衬底能提高GaN 外延层质量的原因。在大失配外延体系中,外延薄膜最初以三维(3D)岛状的模式生长,然后小岛之间合并,逐渐形成连续的二维薄膜,在合并处极易形成会穿透整个外延层的穿透位错。SOI衬底由于顶层薄Si 的存在,外延层与衬底间的作用力较小,使得外延小岛可以在顶层Si 表面自由滑动,可以在某种程度上减少小岛在合并过程中所形成的位错,提高外延GaN 的晶体质量。

图2 柔性衬底示意图

2019 年Roy Dagher 等将SOI 衬底图案化为纳米柱,并在其上得到了无裂纹、完全松弛的GaN,位错密度为4×108cm-2。以纳米级柱状图案为衬底增强了衬底与外延层间的柔顺性,可以更好地释放位错,为降低GaN 的应变、TDD 及实现GaN 器件的转移提供了新的思路。

2020 年,浙江大学宋钰姿制备了一种降低GaN 外延层热应力的新结构——SOI 表面悬浮超薄Si 膜。通过有限元方法模拟了新型结构上GaN 层在冷却过程中的热应力分布,模拟结果显示这种新型衬底上GaN有效区域的热应力可降低44%,进而降低了GaN 中的位错和裂纹密度,还证实了埋氧层的缺失是导致GaN层热应力降低的主要因素。

现有的柔性衬底已经在一些典型的失配外延体系中发挥重要作用,尤其是基于SOI 的器件具有集成度高、可靠性好和功能完善等优点,因此SOI 衬底在MEMS中得到广泛的应用;另一方面,以“滑移理论”为支撑的SOI 衬底可提高GaN 外延层的质量,给予研究者新的灵感——实现柔性层与支撑衬底的弱键合或解耦合,可以更大程度上弛豫外延层的应力,降低外延层的位错密度。

4 结束语

迄今为止,GaN 基器件已经取得了巨大的进步,但是GaN/Si 异质结构的材料质量和电学性质与已经比较成熟的蓝宝石、SiC 衬底上异质结构相比,依然存在明显差距,特别是Si 衬底上GaN 外延片上可见的残余应力、局域陷阱态及其带来的材料、器件可靠性问题还相当严重,应力和缺陷控制问题尚没有根本解决。如何研究制备出更高质量的Si 衬底上GaN 基异质结构,依然是当前该领域高度关注的核心问题之一。Si 衬底上GaN 材料大失配外延制备技术仍处于发展中。在解决Si 衬底GaN 异质外延大失配体系中存在的问题时,缓冲层技术操作复杂,工艺繁琐,未消除的残余应力在下一步外延中还会引入新的位错;图形化衬底技术的制备过程存在着步骤复杂、对设备要求高、价格高昂和大面积图案化制备的成功率低等问题;柔性衬底技术在实现柔性层与支撑衬底的弱键合或解耦合过程中还存在一些不足和技术局限性,并且高品质的SOI 衬底价格并不便宜,要达到广泛应用和推广,还需不断地发展,并解决现存的技术问题。

未来在解决Si 衬底GaN 异质外延大失配应力的相关问题,一方面将借鉴以蓝宝石、SiC 等为衬底异质外延GaN 的成熟工艺,另一方面,衬底与外延层之间的弱键合将成为解决大失配体系中应力问题的重要手段。随着Si 基GaN 无裂纹厚度的增加以及位错密度的降低,Si 基GaN 会突破以蓝宝石为衬底外延GaN 在尺寸和成本上的限制,Si 基GaN 晶圆在LED 市场的份额会逐年增加,Si 基GaN 晶圆质量会更加符合严格的CMOS 工艺标准;Si 衬底GaN 材料研制的HEMT 微波射频器件的性能可以达到甚至超过SiC 上GaN HEMT微波射频器件性能;实现Si 衬底GaN 功率电子器件对传统中低压硅基功率电子器件的替代。