基于版图设计的DICE触发器单粒子翻转加固技术

2023-01-11赖晓玲张健巨艇朱启郭阳明

赖晓玲,张健,巨艇,朱启,郭阳明

(1.西北工业大学 计算机学院,陕西 西安 710072;2.中国空间技术研究院西安分院,陕西 西安 710199)

随着我国航天事业快速发展,宇航级专用集成电路(application specific integrated circuit,ASIC)芯片的规模、功能复杂度及工作频率不断上升,芯片中D触发器的数量越来越多。同时随着集成电路制造工艺不断发展,芯片工艺尺寸不断减小,内核工作电压不断降低,导致D触发器的单粒子翻转(single event upset,SEU)阈值越来越小[1-2],使得D触发器的SEU已成为纳米级数字集成电路发生单粒子软错误(soft error rate,SER)的主要原因之一。

D触发器的设计加固技术主要分为两类:在ASIC前端设计阶段的三模冗余(triple modular redundancy,TMR)电路设计加固技术,以及标准单元库设计阶段的双互锁存单元(dual interlocked storage cell,DICE)触发器设计加固技术。

TMR加固技术包括空间三模冗余(spatial TMR,STMR)和时间三模冗余(temporal TMR,TTMR),其中TTMR防护能力最优,但功耗、面积、时序等开销极大[3],且该技术对冗余触发器的物理位置以及电路的刷新频率要求较高[4]。这与ASIC高性能、低功耗等设计目标相矛盾。而通过开发单元库级的抗SEU加固D触发器可最大限度地减小ASIC性能开销。但在纳米级工艺下,电荷共享引起的多节点翻转(single event multiple upset,SEMU)现象越发严重[5],传统DICE触发器设计方法抗SEU的能力已不能满足宇航需求。研究表明,基于40 nm体硅工艺未做版图优化的DICE触发器,其抗SEU能力仅为同工艺下商用触发器的1.4倍[6]。基于此,近年来,针对纳米级D触发器的单元级加固方法是通过DICE结构与版图设计相结合实现的,如版图重排技术(layout design through error-aware transistor positioning,LEAP)、Double-Height-Cell技术等[3,7],其基本原理都是通过增加锁存器中敏感节点的物理距离,提升SEU防护效果。同时在先进工艺下,特殊工艺与版图设计相结合的DICE触发器也是纳米级触发器加固的有效手段,如在22 nm工艺下,基于超薄体区超薄埋氧(ultra-thin body and buried oxide,UTBB)的全耗尽型绝缘层上硅(fully depleted silicon on insulator,FDSOI)工艺实现的DICE触发器就表现出优秀的SEU防护效果[8]。

如何在减小功耗、面积、时序等资源开销的同时保证电路的抗辐照能力、缩短芯片研制周期及压缩研制成本,是当前宇航ASIC设计面临的重要挑战,而如何在提高D触发器抗SEU能力的同时降低面积和时序等开销是解决该问题的关键。目前,国内外针对纳米工艺下DICE触发器的研究较多,但并未做到兼顾抗辐照能力和面积开销。如西安微电子技术研究所李海松等[3]基于65 nm体硅工艺设计了相关敏感节点远离DICE触发器,该触发器面积为普通触发器面积的2.3倍,但实验结果显示,其SEU的LET阈值小于20 MeV·cm2/mg[3]。Fuma等[7]基于65 nm体硅工艺,提出一种通过版图布局优化来提高抗SEU能力的DICE触发器设计方法,该方法以增大触发器面开销为代价,相较于普通DICE触发器,额外增加了46%的面积。Cai等[8]提出多种基于22 nm UTBB FDSOI工艺的DICE触发器设计方法,SEU阈值可大于37 MeV·cm2/mg,该工艺由于超薄的体区及埋氧层的存在,相较与体硅工艺,天然具有很强的耐多节点翻转能力[8],使得DICE触发器的版图级加固设计相对简单,但流片费用十分昂贵。本文通过研究商用65 nm工艺下D触发器的空间SEU发生机理和DICE触发器版图设计技术,从单粒子瞬态脉冲产生及缓解机理出发,结合触发器的工作原理,同时兼顾了面积开销、抗辐照能力、流片成本,在不额外增加DICE触发器面积的前提下,提出了一种资源开销低的DICE触发器抗SEU版图设计方法。基于该方法设计的触发器资源开销低、电路性能和抗辐照能力表现优秀,在抗辐照ASIC设计中,可极大节省对时序电路SEU加固所带来的面积、功耗和时序开销,且无需引入额外的EDA设计流程,缩短芯片研制周期。

1 DICE触发器的版图加固技术

DICE锁存器由4个首尾相连的反相器构成,其中存储节点分别与前一级NMOS和后一级PMOS相连接,使得正负存储数据均被冗余保存,因此单个存储节点发生翻转时,冗余电路通过反馈将其修正,并不会引发SEU;当粒子入射沉积的能量足够大时,能够导致2个存储相同逻辑的存储单元同时翻转,DICE触发器才会发生翻转,因此DICE锁存器具有很好的抗粒子电离扰动能力[9]。然而由于一些本质的翻转机制,DICE触发器的SEU翻转截面并非为零[10]。

1.1 DICE锁存结构SEU发生机理分析

多个高能粒子同时击中DICE锁存器单元的不同敏感节点的概率非常小,但大量研究表明在深亚微米到纳米级工艺下,DICE结构的抗SEU能力并不十分理想,这是因为单个高能粒子入射引起SEMU所导致的,具体发生机理如图1所示。

图1 4种能够引起双互锁存储单元发生单粒子翻转的典型事件

1) 高能粒子入射锁存单元,当入射角度与垂直平面夹角较大时(通常在45°~60°之间),粒子可斜穿过2个存储相同逻辑的敏感节点,当入射粒子有足够线性传输能导致这些敏感节点发生翻转,便发生存储单元SEU。图1a)为线性传输能(linear energy transfer,LET)阈值约为37 MeV·cm2/mg的Ge粒子以60°角入射65 nm体硅互补金属氧化物半导体(complementary metal oxide semiconductor,CMOS)工艺的DICE锁存单元,这一情况便会导致此类SEU发生。

2) 高能粒子垂直入射(或较小角度斜入射)锁存器单元,并在MOS管附近与质量较高的靶原子发生弹性碰撞(卢瑟福散射),导致其运动轨迹发生较大偏转,从而穿过2个存储相同逻辑的敏感节点。如图1b)所示,垂直入射的Ge粒子在PMOS有源区附近与连接孔(W材料原子)碰撞,使得入射的Ge离子发生大角度偏转后斜穿过2个敏感节点。

3) 高能粒子垂直入射(或较小角度斜入射)锁存单元,并在MOS管附近与质量相近的靶原子发生弹性碰撞,导致粒子运动轨迹发生大角度偏转,同时被击中的靶原子产生一个电离核子反冲出去。这相当于2个不同的高能粒子以不同轨迹入射锁存单元,同时击中DICE锁存单元的不同敏感节点的情况,导致DICE触发器发生SEU。如图1c)所示,Cl离子击中O原子发生散射,Cl离子和O离子分别穿过一个敏感节点。

4) 高能粒子入射锁存单元,并在MOS管附近与原子发生核反应,产生多种能量较高的次级粒子,引起多个敏感节点发生翻转,导致SEU。如图1d)所示,粒子能量为14 MeV的高能中子,垂直入射存储单元的PMOS有源区,并与Si原子发生核反应,产生Mg、α、γ等多个高能次级粒子斜穿过多个敏感节点导致存储单元发生SEU。

粒子散射、核反应等物理机制导致不同种类但LET阈值相近的粒子,SEU截面甚至相差达2个数量级,在纳米工艺下,LET小于10 MeV·cm2/mg的高能粒子,仍可使DICE锁存器结构发生SEU[11-12]。每种翻转机制的发生概率都会随着敏感节点间距的增大而减小,提高DICE锁存器抗SEU的最有效方法是增加一对存储相同逻辑的敏感节点的物理距离。有资料显示,存储相同逻辑敏感节点间距增大1倍,DICE锁存器的SEU可降低10倍[13]。

DICE触发器由主从2个锁存器构成,传统的版图设计方法如图2a)所示,存储相同逻辑的敏感节点距离较近,随着供电电压、节点电容、敏感节点距离减小,深亚微米工艺下DICE结构触发器的防护效果已经不理想。图2b)是波音(Boeing)公司设计的一款90 nm商用CMOS工艺的DICE DFF版图[11],通过增加敏感节点距离和增加阱接触的方式提高触发器的抗SEU能力,然而这带来了较大的面积浪费。

图2 2种常用的DICE触发器图设计方法

1.2 加固措施及版图设计

从DFF的工作原理分析,每半个时钟周期只有一个锁存器环路导通,因此如果高能粒子入射引起翻转的2个存储节点分别在主锁存器和从锁存器中,不会导致DICE触发器发生SEU。基于以上分析,在不浪费版图面积开销的同时,可以参照静态随机存储器(static random access memory,SRAM)的位交错技术设计思路[4],将锁存器中每个敏感节等效看做1个bit位,通过主从锁存器各敏感节点交错布局实现DICE触发器的版图设计,理论上很小的面积开销便可使敏感节点的物理距离增加1倍以上。但是随着集成电路工艺进入纳米级,电荷共享效应的影响增强,仅依靠位交错技术已不能很好地满足DICE触发器的宇航抗SEU指标需求。因此,除了通过位交错技术增大敏感节点之间的距离外,本设计还采取多节点电荷分享的版图设计加固技术[13-14],具体原理如图3a)所示。当高能粒子轰击反相器的关态PMOS时产生电子-空穴对,由于该PMOS的漏极为低电平,源级接VDD,电荷漂移效应及寄生双级放大效应使得PMOS的漏极产生向上的SET脉冲,但开态PMOS在电场作用下会吸收过剩电子,减少高能粒子入射引起的存储节点SET的脉冲高度和宽度,进而减小SEU发生几率。因此减小DICE锁存器一对存储相反逻辑MOS管漏极距离,从而使输出节点的关态PMOS总电荷收集减少也是提高触发器抗SEU能力的有效方法,具体原理如图3b)所示。当高能粒子入射关态PMOS管时产生电子-空穴对,过剩电子的浓度决定寄生PNP管的开关状态,但这部分电子会受电场作用被开态PMOS漏极吸收,吸收能力随漏极距离的减小而增大,从而减小输出节点的关态PMOS管由于双极放大效应收集的正电荷量。基于以上分析,文献[13]公开了一种LEAP DICE的版图布局方案,如图3c)所示。该方案很好地实现了开态MOS与关态MOS之间的电荷分享,且对高能粒子同时穿过多个敏感节点的轨迹要求变得十分苛刻,具有很强的抗SEU能力,但基于该方法实现的DFF不仅面积较传统的DICE DFF增加约40%,且PMOS有源区与NMOS有源区的交错布局使得电源地轨道不连续,极大地增加了DFF单元版图的绕线难度和芯片后端设计的复杂性,因此需对该方案进行改进。

图3 版图重排布加固技术分析

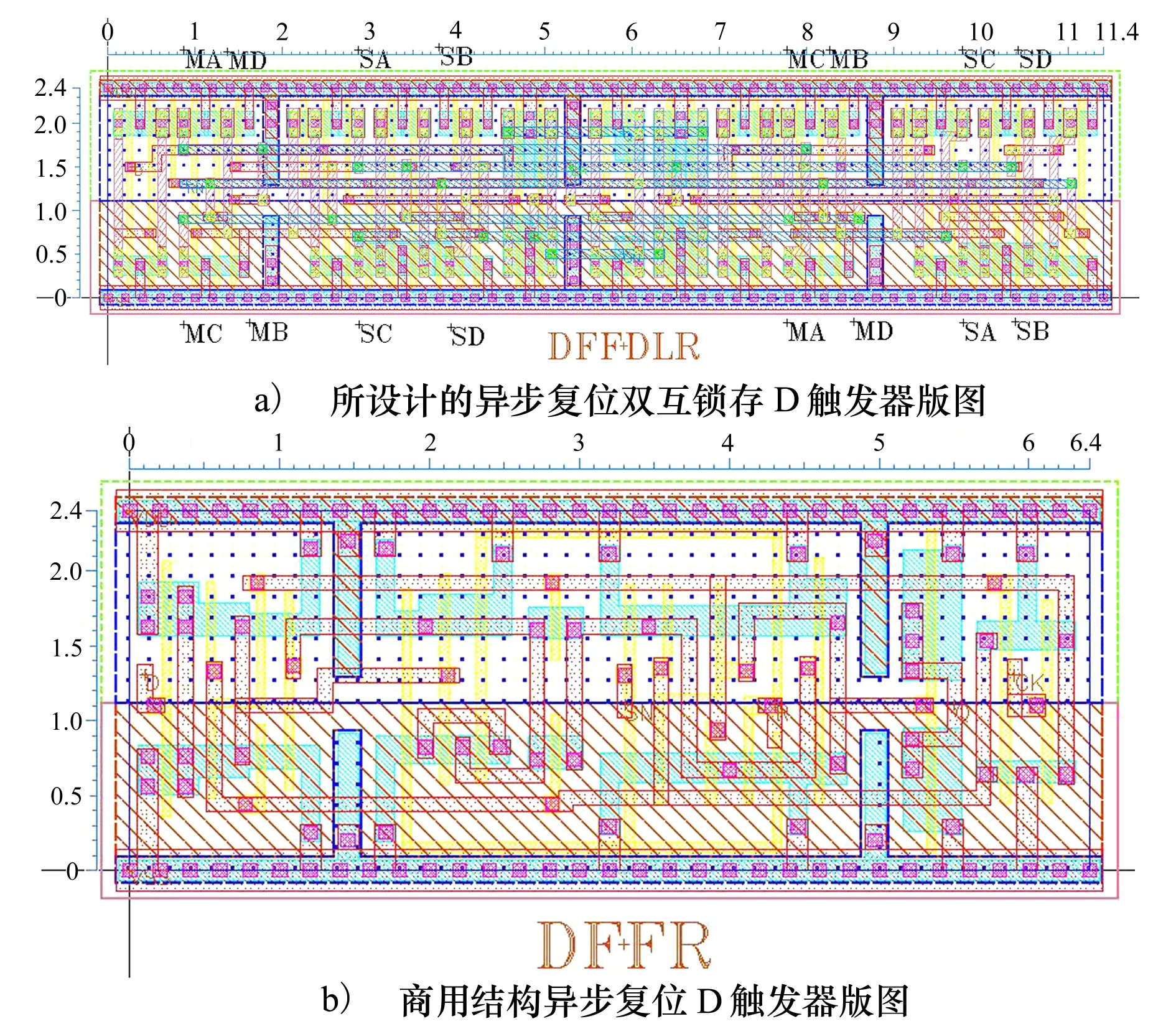

本文以传统的DICE触发器电路结构为基础,在版图设计时进行如下布局:①将同一锁存器中存储相异逻辑的同类型MOS管漏极贴近摆放,以实现减小一对存储相反逻辑MOS管漏极距离的目的;②由于DICE锁存器的逻辑备份电路结构,将同一锁存器中存储相同逻辑的不同节点、不同类型MOS管贴近摆放,以实现LEAP技术;③将同一锁存器中存储相同逻辑的相同节点、不同类型MOS管拉开距离,通过较长的金属走线来增加节点电容,以提高节点抗SEU能力;④将同一锁存器中存储相同逻辑的不同节点、同类型MOS管使用位交错技术布局,增加DICE锁存器敏感节点的间距;⑤将触发器中的输入驱动电路、输出驱动电路以及时钟驱动电路放在触发器版图中间以增大一对敏感节点距离;⑥使用保护带阱接触并在保护带上多打接触孔,增加阱接触,减小阱电阻。通过以上原则,实现DICE触发器版图设计,整体版图如图4a)所示,其中MA、MB、MC、MD是DICE触发器中主锁存器的4个存储节点,SA、SB、SC、SD是DICE触发器中从锁存器的4个存储节点,版图上半部分是PMOS,下半部分是NMOS,阱接触保护带间距小于4 μm,每对敏感节点的距离远远大于3 μm[15],触发器版图通过2层金属实现,整体面积为11.4 μm×2.4 μm,仅为同类型商用结构触发器(见图4b))面积的1.8倍。

图4 2种触发器版图面积对比

2 仿真验证

为验证所设计触发器的可靠性及性能,需对所设计版图分别进行抗SEU能力仿真和功能后仿真。

2.1 DICE触发器的SEU仿真

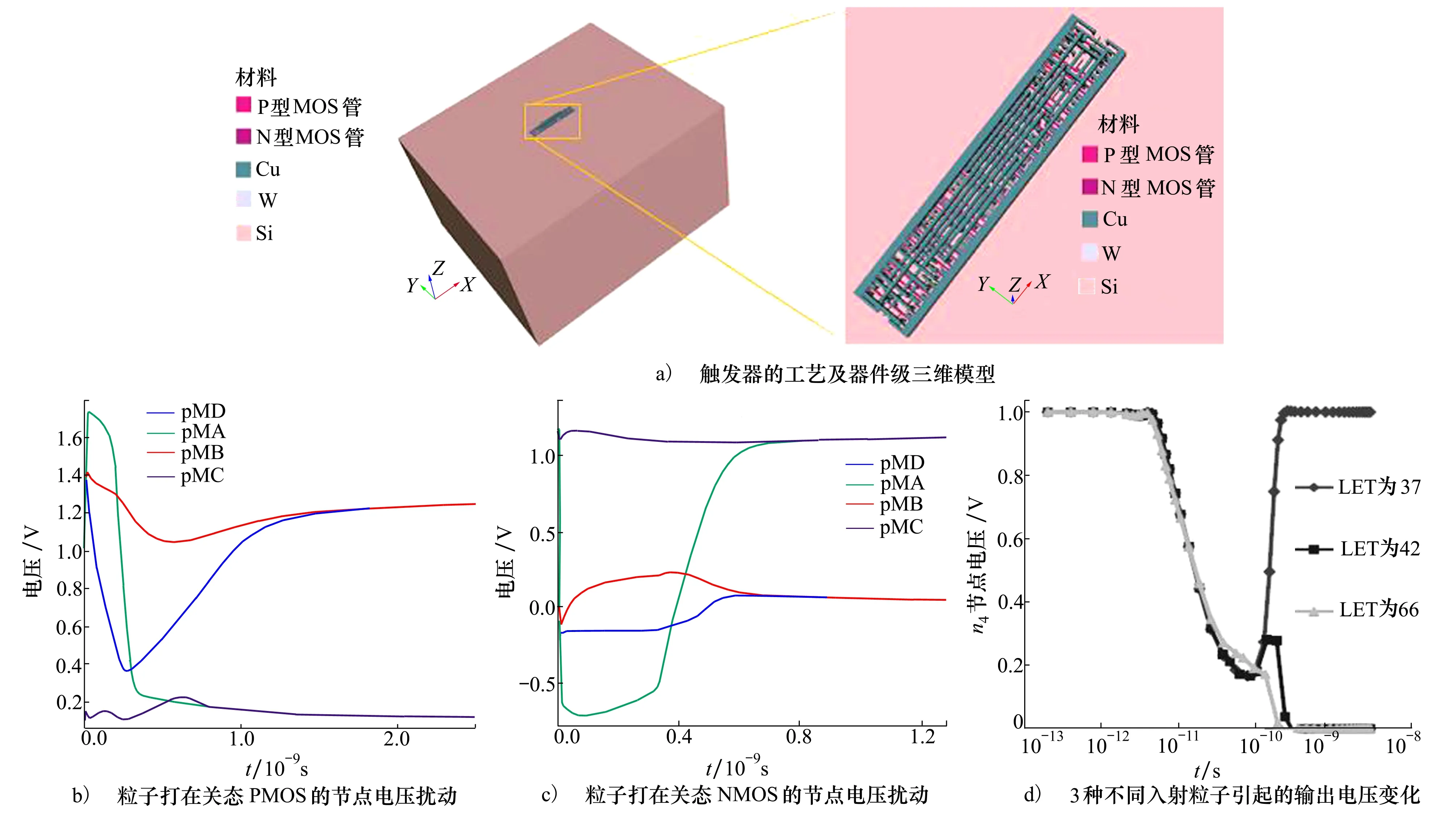

使用65 nm商用工艺的器件模型对本文设计的DICE触发器进行半导体工艺及器件级建模(technology computer aided design,TCAD),三维模型如图5a)所示。

图5 所设计基于版图重排布加固技术的双互锁存D触发器的器件级仿真分析

X方向为版图高度(2.4 μm),Y方向为版图宽度(11.4 μm),Z方向为单元从衬底到金属2的方向。在触发器工作电压为1.0 V条件下,使用Ge离子(LET值约为37 MeV·cm2/mg)以60°倾角分别入射DICE触发器中主锁存器的关态PMOS与关态NMOS,主锁存器节点波形的扰动如图5b)~5c)所示,从仿真波形看节点出现较大SET扰动,但未发生SEU;但用LET值分别为42和66 MeV·cm2/mg的Br粒子和I粒子入射本设计,触发器发生SEU,输出电压的变化如图5d)所示。从仿真结果分析,所设计的DICE触发器抗SEU能力表现优秀,SEU阈值可达37 MeV·cm2/mg。

2.2 DICE触发器的功能后仿真

采用Calibre的PEX提取寄生参数,采用spectre进行后仿真,条件为最慢工艺角(供电电压1.08 V、工作温度125℃、最慢工艺)。本设计的DICE触发器后仿真验证结果为:触发器功能正确,建立时间160 ps,上升传输延迟202 ps,复位建立时间183 ps,时序开销与普通商用触发器相当。

3 结 论

本文以DICE触发器电路为基础,在版图设计中,分析DICE电路结构的SEU发生及防护机理,通过位交错技术、LAEP技术、双极效应防护技术相结合的方法,合理设计单元版图布局,提高单元抗SEU能力。基于本文方法设计的DICE触发器面积仅为同工艺、同类型商用触发器的1.8倍,抗SEU能力和电路性能优秀,端口定义、数量及逻辑功能与商用结构D触发器完全一致,因而使用本设计触发器进行宇航ASIC芯片研制时,无需额外的EDA设计流程对D触发器进行加固,提高了芯片研制效率,并极大节省了由于对D触发器电路进行加固所带来的面积、布线资源和时序开销。