超导纳米线三端子器件研究和应用进展

2023-01-09黄洋辉赵清源涂学凑张蜡宝贾小氢吴培亨

黄洋辉,赵清源,*,涂学凑,张蜡宝,贾小氢,康 琳,陈 健,吴培亨

(1.超导电子学研究所,南京大学,南京 210023;2. 南京大学 电子科学与工程学院,南京 210023)

0 引言

依托半导体制造技术的数字电路已经在生活各方面产生了重要影响,其发展历程经历了电子管、晶体管和大规模集成电路三个阶段。基于超导材料的数字电路技术,虽然面临低温环境的制约,但作为一类独特且性能突出的数字电路技术,同样经历了三个阶段[1]。第一阶段始于1956年,Dudley Buck以两根缠绕在一起的超导线构成冷子管(cryotron)[2],此后基于该冷子管构建的触发器、存储器、模数转换器等数字电路的基本单元被提出。第二阶段以IBM为代表的研究机构发展了基于约瑟夫森效应的锁存逻辑电路,利用更小的控制电流驱动约瑟夫森结。该逻辑电路最大的特点为电路每次进行逻辑操作后都需要断电回到零电压态,因此工作速度迟迟没能超出1 GHz。第三阶段是以快速单磁通量子电路(RSFQ)[3]为代表的数字逻辑电路,与锁存逻辑相比,RSFQ电路由直流供电,具备更快的工作速度,因此得到了大力发展。目前超导数字电路以RSFQ为基本设计单元,但是RSFQ也存在不足的地方,例如,输入阻抗低、驱动能力不足、无法同高速存储器进行集成。这也是美国超导计算机研究计划(C3)需要解决的问题之一[4]。

2014年,McCaughan和Berggren教授在cryotron的基础上提出了一种新型的平面结构超导纳米线三端子器件(Superconducting nanowire cryotron,简称nTron)[5]。相比传统的约瑟夫森结,nTron具有以下的基本特性:(1)核心尺寸更小,仅为百纳米左右;(2)单层器件结构,与其他功能器件更容易进行混合集成;(3)驱动能力强,失超后的电阻达数千欧姆,能够驱动多个后级电路或半导体晶体管等。这些特性使得其在超导数字电路领域受到关注。此后,nTron又衍生出hTron[6]、yTron[7]等超导纳米线低温三端子器件。目前,国际上也有多个研究小组开展了相关研究,其中国外单位包括:MIT(USA)、NIST(USA)等,国内单位主要有:南京大学和天津大学等。随着研究的深入,nTron及其相关器件和电路也从超导数字电路走向了更广的领域。本文主要介绍了三种超导纳米线三端子器件的结构和工作原理,并且综述了最近几年超导纳米线三端子器件的研究和应用进展。

需要一提的是,cryotron最早被翻译为“冷子管”,我们可查到的最早翻译来源于1960年《电子计算机动态杂志》期刊[8]。根据目前的相关进展,Superconducting nanowire cryotron所衍生出的是一系列的三端子器件,通过门控端输入控制信号改变局部区域的电流、温度、磁场等,实现对通道端纳米线超导特性的调控,是一种典型的由电信号控制的器件。这也是这类器件区分约瑟夫森结的重要特点之一,和Dudley Buck提出的cryotron器件在工作原理上也有不同之处。“冷子管”这个几乎被人遗忘的名字,已经不能再反映现阶段超导纳米线这种器件的优势。因此,本文中将此类器件统称为“超导纳米线三端子器件”。具体到某种器件时,我们以他们的英文缩写:nTron、yTron和hTron来命名。这也符合McCaughan和Berggren在原作中的定义(A three-terminal electrothermal device)。至于cryotron的直译,我们还是依据国家标准,译为“冷子管”。

1 nanowire cryotron(nTron)

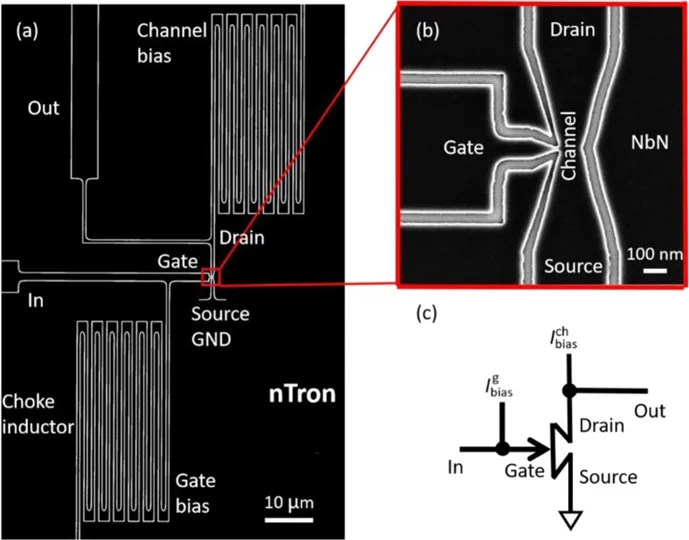

典型的nTron通常为三端子结构,属于单层器件。图1为MIT的研究人员所制备的nTron器件,由两段单根纳米线(门控端和通道端)构成,电路符号见图1(a)。两者的电气连接处为一段宽度约为几十纳米的纳米线结构,通道端通常为数百纳米左右宽的单根纳米线(图1(b))。其工作原理为:将nTron的通道端偏置在低于临界电流的条件下,当门控端没有电流脉冲输入时,通道端依旧处于超导态,当流经门控端的电流脉冲大于其临界电流时,将在门端的纳米线局部区域产生一块处于正常态的热点“Hotspot”区域(图1(d))。随着热点的不断扩大,将导致热点附近的局部温度升高,压缩通道端纳米线的临界电流,使整个通道端变为正常态,输出电阻可达数千欧姆,实现门控端输入电流信号对通道端超导态转化至正常态的控制。

图1 (a)nTron的电路符号;(b)nTron的SEM图;(c)nTron的输出特性;(d)模拟nTron的三个工作过程[5]Fig. 1 (a) Simplified circuit schematic of the nTron; (b) Scanning electron micrograph of an nTron; (c) Circuit schematic and output characteristics for an nTron; (d) Numerical simulation of the nTron depicting the three states of operation [5]

热点的大小取决于输入门控端的电流和通道端的偏置电流大小,当热点产生后偏置电流将输出至负载端,实现一次开关过程。若门控端输入电流小于门控端纳米线的临界电流,但是和通道端的电流叠加超过通道端的临界电流,同样能够触发并产生稳定的热点区域,此时nTron将工作在电流叠加模式下。

因此,nTron的触发模式主要分为两种,一种为门控端电流触发模式下的局部热扩散导致的失超过程,一种为电流叠加模式下的失超过程。两种触发模式下的工作过程可借鉴纳米线热传导模型[9-10]和电路模型[11-12]进行SPICE仿真;或者从nTron的结构出发,利用“T”型结构[13],结合时间相关的金茨堡-朗道方程以及热扩散方程进行数值拟合。nTron可工作在自恢复(self-reset)模式和锁存(latched)模式下,若要将nTron工作在自恢复模式下,通常会在通道端串联电感以减缓电流恢复时间,同时在偏置端外加直流偏置;若要将nTron工作在锁存模式下,需要在通道端加脉宽偏置信号,此时器件能够工作在较高的速度下。

nTron工作场景的不同,所关注的基础特性也有所不同。为了能够更详细地对nTron的基础特性进行表征[14-15],南京大学赵清源课题组开展了相关的研究工作,从nTron的工作速度、时间抖动、工作区间、功耗等方面对该器件进行了详细表征。在实际应用中,上述几项指标往往相互制约,共同影响nTron工作性能。例如更大的门控端输入信号会有更低的时间抖动,但需要更长的热耗散时间,这限制了nTron追求更快的工作速度。图2为该课题组制备的nTron器件结构图片和器件的电路符号,通道端和电感串联,输出端则位于两者之间,目的是提高nTron的工作速度同时减少失超后电流串扰现象,实验中测量到的最大工作速度为615.4 MHz,单个nTron的最低功耗为19.7 nW左右。

图2 (a)nTron的SEM图;(b)nTron的局部放大;(c)nTron的电路符号[15]Fig. 2 (a) Scanning electron micrograph of an nTron; (b) An enlarged view of an nTron; (c) Simplified circuit schematic of the nTron [15]

2 heater cryotron (hTron)

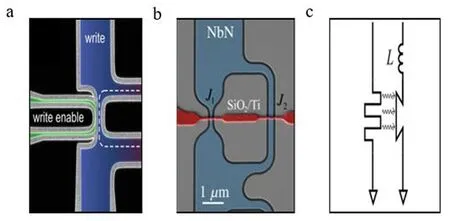

hTron是研究人员在nTron的基础上提出的另一种电热型超导纳米线三端子器件,hTron的端口命名和nTron的命名方式一致。两者的区别在于,nTron利用门控端对通道端直接注入电流控制超导相变;而hTron则利用门控端的热效应引起温度升高来压缩通道端纳米线的超导临界电流,门控端与通道端之间无直接的电气连接。在结构上,hTron主要有平面型[6]和立体型[16]两种。平面型结构(图3(a))通常采用两根相同的超导纳米线构成,纳米线之间为30 nm左右的间隔。立体型(图3(b))为三层结构,上层通常为金属材料,位于通道端中央的正上方;中间为一层约30 nm厚的二氧化硅绝缘层,下层则为一根超导纳米线构成的通道端。图3(c)为hTron的电路符号,左侧符号为门控端,右侧符号为通道端。

图3 (a)平面型hTron的SEM图[6];(b)立体型hTron构建的SEM图[16];(c)hTron的电路符号[16]Fig. 3 (a) Scanning electron micrograph of an in-plane hTron [6]; (b) Scanning electron micrograph of a stereoscopic hTron [16]; (c) Simplified circuit schematic of the hTron [16]

hTron工作原理为:将通道端偏置在低于临界电流的条件下,当门控端没有输入电流时,通道端表现为超导状态;当门控端有电流流经时,假设门控端为金属材料,在金属附近区域产生热量引起局部温度的升高,当热量传递到下方的通道端后,压缩了通道端的临界电流,使通道端从超导态变为正常态;当门控端的电流移除后,器件重新恢复到初始状态。对于平面型hTron,流经门控端的电流只需大于其临界电流。

平面型hTron为单层器件,和立体型hTron相比,制备工艺更加简单,而立体型hTron热触发的速度更快。对于hTron器件,在设计过程中需要重点考虑门控端产生的热效应对通道端临界电流的压缩,即门控端和通道端两者之间的宽度存在制约关系。例如增加通道端纳米线的宽度要求更大的输入电流经过门控端,因为很小的电流经过门控端所产生的热效应对大尺寸通道端的压缩作用有限,对通道端的临界电流影响非常小。而当流经门控端的电流不变时,增加门控端的纳米线宽度也将减弱热效应,门控端宽度的增加意味着电阻的减小,单位时间内所产生的热量更小,热效应更弱。在实际应用过程中,hTron应尽量工作在真空的低温环境中,若工作在液氦环境下会削弱门控端的热效应,从而影响器件的工作性能。

3 “Y”-shaped cryotron (yTron)

yTron是一种利用电流阻塞效应(Current crowding effect)[17]来探测电流的三端子器件,因其形状类似于字母“Y”故而称之为“yTron”。两段纳米线以形状“Y”的方式连接在一起,连接处是宽度为数纳米的圆形拐角,两根纳米线分别被称为偏置臂和感应臂(图4(a)),插图为yTron的电路符号。当流经感应臂的电流逐渐增加时,偏置臂的临界电流也在同步增加,即偏置臂失超所需要达到的电流更高。因此,通过感应臂输入电流,即可调控偏置臂的超导临界电流(图4(b))。值得注意的是,yTron可以作为一种非破坏测量电流的器件,通过测量偏置臂的临界电流值,就可以得到感应臂上的电流,并且这种测量过程中,超导相变仅发生在偏置臂,不破坏感应臂的超导特性,因此这种电流测量是一种非破坏测量。在数字电路中使用时,yTron可被看作是一个反相器,执行反向逻辑。通过选择合适的偏置电流,当感应臂上无信号输入时,偏置臂处于正常态,反之,感应臂处于正常态。

图4 (a)yTron的SEM图和电路符号;(b)感应臂在五种不同偏置电流下偏置臂的I-V特性,插图为测试电路图[7]Fig. 4 (a) Simplified circuit schematic and Scanning electron micrograph of a yTron ;(b) I-V characteristics of the bias arm for five values of Is; (insert) Circuit schematic for testing the yTron [7]

yTron的工作原理依赖于电流阻塞效应,电流阻塞效应是指在纳米线的拐角处或者纳米线宽度突然变化时,靠近拐角内部或者靠近突变处的电流密度更大。yTron两臂的连接处部分存在尖锐的突变过程,因此当电流从某一臂流过时,靠近拐角的地方电流密度增大,其中的过程涉及涡流的边界穿越和吉布斯自由能的变化[17]。当两臂处于相同的偏置电流状态时,拐角处的电流密度相同,几乎不存在电流阻塞效应,在拐角处两臂产生的电流阻塞效应相互抵消;而当感应臂的偏置电流减少时,偏置臂的电流密度相对更大,由于感应臂无法抵消偏置臂产生的电流阻塞效应,拐角处电流密度将增大;若完全移除感应臂的偏置电流,拐角处的电流密度将更高,将有更多的电流短暂流向感应臂最后流向源端。当偏置臂流经的电流不断增加时,感应臂需要更大的电流用于消除电流阻塞效应,因此临界电流也随之增加。

4 应用

4.1 低温数字电路

在首次提出nTron的文章中,nTron被作为基础逻辑器件,搭建了“与”门、“或”门、“非”门等电路单元,演示了半加器的逻辑操作功能,展示了nTron作为逻辑器件在数字逻辑电路的潜在应用价值。随着单光子探测技术的发展,超导纳米线单光子探测器(SNSPD)已经成为目前单光子探测技术中综合性能最优异的探测器[18-19],在量子信息处理[20]等领域已经得到了广泛的应用。大规模SNSPD阵列是目前发展的重要方向之一,而如何实现阵列的低温读出是目前亟须解决的关键挑战之一。2018年,日本NICT的研究人员利用SFQ读出电路[21]读出了64像元的SNSPD阵列,通过对SNSPD输出信号的逻辑统计实现了SNSPD的位置编码,从而对SNSPD阵列进行空间位置识别。最大计数率为12.5 Mcps,并且保留了SNSPD本身的时间特性,但是此项工作中采用了大量的约瑟夫森结单元,因此整体功耗较高,编码器整体功耗为250 μW。

2020年,南京大学赵清源课题组[22]在单个nTron的结构上设计了多门控nTron结构(图5(a)),利用4个12门输入的nTron单元,构建了经典的四位二进制数字编码器。作者将4个多门控的nTron工作在“或”逻辑下,一个12门控的nTron只需要选择8个通道用于执行“或”逻辑操作,4个nTron的输出端对应了编码后的四位输出,即O1-O4(图5(c))。实验中对应位置响应的SNSPD输出脉冲经过两级nTron放大器后,同时输入到对应编码位置下的多门控nTron的门控端,从而实现位置编码,例如位置为“15”的SNSPD输出信号经过放大后同时触发4个nTron,产生四路输出,对应“1111”。位置为“3”的SNSPD输出信号经过放大后同时触发2个nTron,产生两路输出,对应编码“0011”。实验过程中测试了不同输入端口的临界电流,用于验证器件的均匀性(图5(d))。器件封装(图5(b))后进行测试,实验中测到的最大工作速率为250 MHz,并且该编码器实现了对15像元SNSPD阵列的位置编码读出。和一些其他的编码器读出方案对比,该编码器在功耗上也具有明显的优势,编码器整体功耗为361 nW。这为低温阵列探测器的信号读出和处理提供了一种新的解决方案,未来通过结构的设计和工艺的优化,有望实现更大阵列的位置编码读出。

图5 (a)12门控nTron结构SEM图;(b)封装后安装在PCB板上的编码器照片;(c)15-4编码器的电路结构图;(d)编码所有输入端口的临界电流[22]Fig. 5 (a) Scanning electron micrograph of a 12-gate nTron; (b) Photo of the encoder chip mounted on a printed circuit board; (c) Logic circuit diagram of the 15-4 binary encoder; (d) Critical currents for all input ports [22]

4.2 超导体-半导体接口

超导体-半导体接口是实现低温下的信号传导至常温下信号的关键技术。一个典型的半导体晶体管的输入阻抗为兆欧级别,而单个超导电子器件(例如RSFQ)的输入阻抗仅为数欧姆,因此信号在超导体和半导体之间的传输存在严重的阻抗失配问题,即低温下的电信号难以驱动晶体管等半导体电路。利用Stacks电路或SQUID放大器能够缓解失配问题,但功耗和器件面积成为限制其应用的因素。nTron失超后,能够产生数十千欧电阻,驱动能力强,因此能够成为接口电路的选择之一。

2017年,Zhao等人[23]首次利用nTron作为接口电路单元,实现了RSFQ和CMOS之间的互连(图6)。其技术方案为:将nTron的门控端宽度设置为20 nm宽,使得单个磁通量子也能够触发nTron;同时将nTron工作在锁存状态下,通道端失超后产生约4.7 mV的电压,用于驱动HEMT管,从而实现RSFQ和nTron以及CMOS三者之间的信号传输。此后,日本的Tanaka等人[24-25]同样利用nTron的驱动特性,实现了RSFQ逻辑电路、nTron驱动电路、CMOS存储器阵列三者为一体的大规模存储阵列。在此项研究中,nTron作为驱动接口,接受输入信号用于驱动CMOS存储阵列。由于采用nTron替代工作在电压态下的放大器和解码器,功耗大幅降低。2019年,美国NIST的McCaughan等人[26]在nTron和hTron的基础上,设计出一种高阻热开关器件,该器件为“三明治”结构,即热电阻-绝缘层-纳米线结构。该器件的热开关时间低于300 ps,恢复时间为15 ns左右并且输出阻抗大于1 MΩ。该研究团队用该器件将50 mV的输入信号变为1.12 V的电压输出,最终驱动了LED灯。

图6 RSFQ-nTron-CMOS混合电路的实验系统框图[23]Fig. 6 Simplified circuit schematic of the hybrid RSFQ-nTron-COMS circuit [23]

4.3 逻辑存储阵列

逻辑存储操作是实现超导计算机的重要一环。和半导体逻辑存储不同,超导体通常用环流表示存储逻辑,用超导环中环流的方向表示比特位“1”和“0”,例如用顺时针电流方向表示比特位“1”;而用逆时针电流方向表示“0”。近年来,利用RSFQ的存储阵列存在大尺寸单元的问题;RSFQ和CMOS的混合结构能够实现高速和低时间抖动的逻辑操作,但是存在着功耗和接口电路的问题;而利用磁性材料构建存储单元则需要对材料进行更加精确的调节。nTron和yTron以及hTron等器件具有百纳米的器件尺寸,能够很好地解决大尺寸和大面积问题。已经有研究[27]证明,利用超导纳米线构建的nanoSQUID能够利用动态电感而非几何电感调控超导环中的临界电流,可大大缩小器件尺寸,并且该器件不易受到磁场干扰。尽管超导环中产生的环流能够稳定存在,但是如何读取超导环中的电流而不破坏其中的状态是需要考虑的问题,而yTron作为一种非破坏性测量的器件,能够缓解这个问题。

2018年,Zhao等人[6]利用hTron和yTron构成超导环回路,构建了超导存储单元(图7(a))。该电路的核心在于利用hTron的热触发模式从而一次性捕获超导环能容纳的最大磁通数,形成超导环流,当写入正脉冲时产生顺时针环流,代表比特位“1”,写入负脉冲则产生逆时针环流,代表比特位“0”。yTron则负责超导环流的读出,同时不破坏环内的超导特性,因此该电路具有非易失性。单个器件尺寸面积为3 μm×7 μm(图7(b)),在实验中演示了存储和操作比特位“0”和“1”的过程(图7(c))。误码率为10-7的情况下,工作区间为4.6 μA,初步计算整体功耗为10-18J左右。

图7 利用nTron和yTron构建的存储单元电路:(a)电路结构;(b)存储单元电路的SEM图;(c)实验中读取和写入“1”和“0”过程的波形图[6]Fig. 7 Memory cell circuit composed of hTron and yTorn. (a) Simplified circuit schematic of memory cell; (b) Scanning electron micrograph of memory cell; (c) Experimental pulses for writing and reading bits ‘1’ and ‘0’[6]

2019年,NIST的McCaughan等人[28]利用Dayem桥并联电阻替代hTron结构,利用铌作为连接线,钨硅作为器件材料,构建了存储电路单元,该电路能够提高工作速度同时降低功耗。作者在10 MHz~1 GHz的速度下表征了该电路的性能。在50 MHz的工作速率下,最低误码率为10-6。美国MIT的Toomey等人[29]则利用NbN材料,在Zhao的工作基础上,利用Dayem桥并联电阻替代hTron结构,实现了对超导环流的定量调控,能够用于多比特的信息存储。与此同时,雷神公司的研究者[30-31]基于自旋霍尔效应的磁性存储器件分别和nTron以及hTron相结合,实现了新型的存储单元和阵列。而在更大规模存储单元的研究上,利用hTron构成的超导环回路目前实现了2×4的存储阵列[32],误码率实际测量为10-3左右。若要实现更大规模的存储阵列,采用这种结构则需要考虑器件面积和电流串扰以及布线等问题。

4.4 读出SNSPD

SNSPD的基本结构为蜿蜒线并且通过热点模型来探测光子事件,然而蜿蜒线的高动电感导致SNSPD恢复时间缓慢(热点增长和耗散),并且参数选择不当也容易导致锁存,增加功耗。如果光子探测事件能够从脉冲事件输出转换为其他方式,有可能在一定程度上避免这些行为。

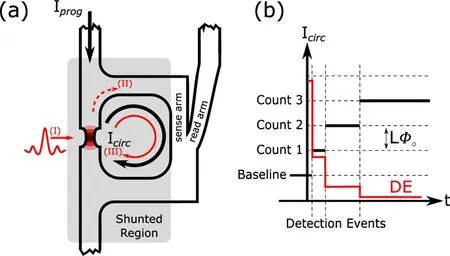

Onen等人[33]利用不同于蜿蜒线的探测器结构,将单光子触发事件转化为磁通量的变化,利用yTron读出磁通的变化量。纳米线结构能够探测光子事件,纳米线和电阻并联(图8(a)灰色部分)后能够实现磁通的定量调控,yTron的感应臂和纳米线则构成超导环用于存储超导环流,超导环中的磁通所形成的环流经过感应臂能够调控yTron读出端的临界电流。多个光子事件将在超导环内形成顺时针环流的累加,实现类似于电荷耦合器件(CCD)的计数功能。然而该研究工作的缺点也很明显,环流的增加,使得纳米线的有效电流偏置减少,导致纳米线探测效率的下降(图8(b)红色曲线)。天津大学胡小龙课题组[34]则将单段纳米线结构替换为并联的超导纳米线结构(SNAP),实现了符合光子计数的功能。

图8 (a)器件的电路符号图电阻;(b)探测效率和环流随着时间的变化图[33]Fig. 8 (a) Schematic representation of the device; (b) Conceptual graph of circulating current and the resultant detection efficiency versus time [33]

4.5 神经网络

人脑感知周围环境和进行自身内部调节的方式是以神经脉冲的形式进行信息传递的,脉冲神经网络(SNN)为代表的第三代人工神经网络,在行为模式上更接近人类大脑中利用脉冲序列信息传递的方式。一个神经元主要由前后神经元和用于连接神经元的突触结构组成。而脉冲神经网络的核心在于构建脉冲尖峰电路单元,它要包含单个神经元的一些基本功能,如突触可塑性和阈值响应以及不应期等。若要实现更大规模的神经网络结构,单个电路还需具备以下特性:第一,能够不断产生脉冲序列,并且速度快;第二,电路单元具有可扩展性和高扇出能力,能够同时连接多个相同的电路结构或者更大的网络结构;第三,无论是在静态还是在动态下均能够保持低功耗。半导体神经网络的解决方案面临着功耗的问题,而约瑟夫森结的神经网络结构虽然速度快、功耗低,但是存在扇出能力弱的问题,超导纳米线在器件尺寸和扇出能力以及功耗上具备优势。

美国MIT的研究人员[35]采用超导纳米线并联电阻的形式,产生弛豫振荡效应,结合神经元在生物习性下的信息传递模式,在软件和硬件层面(图9)构建了单个神经元的脉冲电路单元[36-37],使其具备了神经元的一些基本功能。该团队以这个电路单元为基础,在仿真过程中完成了图片识别、竞争决策等任务。也有研究者利用超导环单元构建类似于忆阻器的阵列的结构,结合深度学习的实验方法来模拟人工神经网络[38]。而NIST的研究者[39-40]则采用光子作为信息传递的媒介的技术方案,以SPD作为光子的接受者,hTron作为输出级输出脉冲信号,nTron则兼具扇出能力,可用于连接不同神经单元,实现神经网络。

图9 神经网络电路结构图,两个震荡单元构成超导环用于模拟钠钾泵的离子输运。插图为震荡单元的输出脉冲[36]Fig. 9 Simplified circuit schematic of the neuron, consisting of two superconducting nanowire relaxation oscillators linked together in a superconducting loop used to simulate ion transportation of sodium-potassium pump. Inset shows experimentally measured oscillations from an isolated relaxation oscillator [36]

5 总结

超导纳米线三端子器件从提出至今,已经在多个领域发挥作用。虽然取得了一些突破性的成果,但器件潜在的性能优势还远没有达到极限,尤其是制约它们工作速度和功耗的相关物理机制亟待探索和继续突破。进一步地,超导纳米线三端子器件的发展趋势也将走向大规模集成化的道路,但针对这一领域的研究还停留在初始阶段,需要在工艺平台建设、EDA软件、测试标准等多方面共同努力。随着未来研究的进一步深入,必然会有力的推动超导纳米线三端子器件和多学科交叉融合发展,发挥超导电子器件的应用价值。此外,最新研究发表了基于电场调控的超导三端子器件[41-45],但由于其微观工作机理目前尚处于探索阶段,门控电压较高,本文暂不进行讨论。我们相信,随着对超导纳米线的深入研究,还会有更多新型的超导纳米线三端子器件被开发和应用。