一种超宽速率图形产生方法

2023-01-04贾冒华孔令磊

贾冒华,童 琼,孔令磊

(1.北京无线电计量测试研究所,北京 100039;2.空装驻北京地区第一军事代表室,北京 100039)

1 引 言

随着现代科技的发展,雷达、导航、通信和电子对抗等系统所产生的数据量呈几何级数增长,对传输系统的高效性和稳定性提出了更高的要求。 这就要求误码率测试设备不但能够支撑STM-1/STM-4/STM-16(速率分别为155 Mb/s,622 Mb/s 和2.488 32 Gb/s)等标准的低速光纤网络的误码测试,而且能够适应最新400GBASE/400GAUI 民用以太网络中数据传输链路的可靠性、稳定性评测,需要具备超宽速率图形产生能力。

在传统的误码率测试技术中,通常采用集成的LC 窄带振荡器产生本振信号,提供给逻辑门电路搭建的高功耗图形产生电路,形成某些离散特征速率的图形信号,速率支持范围窄,并且不能够连续可调,单台设备的工作速率无法有效覆盖多种应用场景,特别对于一些非标领域的需求不能够很好的支持。 本文介绍了一种超宽速率图形产生方法,可以实现50 Mb/s~60 Gb/s 速率范围内的测试图形产生,能够极大拓展误码率测试设备的应用范围。

2 图形产生器设计

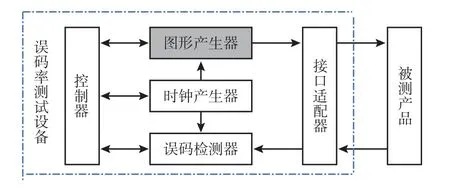

误码率测试设备通过发送包含特定图形信息的串行信号并对反馈信号进行比对分析来实现被测产品的误码率统计[2],其工作原理如图1 所示。 其中,图形产生器用于接收控制器配置参数并生成包含测试图形的串行信号,目前常采用FPGA(现场可编程逻辑门阵列) +MUX(多路复用器)的架构实现。

图1 误码率测试设备原理框图Fig.1 Block diagram of bit error rate tester

对于产生50 Mb/s ~60 Gb/s 超宽速率范围的测试图形,在当前技术条件下由单一电路独立实现非常困难。 考虑到适应FPGA 等图形编码器件的常规技术指标(接口速率一般只达12.5 Gb/s),本方案中将整体工作速率分解为4 个速率段:(50 ~500) Mb/s,500 Mb/s~12.5 Gb/s,(12.5~32) Gb/s,(32~60) Gb/s,原理如图2 所示。 由FPGA 器件产生测试图形后,其中(50~500) Mb/s 速率段的低速信号,可通过普通IO 管脚直接输出;500 Mb/s ~12.5 Gb/s速率段的信号速率较高,可通过GTx(G比特收发器)管脚直接输出;(12.5~32) Gb/s 速率段的信号无法从FPGA 管脚直接输出,可将测试图形数据经FPGA 内部分解后转换成四路并行信号,通过GTx 管脚输出后再经两级2:1 MUX 器件并串转换合成;(32 ~60)Gb/s 速率段的信号也无法从FPGA 管脚直接输出,同样将测试图形数据经FPGA内部分解后转换成八路并行信号,通过GTX 管脚输出后再经三级2:1 MUX 器件并串转换合成。 在整个分段方案中,只有末级的四选一开关需要工作在50 Mb/s~60 Gb/s 的全速率范围,可以选用宽带特性较好的机械开关实现。

图2 50 Mb/s ~60 Gb/s 图形产生器原理框图Fig.2 Block diagram of 50 Mb/s ~60 Gb/s pattern generator

3 图形序列处理

3.1 图形序列发生

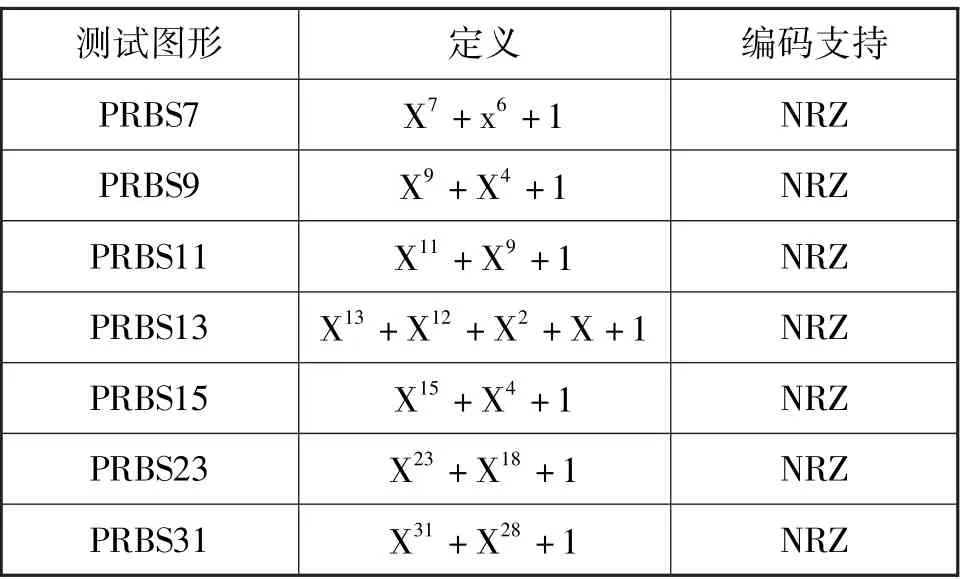

常用的误码率测试图形均由伪随机序列构成,而每组伪随机序列都可以用其本原多项式来表示,如表1 所示[3]。

表1 常用测试图形列表Tab.1 General test pattern list

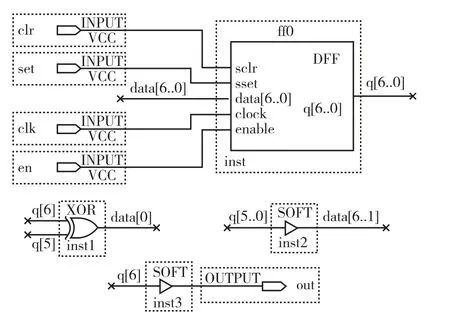

在FPGA 中一般通过构建线性反馈移位寄存器的方式来设计伪随机序列生成电路。 首先确定移位寄存器的反馈方式,然后根据伪随机序列的本原多项式设定移位寄存器的长度,可以得到想要的伪随机序列。 下面以PRBS7(伪随机位序列7)为例,介绍串行伪随机序列的生成方法[4]。 由表1 可知,PRBS7 伪随机序列的本原多项式[5]为X7+x6+1,寄存器的第七级和第六级参与反馈,在FPGA 中建立的逻辑电路如图3 所示。

图3 PRBS7 生成电路图Fig.3 Electrical diagram of PRBS7 generator

其中,ff0 为7 位的寄存器,en 为使能引脚,控制该寄存器处于工作或空闲;set 为初始化引脚,首先将set 设置为高电平,寄存器的值全部初始化为“1”,避免了输出全“0”的状态,然后将set 设置为低电平,则寄存器正常反馈输出;clr 为清零引脚,设置为高时将寄存器恢复为初始状态;clk 为时钟输入引脚,可以设定整个寄存器的工作速率;out 为输出引脚,伪随机序列由这里输出至下一级。

为适应表1 中所列的7 种不同长度的测试图形,其中PRBS31 图形最长。 因此,本方案将伪随机序列生成模块设计成一个31 位的串行移位寄存器[6],通过一个七选一开关选通寄存器的不同反馈支路,进而适应七种不同测试图形的伪随机序列生成,再用一个选通控制位同时控制反馈连接方式和最终输出图形,最终建立的伪随机序列生成模块电路如图4 所示。

图4 伪随机序列生成模块电路图Fig.4 Electrical diagram of pseudorandom sequence generating module

其中,size[2..0]为测试图形的输出控制,通过设置不同的size 值可以控制FPGA 内的移位寄存器的级数和反馈连接方式,进而可以实现不同长度的序列输出。 需要注意的是,伪随机序列生成模块同一时间只能输出一种测试图形。 由一个clk 时钟信号驱动线性移位寄存器工作,clr 为清零控制位,en 为使能位,只有en 为“1”的时候,才能输出有效数据。

3.2 图形序列分解

如前文所述,针对(50~500) Mb/s 速率段和500 Mb/s~12.5 Gb/s 速率段的测试图形信号,FPGA 器件可以通过自身管脚直接输出。 而(12.5~32) Gb/s 速率段和(32~60) Gb/s 速率段的测试图形信号,需要后级多次并串转换才能合成,因此需要对前一节生成的测试图形序列进行分解,以保证最终输出信号的连续性。

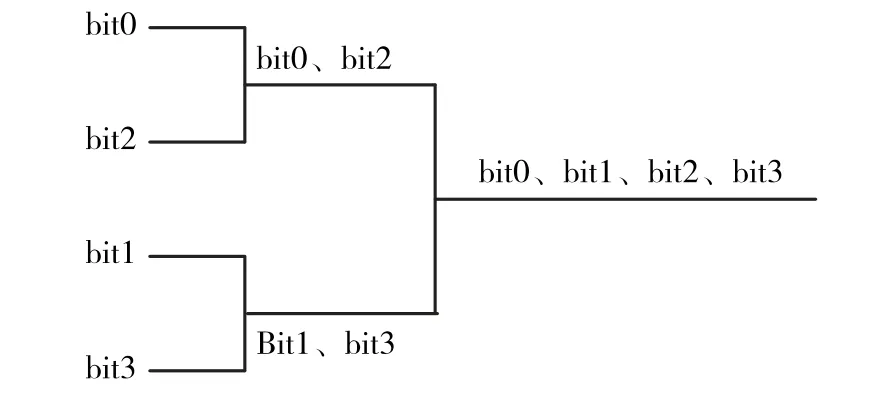

对于(12.5~32) Gb/s 速率段生成的测试图形序列,首先将其按照先后顺序分解为4bits 为单位的分段结构“bit0,bit1,bit2,bit3”;然后将每个分段结构的“bit0”由FPGA 器件的端口3 输出(端口号参见图2),“bit2”由FPGA 器件的端口4 输出,“bit1”由FPGA 器件的端口5 输出,“bit3”由FPGA 器件的端口6 输出;最后经过两级MUX 并串转换可以得到测试图形序列“bit0,bit1,bit2,bit3”。 图形序列分解的原理如图5 所示。

图5 (12.5~32)Gb/s 速率段图形分解原理图Fig.5 Block diagram of pattern decomposition for (12.5~32)Gb/s section

同理,对于(32~60) Gb/s 速率段生成的测试图形序列,首先将其按照先后顺序分解为8bits 为单位的分段结构“bit0,bit1,bit2,bit3,bit4,bit5,bit6,bit7”;然后将每个分段结构的“bit0”由图2 中FPGA器件的端口3 输出,“bit4”经由FPGA 器件的端口4输出,“bit2”经由FPGA 器件的端口5 输出,“bit6”经由FPGA 器件的端口6 输出,“bit1”经由FPGA 器件的端口7 输出,“bit5”经由FPGA 器件的端口8输出,“bit3”经由FPGA 器件的端口9 输出,“bit7”经由FPGA 器件的端口10 输出(端口号参见图2);最后经过三级MUX 并串转换可以得到测试图形序列“bit0,bit1,bit2,bit3,bit4,bit5,bit6,bit7”。

4 图形输出验证

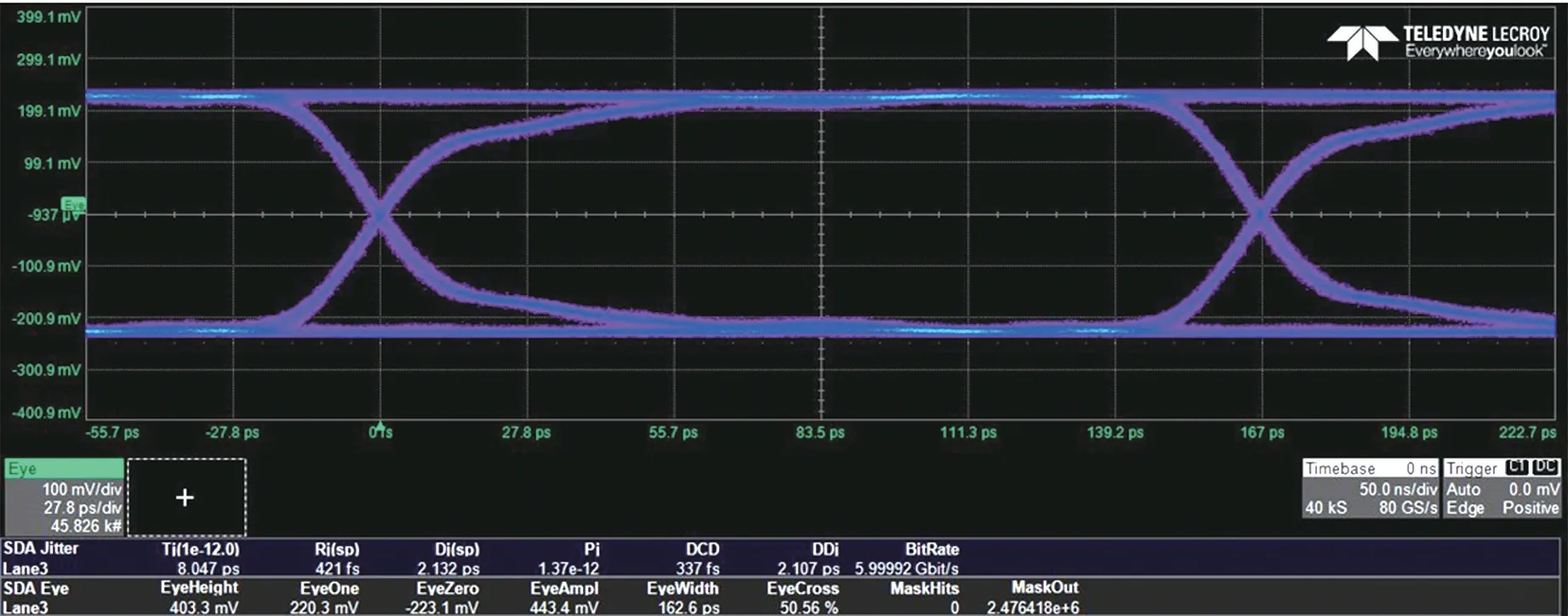

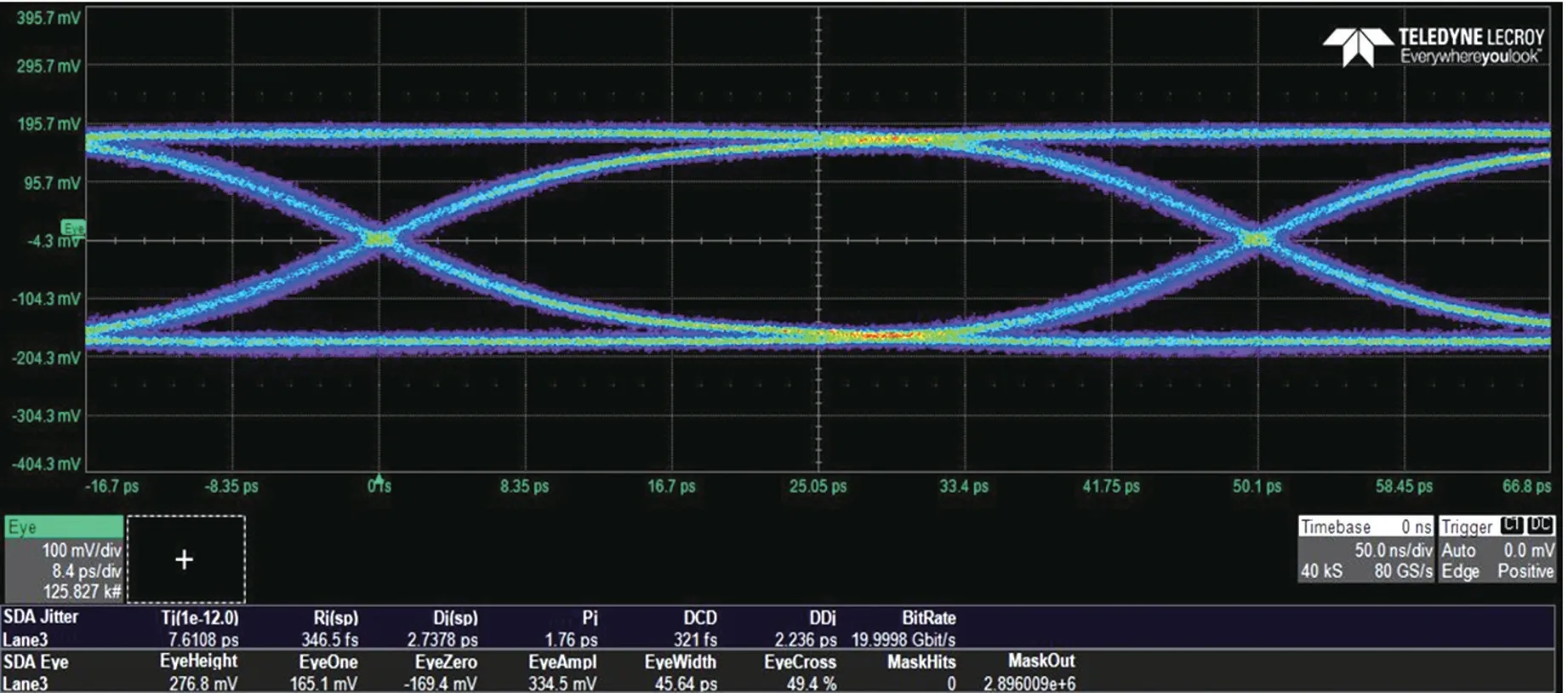

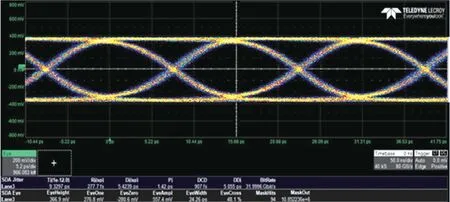

依据前文所述的工作原理,选用Xilinx 公司的FPGA 芯片XC7VX690T80、ADSANTEC 公司的DC~64 Gb/s MUX 模块ASNT5151-MOD 等核心器件搭建误码率测试系统。 利用高速采样示波器对误码率测试系统输出的测试图形信号进行了眼图指标测试[7],其中系统工作时钟由标准信号源提供。 其中6 Gb/s,20 Gb/s,32 Gb/s,56 Gb/s 等典型工作速率[8]的眼图测试结果如图6 至图9 所示。

图6 6 Gb/s 测试图形的眼图Fig.6 Eye diagram of 6 Gb/s test pattern

图7 20 Gb/s 测试图形的眼图Fig.7 Eye diagram of 20 Gb/s test pattern

图9 56 Gb/s 测试图形的眼图Fig.9 Eye diagram of 56 Gb/s test pattern

5 结束语

提出一种用于误码率测试设备的超宽速率图形产生方法,并基于FPGA +多级MUX 的图形产生架构搭建了测试系统,将50 Mb/s~60 Gb/s 输出信号合理的划分为(50 ~500) Mb/s,500 Mb/s~12.5 Gb/s,(12.5~32) Gb/s,(32~60) Gb/s 四段,既能避免单一电路承担全速率范围信号输出的压力,又能利用图形序列编码技术保证测试数据的连续性,最终实现一路50 Mb/s~60 Gb/s 范围内超宽速率测试图形信号的产生。