基于磁通门和时域数字鉴频的磁场锁定系统

2022-12-28张啸阳姚守权徐俊成

张啸阳,姚守权,徐俊成,蒋 瑜

华东师范大学 物理与电子科学学院,上海市磁共振重点实验室,上海 200062

引 言

永磁型磁共振仪器广泛应用在医疗成像、能源地矿、食品农业中.磁体作为仪器的重要组成部分,通常采用钕铁硼(Nd-Fe-B)材料制成,该材料的缺点是温度稳定性较差,通常1 ℃的温度变化会导致磁场强度变化1 000 ppm(Parts per Million,百万分之一)[1].除此以外,磁体会受到附近大型铁磁性物体移动和电流变化等因素影响,包括50 Hz 交流电、电梯升降、地铁列车运行等[2,3].磁场的稳定性分为长期稳定性和短期稳定性:影响长期稳定性的因素主要是由温度变化造成的慢速磁场偏移;而影响短期稳定性的因素主要是由环境干扰引起的瞬态磁场波动.在医疗成像中,磁场不稳定会导致每次采集信号的相位出现波动,造成图像模糊、图像错位甚至产生伪影[4,5];而在食品等检测领域,磁场偏移会导致样品检测的一致性变差,影响检测结果的重复性和可靠性.

为解决慢速磁场偏移,现有技术主要是在磁体外侧加装隔热棉等保温材料,并外加恒温控制装置[1].但由于保温材料效果有限,且恒温控制装置存在温控精度不够和反馈滞后等问题,只能将磁场稳定在57 ppm/天[6]的程度.为了避免瞬态磁场波动带来的影响,现有技术主要采用主动和被动磁屏蔽装置.被动磁屏蔽装置是采用高导磁材料,安装在磁体周围或仪器所在房间的各个墙面上;而主动屏蔽装置则是在磁体周围加装主动补偿设备,主要包括磁传感器、三维磁场线圈和电流源.屏蔽装置可以有效稳定磁场,但存在成本高昂、装置繁琐等缺点.除了以上两类方法外,还可以采用核磁共振傅里叶变换方法[7,8]来对磁场进行锁定,即对锁样品射频激发后,将得到的磁共振信号经过放大、正交检波、低通滤波和采样后,再通过傅里叶变换计算核磁共振信号频率,从而计算磁场偏移并进行补偿.但此方法电路比较复杂,同时傅里叶变换也需要一定时间,会造成产生补偿磁场的延迟,因此它通常用于慢速磁场偏移的测量和补偿.

本文在现有研究的基础上,利用了磁通门传感器的高灵敏性和核磁共振测量频率方法的高精确度,并结合现场可编程门阵列(Field Programmable Gate Array,FPGA)的高速处理性能,设计了基于磁通门和时域数字鉴频的磁场锁定系统,包括(1)磁通门锁场方法[9],拟解决因环境干扰所造成的瞬态磁场波动(其频率在1 kHz 以下);(2)时域数字鉴频锁场方法,旨在解决磁场慢速波动的问题.时域数字鉴频锁场方法在现有恒温控温装置的基础上,首先对锁样品进行射频激发,然后将产生的磁共振信号放大,通过混频、低通滤波获取差频信号,接着采用过零比较器将差频信号转化为数字方波直接送入FPGA 进行高速鉴频,不需要进行采样和傅里叶变换.通过简单的电路和数字处理,就能够测得磁场的变化量.将两种锁场方法同时使用,即使磁通门传感器放置在磁体附近,但由于磁体本身具有较好的磁屏蔽特性,温度引起的主磁场变化也不会对磁通门锁场方法造成影响.

1 理论与方法

1.1 磁通门锁场方法

常见的环境干扰会造成主磁场的瞬态波动,而0.2 μT 以上的磁场变化就会对磁共振实验造成影响[3].为了检测并补偿磁场波动,首先需要确定测量磁场的方法.常见方法主要有以下几种:(1)无定向磁强计,通过检测磁场与磁化物体间的作用力来测量磁场;(2)感应线圈磁强计,通过检测线圈中磁通变化来获得表征磁场强弱的电信号;(3)磁通门磁强计,根据软磁芯材料的磁化饱和特性来检测磁场强度[10].磁通门磁强计噪声系数低、灵敏度高,且分辨率可以达到nT[11],能够满足微弱波动磁场的检测需求.因此本文采用磁通门传感器,对环境的瞬态波动磁场进行高灵敏探测.

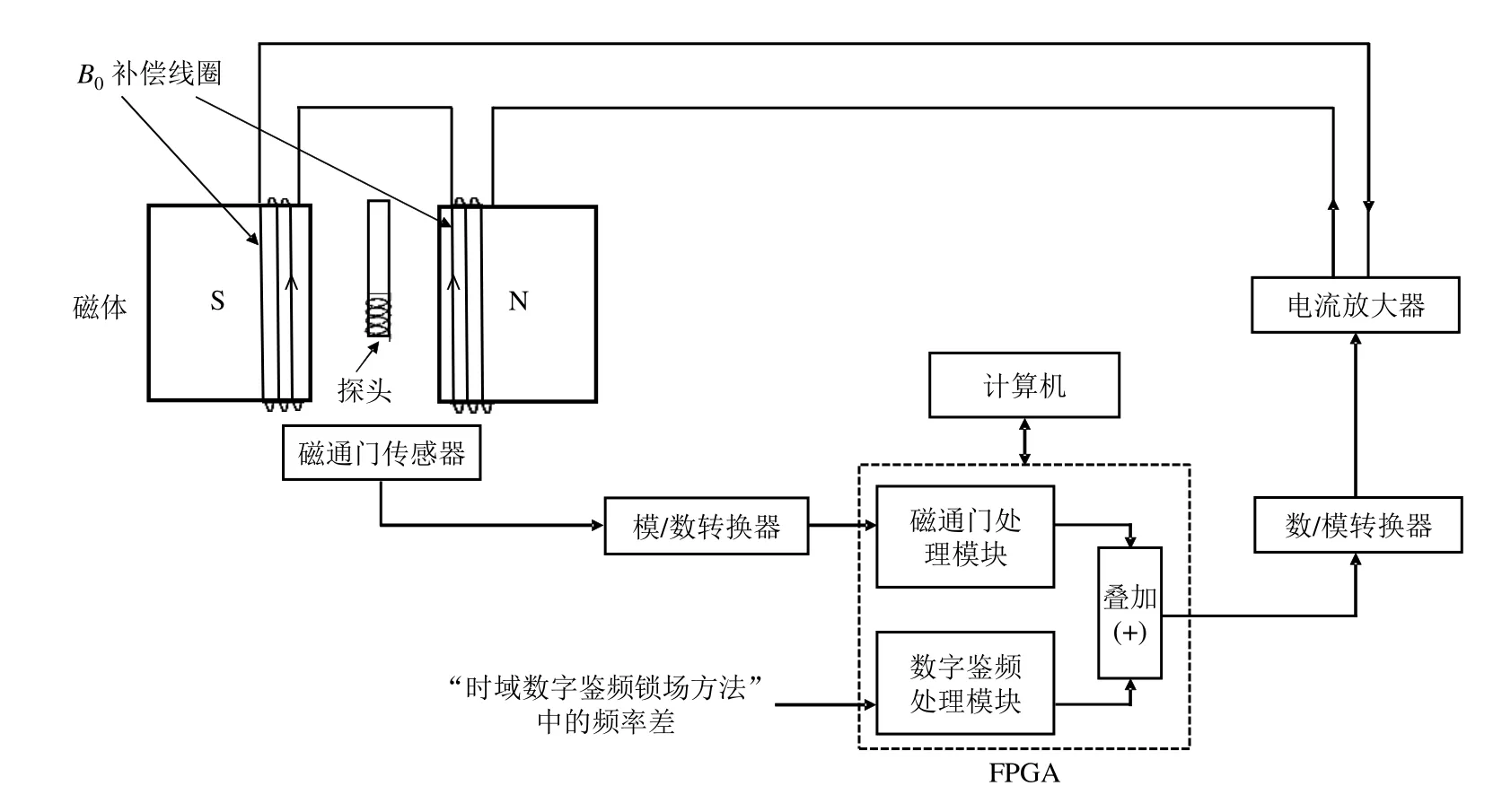

图1为磁通门锁场方法的原理框图,将磁通门传感器放置在磁体附近,所测磁场以模拟电压形式输出,同时包含磁体在该处产生的静态逸散磁场、地磁场和外界干扰造成的瞬态磁场,经过模/数转换器(Analog to Digital Converter,ADC)转为数字信号后送入FPGA 进行高速数值计算.计算处理后得到的补偿量通过数/模转换器(Digital to Analog Converter,DAC)转为补偿电压,驱动电流放大器产生补偿电流,然后送入磁体两极绕制的B0补偿线圈,从而产生补偿磁场,以达到稳定磁场的目的.

图1 磁通门锁场方法的原理框图Fig.1 Block diagram of field locking method based on fluxgate sensor

由于磁通门锁场方法只考虑对波动的磁场部分进行补偿,因此在FPGA 的逻辑设计中,首先需要对静态磁场和瞬态磁场进行分离.将一段时间的数字测量信号取平均,其结果作为静态磁场,并从测量数值中去除,剩下的就是瞬态磁场值.当有外界瞬态磁场干扰时,为了准确测量静态磁场,可以适当延长测量时间,以尽可能消除静态磁场的影响.不过,即使不能从测量值中准确去除静态磁场,在一定程度上造成补偿电流的小幅度增加,导致测得的核磁共振信号频率出现一定偏移,也不会影响瞬态磁场的补偿效果.在磁通门测量磁场并进行模/数转换的时候,会存在测量电路内部噪声造成的测量电压毛刺和量化误差等的影响.为了减少这些因素造成的测量偏差,我们将瞬态磁场值采用通频带较为平坦的巴特沃斯(Butterworth)数字低通滤波器进行滤波处理.本文拟解决频率在1 kHz 以内的环境干扰,根据软件模拟仿真,将滤波器的截止频率(−3 dB 点)设为1.2 kHz,阶数设为4 阶,可以保证具有较高的带外抑制性能,滤波器的幅频响应如图2所示.

图2 巴特沃斯低通滤波器幅频响应Fig.2 Amplitude-frequency response of Butterworth low pass filter

瞬态磁场值经过滤波后,再做均值化处理,可以进一步减少噪声的影响,提高测量精度.以最大环境干扰频率1 kHz 为例,假设单个周期满足20 个抽样点数,就可以对瞬态磁场有较好的补偿效果,这样至少需要20 k/s 的采样率,本文使用最大采样速率为1 M/s 的ADC 采集模拟信号,则最多可以每50 个点数做一次均值化处理.经过上述处理后,基于PID(Proportion Integral Differential)算法[12]的思想,采用调节比例的方法计算出补偿值.在软件仿真中,根据磁通门检测电压与磁场的关系(100 mV/μT),同时测量并拟合出DAC 输出电压与磁场强度变化的线性关系,以此确定补偿比例系数.在磁通门锁场的实际测试中,可以进一步手动微调补偿比例系数,以保证产生的补偿磁场可以更好地反相抵消瞬态波动磁场.

本文的设计中采用高灵敏度磁通门传感器(Mag670,Bartington),量程为±100 μT,精度为0.1 nT,量程和精度能够满足磁场波动检测要求.将磁场检测值送至FPGA 中进行高速计算,从开始分离磁场到输出补偿电压值的总时间小于1 μs,具有较快的实时补偿性能,由于采用了高速数字补偿计算,整个磁场锁定方法性能稳定,重复性较好.图1中提及的“时域数字鉴频锁场方法”将在下文进行介绍,将磁共振信号转为方波后同样送入FPGA 处理,并将两种方法计算出的磁场补偿值进行叠加,一并送入DAC 产生补偿电压.

1.2 时域数字鉴频锁场方法

永磁磁体的温度稳定性较差,温度的微小变化都会造成主磁场漂移,从而影响到磁共振实验的一致性和可靠性.为了解决这一问题,首先需要对磁场的这一变化进行高精度测量.采用核磁共振方法能够精确测量磁场,通常是将脉冲激发后的磁共振信号进行放大、模数转换和正交检波等处理,然后采用傅里叶变换计算出磁场偏移值,但这种方法电路实现较为复杂.本文则采用时域数字鉴频方法测量样品共振频率的偏移.在磁体已经采用保温、控温装置的基础上,采用较为简单的电路设计,将线圈感应的磁共振信号经过混频、低通滤波和过零比较后,转为数字方波送入FPGA,直接精确测量磁共振方波信号的周期,计算出锁样品的共振频率偏移.进而可对磁场的变化进行补偿,达到磁场锁定的目的.我们以本课题组正在研制的食品快检磁共振分析仪中采用0.5 T 永磁材料设计的磁体部分为例,来说明本文如何采用时域数字鉴频锁场技术,对因环境温度改变引起的慢变化磁场进行精确测量.锁样品采用硫酸铜溶液,1H 共振频率约为21.375 MHz.

1.2.1 采用混频技术提高鉴频精度

将磁共振锁场信号转为方波后,采用FPGA 时钟对数字方波的周期进行计数,根据计数值可以计算锁信号的周期和频率.假设FPGA 采用100 MHz 时钟对数字方波的周期(计数周期为10 ns)进行计数.直接测量时,被测信号频率过高,测得的计数值仅为4.且由于被测信号与FPGA 时钟之间无关联,所以该计数值还会存在±1 的计数误差[13,14],这将导致计数值的误差过大,不能满足对锁共振信号频率的测量精度(±1 μT)要求.为了解决这个问题,可将锁共振信号与本振参考信号先进行混频处理并取出差频信号,然后采用FPGA 对差频信号的周期进行测量,就可以提高周期检测的精确度,但具体能达到的精度水平还与差频信号的频率选取有关.

差频信号的频率选取,需要同时考虑最大的磁场波动和锁共振信号的衰减情况.首先,混频后的差频信号频率必须大于不同时间测量的锁共振信号频率的最大偏差,即锁共振信号的频率必须始终大于本振参考信号的频率,因为仅仅通过对差频信号的周期测量,无法判定锁共振信号的频率是大于还是小于本振参考信号频率.在差频信号的频率选取之前,首先对磁体的波动情况进行测量,12 h 测得的锁共振信号最大频率波动约为2 kHz,再考虑可能出现的温度异常等情况,我们将温度引起的锁共振信号的频率偏差选取在大于5 kHz 的范围.其次,需要对锁样品共振信号的弛豫情况进行分析,以评估锁信号能够用于周期测量的时间范围.本文采用单脉冲序列,磁共振信号经过约90 dB 放大后,利用示波器(DSOX1204A,Keysight Technologies)同时观察射频振荡信号[15]和自由感应衰减信号.在射频脉冲结束后,射频振荡信号持续时间约为40 μs.另外,锁共振信号最大峰的峰值约为2 V,持续约400 μs 后,信号变得越来越弱.因此为了提高对锁信号周期测量的准确性,我们选择在射频脉冲结束后等待50 μs 开始对锁信号的周期进行测量,并且测量持续时间不超过300 μs,避免因电路、磁体性能变差等原因,造成锁信号变弱和弛豫时间缩短,进而无法对其进行准确测量.但另外,在条件允许的前提下,差频信号的频率越低,对其周期测量的精确度就会越高.因此为了保证测量精度,差频信号的频率也不能设置过高.

假设选取的差频信号的频率为fIF(对应周期为TIF),采用的FPGA 时钟频率为fclk,FPGA 对差频信号进行n个周期测量,周期计数值为N,那么:

根据(1)式可知,通过测量计数值N,可以计算差频信号的频率.将其与本振参考信号频率相加,即可得到锁共振信号的频率.通过对不同时间锁共振信号频率的测量,从而获得磁场的波动情况.

假设将磁场锁定在差频信号频率为fIF,0的位置(称作锁定频率),此时对应的差频信号n个周期的计数值为N0,则每次测得的频率偏差ΔfIF为:

根据(2)式,当频率偏差ΔfIF>0 时,测得的计数值N小于N0,说明此时测得的频率高于锁定频率fIF,0.

本文使用的FPGA 测量时钟为100 MHz,每次测量的锁信号方波周期数固定不变,信号测试时间介于100~300 μs 之间,那么不同测量周期n时计算的差频信号频率如表1所示.如果将测试时间为200 μs 时计算得到的差频信号频率设置为锁定频率,从表1可以看出,当只对1 个周期的锁方波信号进行测量、测试时间为300 μs 时,测得的频率与锁定频率的偏差仅为1.667 kHz,不能满足上文分析温度引起的锁共振信号频率偏差大于5 kHz 要求.测量5 周期和10 周期的两种方法,都能够满足因温度引起的锁共振信号频率偏差大于5 kHz 要求.同时,将测量时间为200 μs 所对应的测量计数值N加1,根据(2)式计算得到5 周期和10 周期时最小频率测量精度分别为1.25 Hz(对应磁场0.029 4 μT)和2.5 Hz(对应磁场0.058 7 μT),均满足±1 μT 的测量精度要求.从表1也能看出,测量信号周期越长,测量精度会越高.本文选取锁定频率为25 kHz,连续测量5 个周期,对时域数字鉴频效果进行验证.当对全部实验参数反复验证确认后,可以在后续实验中对差频频率进行优化,以便进一步提高测量精度.

表1 不同测量周期数下,计算得到的差频信号的频率Table 1 The frequency measurement corresponding to different measurement periods of difference frequency signal

1.2.2 磁场补偿

根据上述方法,首先测量获得锁方波信号周期的计数值N,然后计算得到锁共振信号的实际频率,并进一步计算该频率与目标锁定频率的偏差;其次,采用主动补偿方法,在B0补偿线圈中注入补偿电流,使之产生反方向的频率偏移,以抵消计算得到的锁信号频率偏差,从而达到锁定磁场的目的.补偿电流由电流放大器产生,其输入电压由DAC 进行设置,因此需要知道DAC 设置的补偿电压值与锁信号频率偏差之间的关系.本文采用FPGA 可重配置的数据采集卡(USB-7856R,National Instruments),其DAC 输出电压范围为−10 ~ +10 V,测试不同输出补偿电压U(V)所产生的频率偏移fΔ(Hz).为了减少因测试时间较长,由环境温度变化引起的锁共振频率偏移的影响,每次都先后分别设置补偿电压为0 V 和不同电压值,将测得的锁共振信号频率相减即可得到频率偏移fΔ.在−10 ~ +10 V 全量程范围进行测试.其中,在−1 ~ +1 V 范围,每隔0.1 V 测试一次频率偏移;在其他电压范围,每隔0.5 V 测试一次频率偏移,一共测得56 组数据.然后通过线性拟合,得到输出补偿电压U和产生的频率偏移fΔ之间关系:

拟合优度值R2为0.999 1,说明拟合度较好.

通过(2)式计算得到频率偏差ΔfIF后,由B0补偿线圈产生fΔ−,对磁场偏移进行补偿,以达到磁场锁定的目的.即有:

结合(2)~(4)式,即可得出计数值N与DAC 输出电压U的关系:

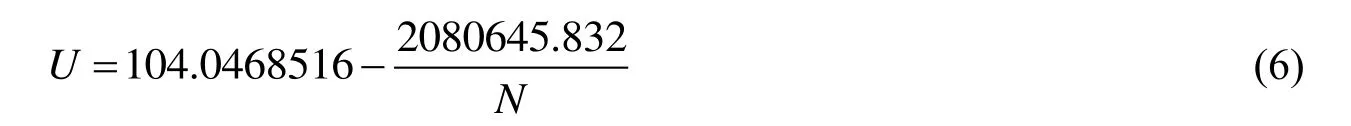

本文同时测量5 个周期,锁定频率设置为25 kHz,此时测量计数值为20 000,FPGA 时钟频率设为100 MHz,带入(5)式,得到该测试条件下计数值N和DAC 设置输出电压U之间的关系:

将利用数字鉴频方法测得的计数值N代入(6)式,即可计算输出补偿电压U,从而达到锁定磁场的目的.

1.2.3 锁场激发与接收电路

针对时域数字鉴频锁场方法,我们设计了相关的锁场电路.如图3所示,主要包括探头、发射链路、接收链路三个部分.为了避免锁样品与磁场中心核磁共振样品之间的射频干扰,在探头盒体内部设计了一个独立腔体,放置用于锁场的发射/接收(Transmit/Receive,T/R)开关电路、自发自收线圈[16]和样品.选用硫酸铜溶液作为锁样品,对其中的氢核进行脉冲核磁共振探测.经测试,即使锁样品和磁体中心位置氢样品间的共振频率相差较小,但由于采用了不同的腔体设计,屏蔽性能较好,因此也能较好地解决两个探测线圈之间的射频干扰问题.锁场线圈需要尽量靠近磁场的中心位置,这样在测量锁共振信号频率并对磁场进行锁定时,中心位置核磁共振样品所在位置磁场也同样达到锁定状态.

图3 时域数字鉴频锁场方法的电路框图Fig.3 Electrical block diagram of time domain digital frequency discrimination and field locking method

射频源采用直接数字频率合成器(Direct Digital Synthesis,DDS)进行设计,同时产生两路射频信号,分别作为发射链路的激发信号和接收链路的本振参考信号.FPGA 产生门控信号驱动射频开关,将射频源输出的射频信号转为射频脉冲信号,经过射频放大器放大后,送入探头中激发锁样品.

在接收链路中,由于线圈感应的锁共振信号比较微弱,首先采用低噪声前置放大器进行放大,接着由二级放大器放大至峰峰值2 V 左右,再通过带通滤波器进行选频滤波,抑制带外噪声.在现有0.5 T 磁场中,锁样品的共振频率约为21.375 MHz,将其与21.350 575 MHz 的本振信号混频,通过低通滤波取出差频信号,由过零比较器转为数字方波后送入FPGA 计算得到补偿电压.在FPGA中,将磁通门锁场方法和时域鉴频锁场方法计算的磁场补偿电压值相加,由同一路DAC 进行输出并产生补偿磁场,实现对磁场偏移的锁定.

1.3 软件设计

本文涉及的两种锁场方法,采用同一个数据采集卡进行控制,同时具有16 bit 的ADC 和16 bit的DAC,其中的FPGA 可以重配置并进行数字算法设计和逻辑控制.为了更便捷地实现相应功能,使用LabVIEW 图形编程环境,对上位机界面控制程序和FPGA 终端程序进行设计.上位机程序主要实现以下几方面功能:(1)控制DDS 射频源,设置激发信号与本振参考信号的频率、相位和幅度;(2)通过DAC 输出补偿电压,驱动电流放大器,产生磁场补偿电流及匀场调节电流;(3)磁通门传感器采集数据的处理和补偿,包括磁场分离、低通滤波、均值化处理、数字波形实时显示、补偿比例系数设置等;(4)时域数字鉴频方法中的频率偏移测量和计算等.

上位机程序和FPGA 终端的数据传输采用RT 轮询(Real Time Polling)和先进先出存储器(First In First Out,FIFO)传递方式.RT 轮询主要用于传输静态磁场设定值、测量周期计数值等对速度要求不高的参数;而FIFO 主要实现对磁通门瞬态测量波形的实时显示.FPGA 终端中主要包括磁通门锁场、时域数字鉴频锁场和补偿叠加输出三部分功能,经过逻辑设计并编译下载至采集卡后,实现对整个锁场系统的控制.

2 测试结果与讨论

将磁通门锁场方法和时域数字鉴频锁场方法整合到一起,研制了一套磁场锁定系统,如图4所示.数据采集卡采用NI 公司的USB-7856R,发射链路与接收链路用于获得时域数字鉴频方法中的锁共振方波信号,稳压电源为各个模块提供直流电压.

图4 磁场锁定系统实物图Fig.4 Magnetic field locking system

2.1 磁通门锁场方法测试

磁通门锁场方法是对环境干扰造成的瞬态磁场波动进行锁定,比如地铁、电梯和50 Hz 大交流干扰源.这些干扰源一般都来源于仪器所在实验室的外面,距离仪器通常都在10 米以外甚至更远的地方,磁通门传感器探测到的瞬态磁场波动能够比较准确地反应磁体中心的磁场波动.

为了测试对瞬态磁场波动的锁场效果,首先需要产生一个模拟的干扰磁场.我们将函数发生器(33250A,Agilent)输出的正弦波信号通过音频功率放大器(Micro-tech 600,Crown)进行放大,以便在磁体附近产生交变磁场.现有音频功放的驱动功率较弱,干扰源因此只能放在离磁体较近的位置,干扰源、磁通门传感器和磁体中心两两之间距离都为30 cm 左右,这样磁通门传感器检测到的磁场波动与磁场中心的磁场波动有一定偏差,因此磁通门传感器方法的磁场锁定效果不太理想,并且模拟干扰场的频率也不能设置太高.

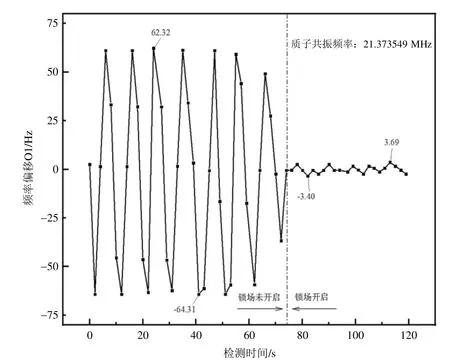

我们对本课题组研制的食品快检分析仪进行了磁场锁定功效测试,利用指纹谱分析软件的稳定性测试功能,对磁场中心的矿泉水样品进行磁共振采样,然后通过傅里叶变换计算氢的共振频率,每次测量间隔约为2 s,采样带宽为10 kHz,采样点数为4 096,共振频率的测量精度为2.4 Hz.利用上文介绍的函数发生器和音频功率放大器,产生干扰场的频率为1 Hz、函数发生器的输出幅度为400 mVpp.将磁通门传感器固定在磁体外罩的合适位置,在没有产生干扰场情况下,测量得到静态磁场对应的电压值为−9.118 V.通过测量干扰场所产生的瞬态磁场波动电压,利用1.1 节介绍的方法计算补偿比例系数,并根据实际的磁场补偿效果进行微调,确定补偿比例系数为−1.197 2,连续测量约2 min,测得锁场开启前后共振频率的变化如图5所示.可以看出,在没有开启锁场的情况下,氢共振频率的波动最大达到了64.31 Hz;在开启磁场锁定后,共振频率变化稳定在±4 Hz(对应磁场为±0.093 9 μT)的范围内,与频率测量精度基本保持一致,说明基于补偿的磁场锁定效果比较理想.

图5 磁场共振频率在锁场前后的波动情况Fig.5 Magnetic resonance frequency fluctuation with and without field locking control

2.2 时域数字鉴频方法检测频率偏移

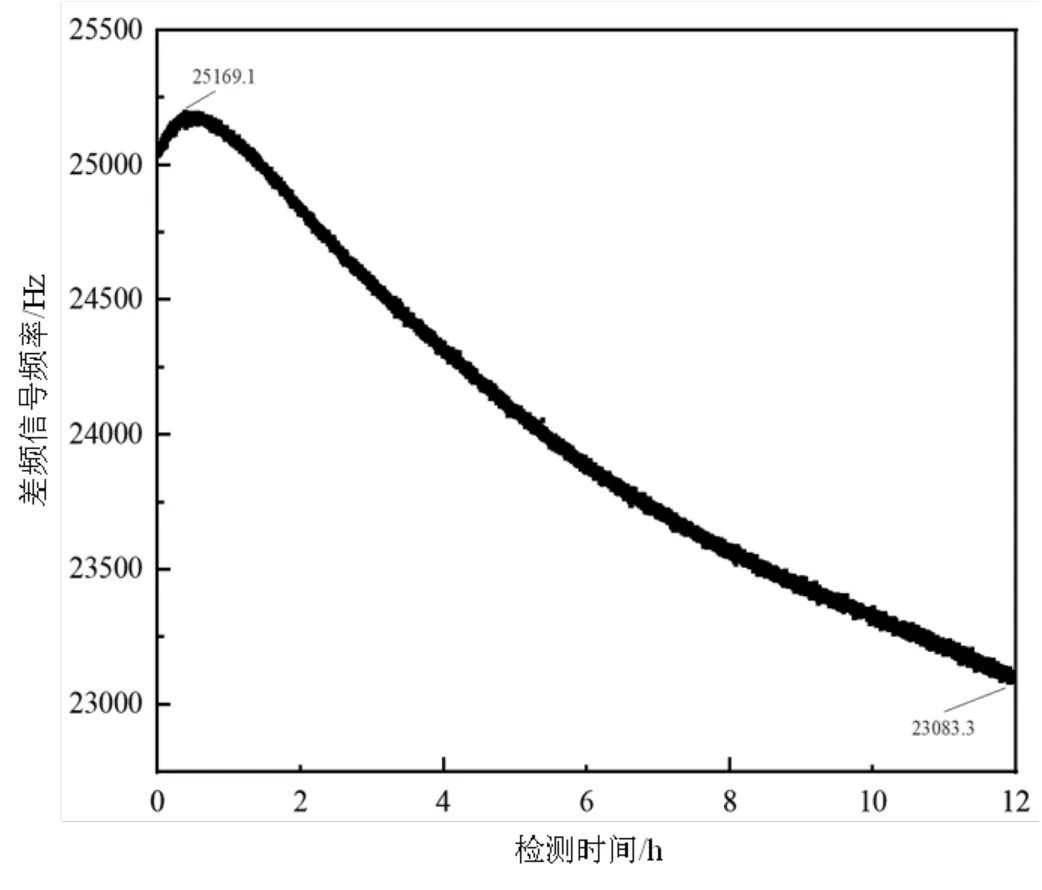

对磁场变化进行高精度测量是对永磁磁体磁场进行锁定的前提.在不外加瞬态干扰磁场的情况下,本文采用时域数字鉴频方法测量由环境温度引起的磁场频率的偏移.在对磁通门锁场和时域数字鉴频锁场相关的FPGA 逻辑进行设计及编译后,显示最高工作频率为120 MHz,为了方便计算,本文设计采用100 MHz 作为计数时钟,此频率能够满足鉴频测量的精确度.为了采用时域数字鉴频方法对锁共振信号频率测量进行验证,仪器自动进行了长达12 h 的连续测试,每隔5 s 对锁样品进行一次射频激发和差频信号周期测量.脉冲宽度30 μs,激发中心频率21.375 575 MHz,本振参考频率21.350 575 MHz,每次检测5 个锁差频信号方波的周期,根据FPGA 测量周期计数值并计算出差频信号频率偏移.图6显示了不同时间测量的差频信号频率,将其与本振参考信号频率相加即可得到实际的锁信号共振频率.从图中可以看出,12 h 的共振信号频率偏差为2 085.8 Hz,继续测量的话,频率偏移还会在一定时间内继续增大.在开始阶段频率有所增加,之后频率逐步减小,这个慢速的频率变化,就是由环境温度变化引起的(整个过程磁体控温温度始终设置在32 ℃).对相邻测试数据点进行分析,采用相邻10 点数据进行移动平均处理,每一点数据与平均数据相减得到残差,其最大的残差约为±40 Hz(对应磁场为±0.939 4 μT),求得均方根误差(Root Mean Square Error,RMSE)约为10.1 Hz(对应磁场为0.237 2 μT),满足±1 μT 的测量精度要求,相对于激发中心频率来说,最大的频率测量误差为1.87 ppm.

图6 时域数字鉴频方法测得12 h 差频信号偏移情况Fig.6 12 hour difference frequency signal offset by time domain digital frequency discrimination method

3 总结

本文针对0.5 T 永磁型食品快检磁共振分析仪中出现的瞬态磁场波动和慢速磁场偏移问题,整合了磁通门锁场和时域鉴频锁场两种方法,并设计了相关电路,基本解决了永磁磁体的磁场稳定性问题.当存在模拟的瞬态干扰磁场情况下,共振信号频率能够稳定在±4 Hz(对应磁场为±0.093 9 μT)范围内;而时域数字鉴频锁场方法可以快速、精确地测量磁场偏移,经计算处理后可以进一步补偿由温度变化造成的磁场偏移.由于时间和实验条件所限,磁通门锁场方法仅采用模拟干扰源进行测试,下一步是寻找真实的自然干扰环境对锁场效果进行验证;而时域数字鉴频方法仅测试了对锁共振信号频率的测量,最大的频率测量误差为1.87 ppm,实现了对磁场偏移的精确测量,将在下一阶段对磁场偏移的锁定效果进行测试验证;在后续的测试中,会同时测试瞬态磁场波动和温度引起的慢速磁场波动的锁定效果,并另文讨论.

此外,现阶段时域数字鉴频锁场方法还存在优化空间,可以从减少放大器噪声、提高滤波器性能、改善过零比较器滞后参数等角度着手,进一步减小鉴频误差.未来的目标是解决上述问题和测试补偿效果,并希望通过优化脉冲序列参数,缩短测量间隔时间,争取将该方法同时用于对环境造成的瞬态磁场波动进行锁定,这样可以进一步简化磁场锁场系统,提高磁场稳定的效果.

利益冲突

无