基于System Generator的任意底对数变换FPGA实现方法

2022-12-25李武旭

李武旭,李 宏

(四川九洲空管科技有限责任公司,四川 绵阳 621000)

0 引 言

现场可编程门阵列(FPGA)具备极强的并行处理能力,被广泛运用于雷达、通信和测量等领域中,尤其对实时性要求较高的应用中。在这些应用中可能涉及到对数运算。目前,在FPGA上实现对数变换的方法主要有查表法[1-2]、CORDIC[3-4]和线性近似法[5]等。查表法所需要的存储单元随着精度的增加或输入值范围的增大而呈指数增加。CORDIC[3]法的实现结构简单,但计算精度与迭代次数直接相关,处理延时和逻辑资源花销也会增加。线性近似法由于本身的缺陷导致精度有限,且近似曲线的设计过程复杂。

本文介绍一种采用分段拟合方式实现任意底对数变换的近似方法,并联合System Generator、MATLAB和Simulink等工具进行设计与验证协同开发,将近似曲线的设计、理论模拟仿真、算法FPGA实现以及算法仿真验证等过程统一起来,并通过修改参数设计出不同底和精度要求的对数变换。

1 任意底对数的近似计算原理

在数字系统中,数据通常采用2种二进制表示形式定点数和浮点数。浮点数格式由符号位(S)、偏移指数位(E)和尾数位(M)三部分组成[6]。单精度浮点数格式的x可表示为:

x=(-1)s2(E-127)(1+M)

(1)

对于任意非负数x(S=0),其以a(a>0,且a1)为底的对数logax可分为以2为底的对数转换和对数底变换2个处理过程,即:

(2)

通常,连续函数可以通过麦克劳林级数进行近似表示,则对数函数log2(1+t)的麦克劳林级数可表示为:

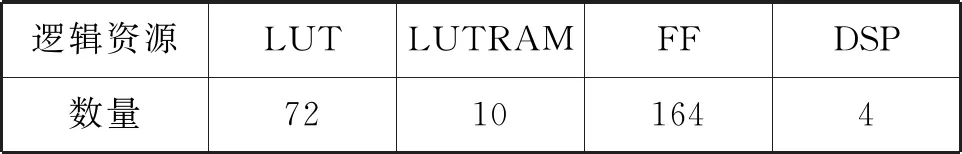

-1 (3) 此外,因为对数log2(1+t)的麦克劳林级数存在公因式t。若定义辅助函数faux(t)为: (4) 则式(2)可重写为: (5) 辅助函数faux(t)是由无穷项多项式构成的幂级数,在实际中,精确的计算faux(t)是不现实的,即使对faux(t)的级数进行截断,也需进行复杂的幂运算,故必须对faux(t)的计算方法进行简化[7]。在[0,1)范围内,辅助函数faux(t)的曲线呈非线性连续变化且单调递减(见图1),采用曲线拟合方法对faux(t)曲线进行近似。为了降低计算复杂度,faux(t)拟合曲线的阶数应尽量小,而faux(t)呈非线性变化,直接采用一次多项式拟合效果肯定不理想,故将t取值区间均分为D段,按区间分段进行一次拟合。图1中分别显示了4种情况下的拟合效果。 图1 辅助函数的理论曲线和拟合结果 图1分别显示了faux(t)的理论曲线、拟合曲线及其两者间差异。从图1可看出,二次拟合误差在±5.8×10-3以内;当分段数为4、8和16时,一次拟合误差分别在±3.4×10-3、±9.4×10-4和±2.5×10-4以内。与二次拟合相比,一次拟合的拟合误差随着分段数增加而减小,且可获得更好的近似结果,也具有更低的计算复杂度。因此,分段一次拟合方法更适用对辅助函数faux(t)进行近似。可见,辅助函数拟合曲线是一个分段函数,其表达式为: (6) 通过辅助函数的近似处理,可将对数快速计算过程进一步化简为: (7) 本文采用的目标FPGA为Xilinx的Kintex-7系列XC7K325T,其包含运算单元DSP48E1。每个DSP48E1均包含1个25位宽的预加法器(Pre-Adder)、25×18位宽的乘法器和48位宽的累加器(Accumulator)等。对数计算的数据位宽和运算结构应适应DSP48E1的特性,需对常数和运算结果进行量化,但引入量化误差。 (8) 在FPGA实现时,通过简单的位裁剪处理实现这种转换关系,不需要占用额外的逻辑资源。结合式(7)和式(8)并经简化后,可得新的快速对数变换表达式: (9) 在计算过程中,以M的高W位作为地址从ROM中实时获取。 而除以D运算可转换为右移W位操作,无需除法器,不占用额外FPGA逻辑资源。对数变换过程主要以定点数乘法和加法为主,不存在其他复杂的运算过程,其原理框图如图2所示。 图2 快速对数变换的FPGA实现原理框图 基于硬件描述语言(HDL)代码编写的传统FPGA开发方式,要求开发人员对处理算法和硬件有深入认识,开发周期比较长。当发生算法改动或硬件平台改变时,需要从源代码入手进行修改,工作量大,维护困难。System Generator作为高性能的数字信号处理(DSP)系统快速建模与实现工具,是DSP高层系统和Xilinx FPGA 之间的桥梁,能够使设计人员快速开发出高性能的FPGA来实现DSP算法,可在MATLAB/Simulink 环境下对算法级系统进行图形化建模和系统级仿真[8]。System Generator通过简易的图形化设计方式代替HDL开发的方式,避免了代码可读性差的缺点,方便成熟设计的共享和移植。System Generator是Xilinx提供的FPGA硬件开发工具,使开发人员能够在Simulink开发环境下,通过图形化的方式搭建快速对数变换的系统模型,并生成针对Xilinx FPGA优化的参数化设计。与原理框图的组成略有差异,这个System Generator模型由输入/输出接口、数据分割处理、以2为底对数转换、对数换底变换、异常检测处理和System Generator标志等模块组成。输入/输出接口使用Gateway In和Gateway Out模块实现Simulink和System Generator之间的数据传递,也用于确定用户逻辑设计的边界(相当于HDL代码中的顶层输入/输出端口定义)。System Generator标志允许用户设置系统和仿真参数,包括目标开发平台、目标器件、工作时钟等,还用于调用代码生成器将Gateway In和Gateway Out之间的模型转换为HDL代码。 快速对数变换的输入采用单精度浮点数格式,中间计算结果和转换输出则采用定点数格式。对数运算对负数无意义,零的对数转换结果为负无穷(由于定点数的数值范围有限而无法正确表示),通过异常检测处理模块来识别这2种特殊情况,同时它们的转换结果用比正常值更小的其它数值代替。 在传统FPGA开发方式下,快速对数变换实现分为3个独立过程,首先需通过MATLAB对算法进行模拟仿真验证,计算出参数A、c0、c1和c2并进行量化,接着编写HDL代码进行FPGA实现,然后编写Testbench文件通过逻辑仿真工具对FPGA设计进行逻辑仿真验证。一旦FPGA平台或者对数变换设计需求改变,很可能造成逻辑设计发生变化并须重新进行设计与验证。这种方式需要设计师使用多种开发软件平台单独、串行地开展算法设计、FPGA实现和逻辑仿真验证工作,开发效率低,非常不便于快速对数变换设计的共享和移植。 System Generator结合MATLAB和Simulink构建出FPGA设计与验证联合开发环境。System Generator以图形化的方式完成FPGA逻辑设计,并利用大量的MATLAB函数和Simulink模块完成算法理论模拟仿真、产生测试激励和开展设计效果分析。在该开发环境下,快速对数变换的整个设计包含模型初始化配置模块、测试激励产生模块、浮点数对数变换模块、快速对数变换模块和对数转换误差分析模块等部分,其中模型仿真初始化配置模块采用m文件形式,其余模块均采用Simulink和System Generator模块进行图形化设计,如图3所示。 图3 快速对数变换的联合设计与验证模型 在Simulink环境下,测试激励同时传递给浮点数对数变换模块和快速对数变换模块进行仿真,通过对数转换误差分析模块可显示出快速对数转换和理论对数转换的计算结果,并分析两者之间的差异情况。图4显示了2个模块进行以10为底对数转换结果,从图中可以看出两者的转换结果基本一致,说明快速对数转换的算法有效且System Generator系统模块设计正确。 图4 快速对数转换和理论计算结果 此外,以浮点数对数变换结果为参照,分析了不同对数转换的绝对误差和相对误差情况,图5(a)和图5(b)显示了相同分段拟合情况下以10为底对数和自然对数2种计算的绝对误差情况。对比图5(a)和图5(c)可看出,随着拟合分段数的增加,对数转换的绝对误差会改善,与理论分析一致。 图5 快速对数转换和理论计算的误差情况 通过System Generator标志调用代码生成器将快速对数变换的系统模型转换为HDL代码,并产生VIVADO工程。在VIVADO开发环境中,对快速对数变换模块的HDL代码进行逻辑仿真,其结果如图6所示。快速对数变换模块需花费12个时钟周期正确完成以10为底的对数转换,其计算结果与理论值误差很小,并能够识别出负数和零对数转换的异常情况。 图6 快速对数转换的逻辑仿真结果 在VIVADO中,对HDL代码进行综合后,以10为底的对快速对数变换所使用的FPGA逻辑资源如表1所述。 表1 FPGA逻辑资源使用情况 本文提出利用浮点数的特点和对数转换的性质,将任意底对数转换过程转换为以2为底的对数转换和对数底变换2个步骤,利用分段拟合方法对以2为底的对数变换进行近似,使任意底对数转换能够在FPGA上以有限的乘法和加法简单实现。同时,联合System Generator、MATLAB和Simulink开展任意底对数变换进行FPGA实现的设计与验证联合开发,该开发方法能够显著提高FPGA开发效率,便于FPGA设计的共享和移植,在工程实际中具有一定的推广意义。2 辅助函数的近似计算

3 基于FPGA的对数变换设计优化

4 快速对数运算的FPGA设计与验证

5 对数变换的FPGA设计与验证联合开发

6 结束语