含失调补偿的高速灵敏放大器的设计

2022-12-23肖世周贾一平杨海钢秋小强

肖世周,贾一平,杨海钢,,秋小强

(1.中国科学院空天信息创新研究院,北京 100190;2.中国科学院大学电子电气与通信工程学院,北京 100049;3.山东芯慧微电子科技有限公司,山东 济南 250001)

静态随机存储器(Static Random Access Memory,SRAM)被用于数据的高速缓存。灵敏放大器(Sense Amplifier,SA)作为SRAM 读出电路的核心,通过检测位线(Bit Line,BL)上的微小压差,将其转换为全摆幅信号,实现数据的快速读出[1]。根据端口数量的差异,SA 分为差分型、单端型;根据放大原理的不同,差分SA 又分为电压型、电流型及电荷型[2]。锁存器型SA 作为一种输入输出节点共用的差分电路,和单端SA 相比,结构更简单;比电流镜型SA 速度更快;和交叉耦合型SA 相比,避免了短路功耗;比Strong ARM 锁存型SA 电压余量更大[3]。但制造芯片时的环境偏差会引起晶粒、晶圆间的差异,且特征尺寸越小,晶体管沟道长和宽的偏差比会逐渐增大,使SA 检测到的压差来源于失调电压VOS,导致读出错误。

1 灵敏放大器失调分析

1.1 失调电压的来源推导

灵敏放大器中几毫伏的失调,可能会导致SRAM中数据读出时出现逻辑错误。故SA 电路设计时,需要充分考虑失调的来源、影响及补偿方式。

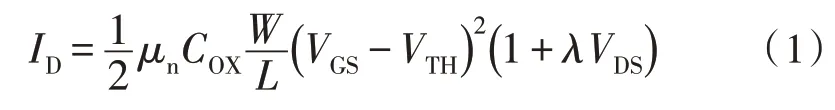

晶体管饱和区的漏电流公式[4]如下:

其中,W、L、VGS、VDS是与电路设计相关的参数,μn、COX、VTH、λ是与制造工艺相关的参数。

传统锁存器型灵敏放大器如图1 所示。

图1 传统锁存器型灵敏放大器

在推导SA 失调与上述参数的关系之前,参考线性电流近似模型[1,5-6],做以下近似:

1)V1(0)>VS1且V2(0)>VS2,即两根位线需要先放电再检测压差,其中,V1(0) 是BL 端的初始电压,V2(0)是BLN 端的初始电压,VS1、VS2为V1、V2节点的翻转电平。

2)失调主要来源于N管,且N1 管的阈值电压VTH1小于N2 管的阈值电压VTH2。

3)节点放电时,电流与时间简化为一阶线性关系。

4)忽略沟道长度调制效应,即λ=0。

5)初始时刻,两个BL 节点实际电压与翻转电压差值近似相等。

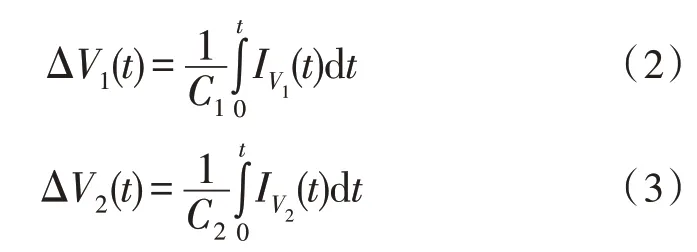

首先,灵敏放大器在[0,t)时间内的节点电压变化量如下:

根据积分中值定理[7],存在一个ξ值,有:

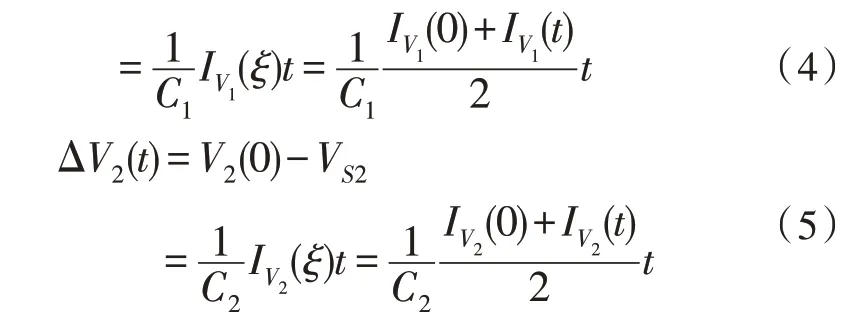

t时刻放电结束后,有:

对式(4)、(5)化简,并代入式(1),有:

对式(7)、(8)做商且开二次方根,有:

化简后,得:

所以,在上述近似下,VTH是影响灵敏放大器失调的最重要因素。

1.2 失调电压的分析

失调电压分布符合高斯分布[8-9]:

若失调电压均值μ为0,则有:

根据Pelgrom 定律[10],δ(标准差)和晶体管尺寸的关系符合式(13):

其中,比例常数AVT和工艺有关[10-12],与氧化层厚度tOX成正比,与衬底的掺杂浓度NB的四次方根成正比,如式(14):

该次设计采用UMC 65 nm CMOS 工艺,NMOS 的AVT约为3 mV·μm[4,12],对于一个0.06×0.6 μm2的晶体管来说,δ约为15.81 mV,3δ约为47.43 mV。

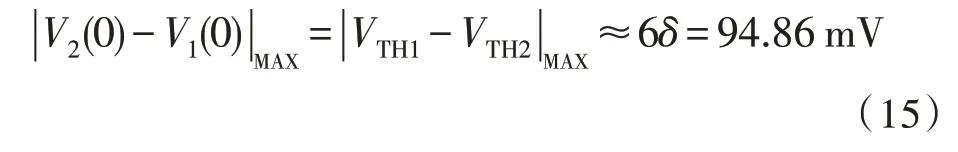

忽略3δ范围外的偏差,有:

仅考虑NMOS 阈值失调,SA 需要等到位线压差大于94.86 mV时,才能保证准确读出SRAM 中的数据。另外,由于N 阱衬底的掺杂浓度较高[13],若不忽略来自PMOS 的失调,SA 的灵敏度会进一步下降,降低数据读出速度,故减少失调电压是新型SA 的一个重要研究方向。

1.3 失调电压的补偿

目前,有多种方案来设计低失调的灵敏放大器,如下:采用成比例增加晶体管的宽度和长度的方式来降低δ的值,但版图面积牺牲较大,且输出电容增加[14];使用热载流子注入校准手段可调节晶体管的阈值电压,但测试成本和不稳定性偏高,可能出现电学特性退化的现象[14-15];基于BIST 原理,内建多组相同尺寸的灵敏放大器,每次仅有一组工作,导致占用较大面积,而且控制电路较为复杂[16];利用衬偏调制效应,通过调节衬底电压来减小阈值失配,但提高了电路对衬偏电压的精度要求[16-17];文献[1]提出的自反馈电流校准技术,通过调节SA 两个输出端口的放电电流来降低失调电压,但由于失调补偿支路的电压余量较小,导致位线上的低电平无法降到零电位,严重时影响电路功能。

2 新型灵敏放大器的设计

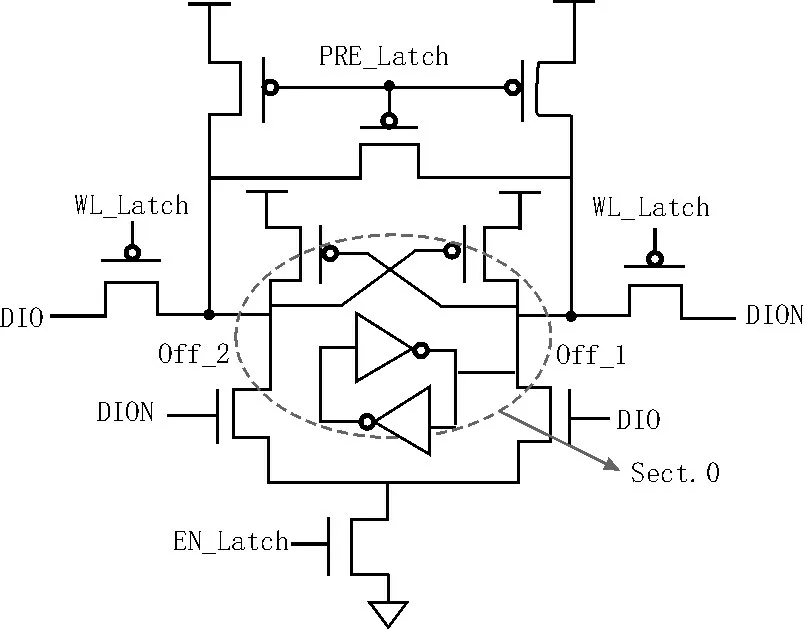

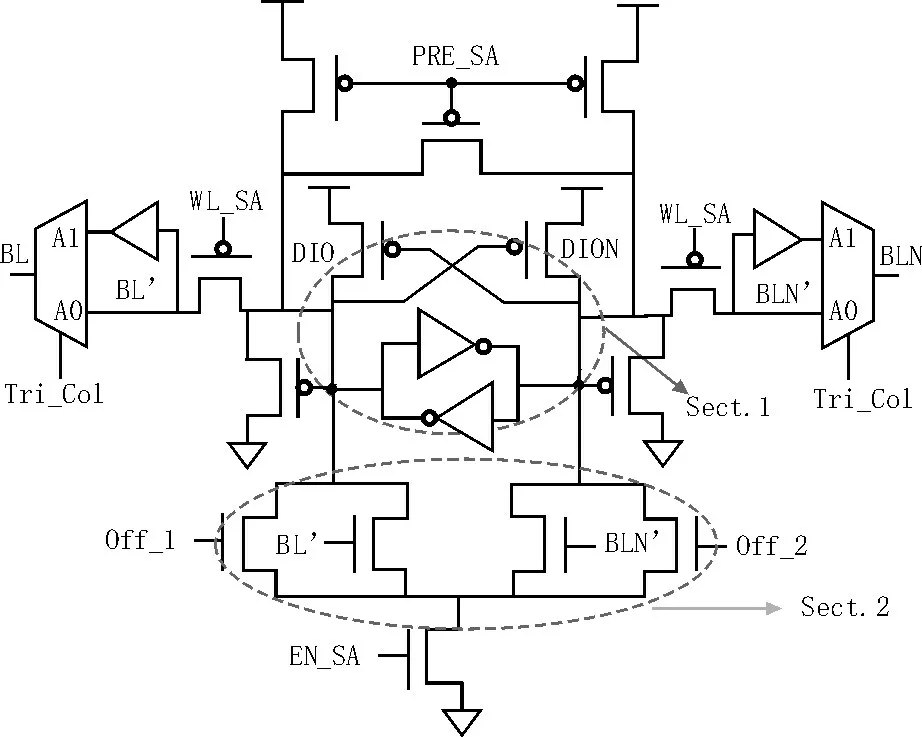

该文基于锁存器型灵敏放大器,在电流反馈失调校准原理的指导下,提出了一种新型的灵敏放大器。电路分为失调检测和灵敏放大两部分,失调检测电路如图2所示,核心灵敏放大电路如图3所示。

图2 失调检测电路

图3 核心灵敏放大电路

失调检测电路包含预充和失调补偿两个工作阶段:对Off_1 和Off_2 节点预充结束后,传输管打开,DIO、DION 信号传入该电路。如图3 所示,由于Sect.1 失调电压的存在,DIO 和DION 间的微小压差经过Sect.0 放大至全摆幅信号,之后反馈回如图3 所示的电路中,补偿结束,关断传输管。每个灵敏放大器只需要进行一次补偿操作,然后补偿信号Off_1、Off_2 被锁存。

核心灵敏放大电路同样包含预充电和放大两个工作阶段:对SA 的内部节点预充后,打开传输管,SRAM中的信号经BL、BLN传至Sect.1,使能信号EN_SA置为高电平,灵敏放大器开始工作。补偿信号(Off_1、Off_2)、BL’、BLN’提供四条电流支路:当差分输入端任一侧的电平被拉低时,该支路关断,另一支路保持为高电平。

在位线上增加一级多路选择器(MUX),数据读出时选择带有BUFFER 的支路,使BL’、BLN’被拉低至晶体管阈值时,加快其降为干净的零电位;且隔离位线上寄生电容的影响。在DIO 和DION 节点处增加两个二极管接法的PMOS管,当DIO 或DION 上的电压降至PMOS 的阈值时,PMOS 作为开关能将节点电压迅速拉低至零电位。

由于改进后的电路相较于锁存器型灵敏放大器,在电源和地之间增加了一级NMOS,以供补偿选择,减小了电压余量,故在进行参数设计时,为减少σ值,Sect.1 电路保持尺寸不变,Sect.2 电路尺寸变为原来的3 倍。

3 电路仿真与验证

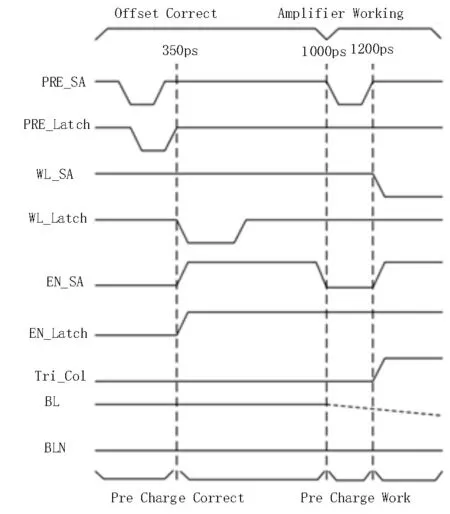

电路仿真主要分为四个阶段:失调检测阶段的预充及补偿、灵敏放大阶段的预充及放大。该SA 电路在UMC 65 nm CMOS 工艺下,进行前后仿工作,并与锁存器型SA进行比较。电路的时序图如图4所示。

图4 仿真时序图

3.1 延时仿真

数据读出时的延时主要包括两部分:位线压差达到SA 灵敏度的延时,以及SA 对位线压差进行放大的延时。无失调补偿时,SA 的灵敏度为110 mV,和前面的推导结果基本吻合;在失调补偿后,SA的灵敏度为50 mV。表1、表2 显示了TT corner、25 ℃、1.0 V 供电电压下,失调补偿前后的SA 进行数据读出的延时情况,TBL为位线电平降到灵敏度电压的延时,TSA为灵敏放大器的延时,TTOTAL为总延时。

表1 失调补偿前延时对比情况

表2 失调补偿后延时对比情况

3.2 失调仿真

预充结束后,对SA 内部DIO、DION 节点压差进行1 000 次Monte Carlo 分析。失调仿真结果表明,补偿后的节点压差均值相对于0 V 偏离比补偿前更小。

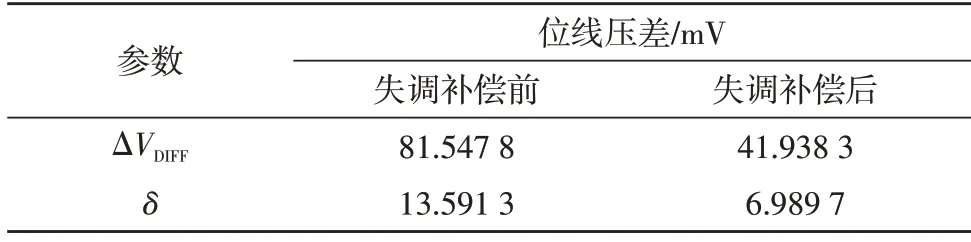

表3 所示为失调补偿前后位线压差及压差分布的δ对比情况。

表3 失调补偿前后位线压差对比

失调补偿前ΔVDIFF的理论值为94.86 mV,可以看到,仿真测量值为81.547 8 mV,灵敏度为110 mV,仿真测量值和灵敏度近似。改进后SA 的仿真测量压差为41.938 3 mV,灵敏度为50 mV,两者基本一致。

版图后仿结果表明,δ较前者减少了≈48.57%,仿真测量结果符合预期目标。

3.3 PVT仿真

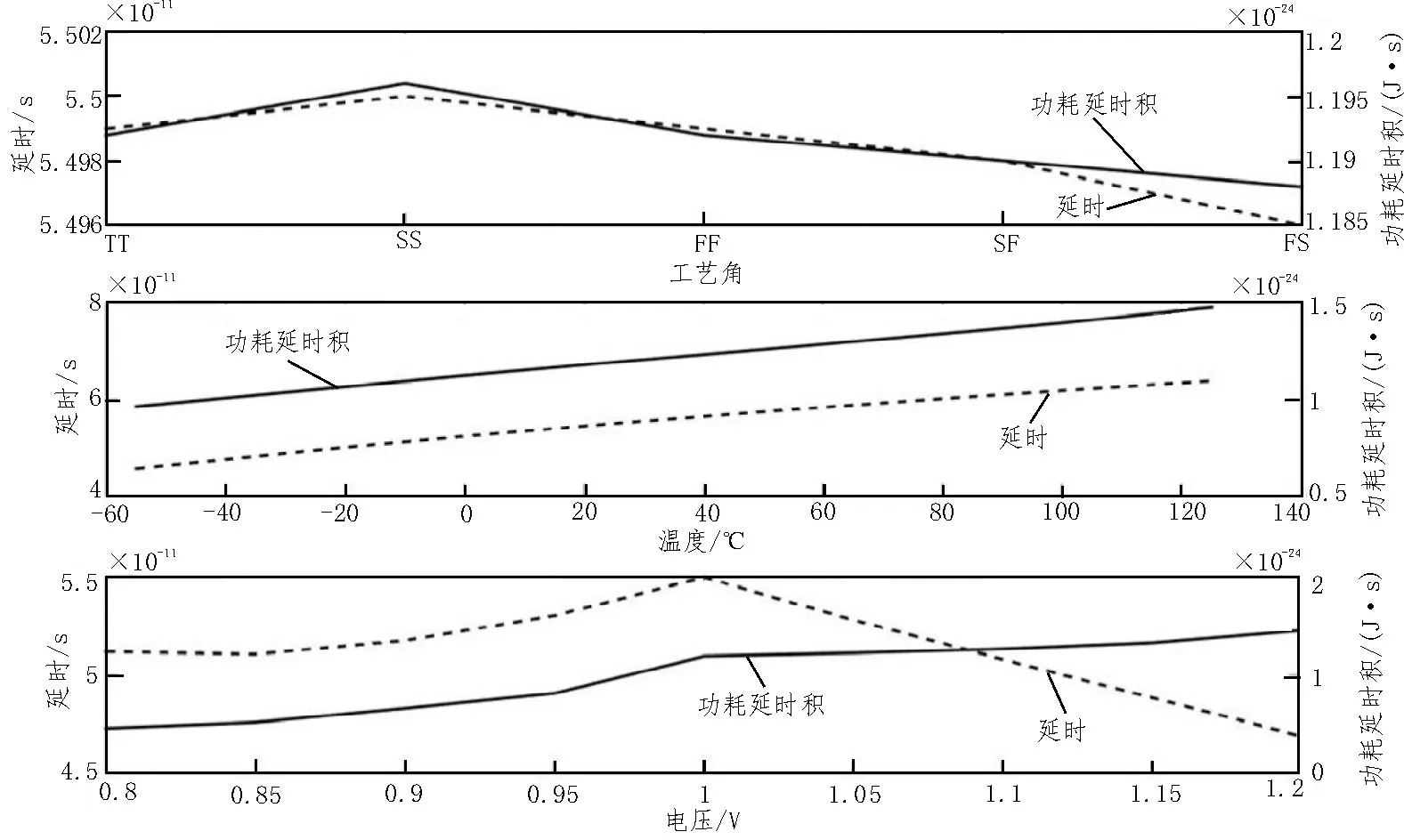

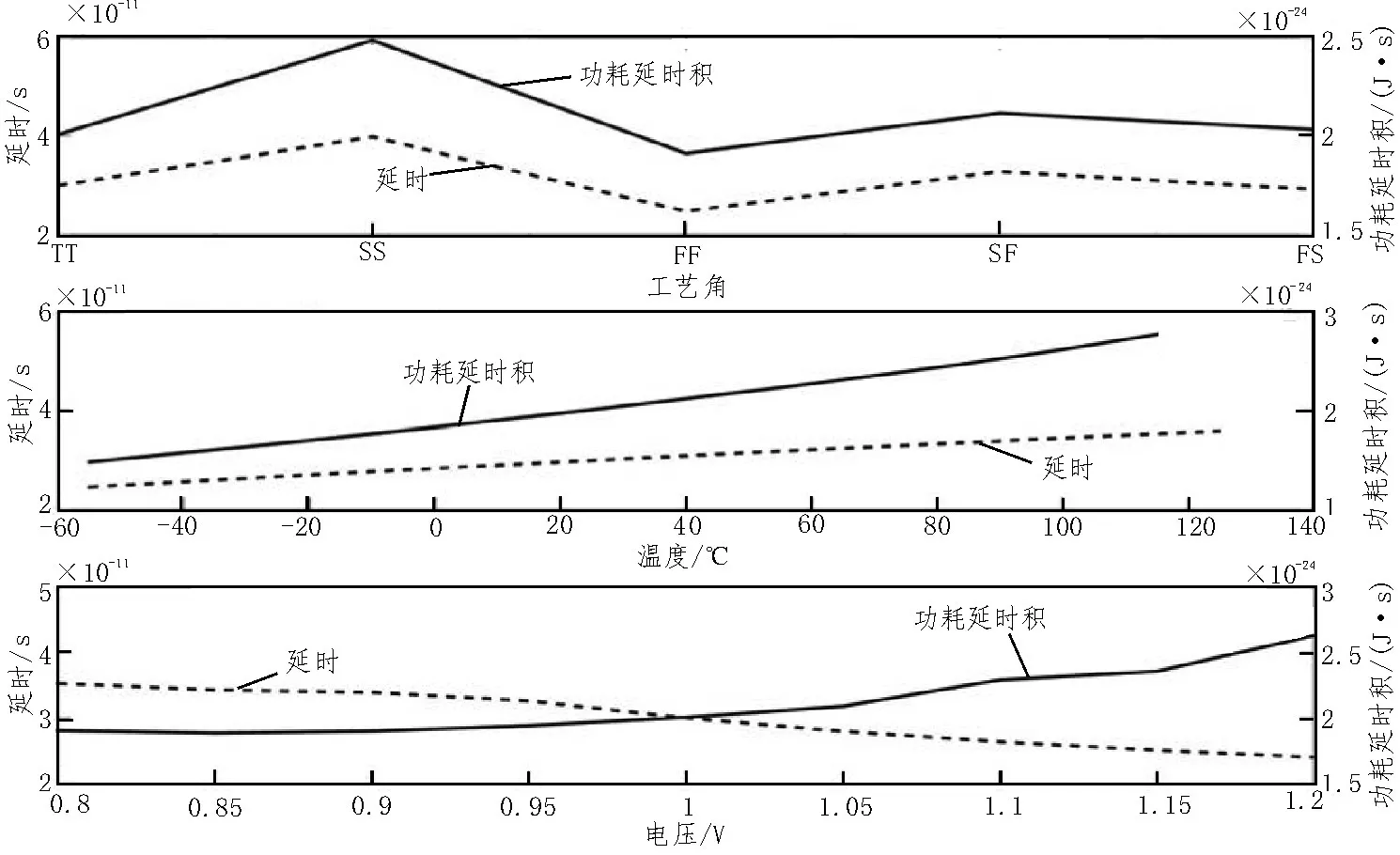

图5、图6 所示分别为灵敏放大器补偿前后延时和功耗延时积(Power-Delay Product,PDP)受PVT 影响的关系图。仿真结果表明,失调补偿前后SA 的延时和功耗延时积基本保持稳定,随着温度的上升,两者均有少量的上升;随着供电电压的上升,延时下降,延时功耗积上升。

图5 失调补偿前PVT仿真结果

图6 失调补偿后PVT仿真结果

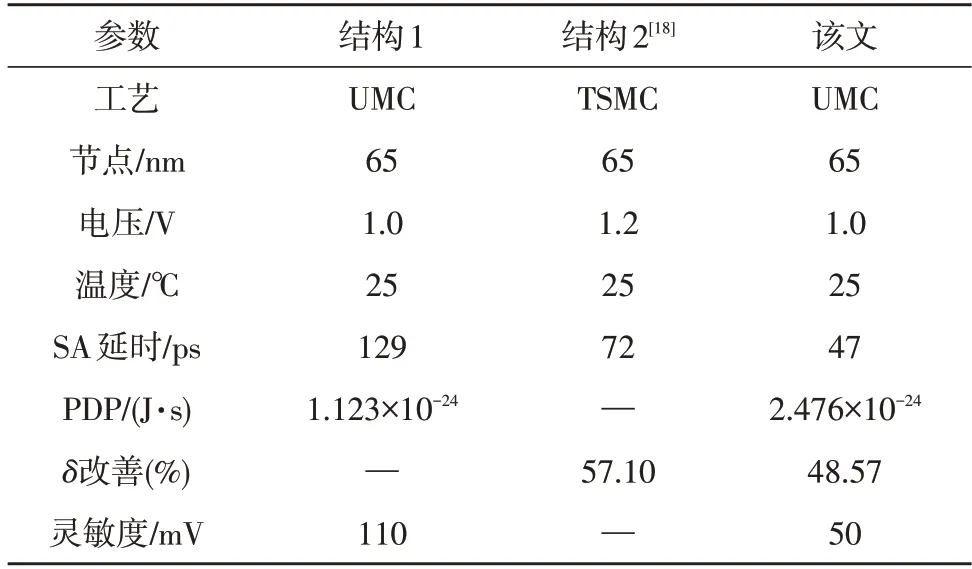

表4 所示为改进后的SA 与其他文献中结构的参数对比,可以看出,该设计的SA 通过改善σ,降低了延时,达到了设计目标。

表4 不同结构的参数对比

4 结论

该文通过调研不同类别的SRAM 和灵敏放大器,分析了影响灵敏放大器性能的因素,通过推导和分析失调电压来源,提出了一种针对锁存器型SA 的改进电路,利用电路中的冗余结构,给SA 增加了两条电流校准支路,位线上增加了一级MUX。在1.0 V工作电压、25 ℃、TT Corner下,SA 的灵敏度为50 mV,数据读出延时为139.4 ps,PDP 为2.006×10-24J·s。仿真结果表明,灵敏放大器的灵敏度、数据读出速度、可靠性相较于补偿前的结构,均得到了提升。