一种应用于CMOS传感器的宽增益范围PGA设计*

2022-12-12杨煌虹陈翰民冯秀平曾伟

杨煌虹,姚 佳,陈翰民,冯秀平,曾伟,武 华

(赣南师范大学 物理与电子信息学院,江西 赣州 341000)

近年来,随着CMOS工艺技术的快速发展,许多CMOS传感器逐渐朝着低噪声、宽增益的方向发展.在CMOS图像传感器领域,模拟前端一般为CDS-PGA-ADC结构[1],在CMOS图像传感器输出与ADC输入之间增加一个PGA,通过它将CMOS图像传感器的输出信号调整到ADC的最佳输入范围,能提高CMOS图像传感器性能并扩展其功能[2],因此设计一个具有宽增益范围的PGA具有良好的应用前景.

传统PGA以单级运放组成的开环结构为主,此类结构具有良好的稳定性和响应速度,但只能实现较小范围的增益控制.魏聪[3]采用单级cascode结构运算放大器作为其主运算放大器,反馈增益调节采用可编程开关电容阵列结构,电路具有较快的响应速度和稳定性,但最高只能实现8倍增益的PGA系统设计.Amico[4]提出了一种带源极负反馈的共源级为主运放的可变增益放大器,具有低功耗和高精度等优点,但也只能实现0~20 dB的增益范围,且具有不可忽视的噪声干扰.杨江[5]所提出的可编程增益放大器基于带有并联负反馈的开环结构,可以在较低功耗下获得较大的带宽,实现了0~60 dB的增益范围,但结构复杂,控制电路繁琐,不易于集成.

本文设计的PGA采用以PMOS输入的折叠式共源共栅结构和共源结构的二级级联,通过采用二进制编码方式控制反馈电阻变化的闭环结构,实现了以6 dB为步进,0~60 dB的增益范围,且结构简单,具有良好的增益精度,可应用于CMOS传感器模拟前端.

1 系统框架及电路实现

本文设计的可编程增益放大器将输入信号通过比较器电路,控制传输门开关来改变反馈电阻值,实现6 dB步进、0~60 dB的增益控制.其中,由于差分对的不完全匹配导致输出端的不完全对称所引起的直流失调问题,在反馈网路中添加直流失调补偿模块来进行失调电压的补偿.另外,设计了LDO电源模块来供应其它模块的正常工作.总体系统框图如图1所示.

图1 系统总体框图

由于设计的增益范围为0~60 dB,如果采用单一PGA来实现,则反馈结构极其复杂,且开关电路也较为繁琐[6],本文采用两级PGA分别实现0~30 dB的增益范围.通过设计具有一定放大倍数的运放结构进行反馈控制,从而实现0~60 dB,6 dB步进的增益范围.

1.1 运算放大器的设计

运放是组成PGA最基本的模块[7],为了使PGA的反馈系数更准确表达其放大倍数,需要设计足够大增益的运算放大器;另外,考虑到噪声干扰和输出摆幅的问题,选择以PMOS为输入的折叠式共源共栅电路加上共源级放大电路组成二级运放,提供足够高的增益和理想的输出摆幅.由于折叠式共源共栅结构存在多个偏置电压,使得共模电平难以确定,运放难以正常工作,因此引入共模反馈来稳定共模信号,使得电路更容易偏置[8].另外,对于二级运放容易因电路两个极点相隔太近,导致系统不稳定,因此采用了密勒补偿来维持电路的稳定.设计的运放电路如图2所示.

图2 运放电路图

对于运算放大器,输出阻抗是衡量放大能力的一个重要参数.本设计中的运放结构以提升输出阻抗为目的,根据对折叠式共源共栅运放进行半边等效电路分析,可以得出:

Rout=(Rup‖Rdown)

(1)

Rup=(gm7+gmb7)ro7ro9

(2)

Rdown=[(gm3+gmb3)ro3(ro1‖ro5)]

(3)

联立(1)(2)(3)得,

Rout=[(gm3+gmb3)ro3(ro1‖ro5)‖[(gm7+gmb7)ro7ro9]]

(4)

可知其输出阻抗非常大,使得运放电路具有可观的增益.

1.2 增益调节模块

运放增益级采用双输入双输出的闭环结构,通过二进制编码方式控制反馈电阻的变化来改变增益,增益调节示意图如图3所示.

图3 增益调节示意图

1.2.1 传输门开关设计

设计的PGA采用控制开关改变反馈电阻实现可变增益.开关电路可由单个MOS管或传输门构成,考虑到单个晶体管对输入信号范围有一定限制,且导通电阻会随输入电压的变化而变化.本设计采用CMOS传输门结构,利用PMOS和NMOS的导通特性从而实现较低的导通电阻,且满足大范围输入电压的要求[9].通过利用反相器与传输门电路的搭配,完成一个较大输入电压范围的开关电路,电路结构如图4所示.当VC为高电平时,NMOS和PMOS导通,其等效输出电阻

图4 传输门电路图

Rout=Ron(M6)||Rop(M7)=

1/[μnCox(W/L)M6(VDD-VTH,M6)-(μnCox(W/L)M6-μpCox(W/L)M7)Vin-μpCox(W/L)M7|VTH,M7|]

(5)

通过设计晶体管M6和M7满足μnCox(W/L)M6=μpCox(W/L)M7时,使得导通电阻Rout与不受输入Vin的影响.另外,设计晶体管尺寸满足(W/L)M7=2 (W/L)M6的要求,使得反馈电阻为千欧数量级时,其导通电阻可忽略不计.

1.2.2 反馈电阻网络设计

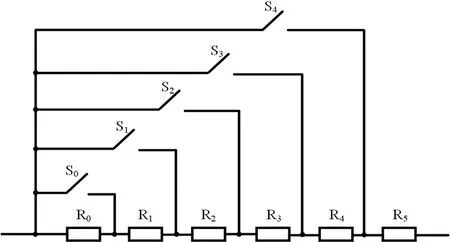

由于需要实现0~60 dB的宽增益范围以及6 dB的增益步进,考虑到对增益控制的易操作性,选择使用分压式开关来进行控制.反馈电阻网络结构如图5所示,设计的反馈电阻R0~R5的阻值分别为160 kΩ、80 kΩ、40 kΩ、20 kΩ、10 kΩ、10 kΩ.以10 kΩ电阻作为输入电阻,通过控制开关来调节反馈电阻的总阻值,从而实现0~30 dB,6 dB步进的增益.当没有开关导通时,增益最大达到30 dB,随着开关从S0~S4逐个导通,增益从30 dB以6 dB为步长依次降低,直到所有开关均导通时,有最小增益0 dB.

图5 反馈电阻网络结构图

1.3 直流失调补偿模块设计

由于工艺误差会带来输入差分对的失配,导致直流失调问题,通过引入DC-OC模块进行补偿.传统补偿方法主要有交流耦合、开关电容结构、低通负反馈和数字校准几种直流失调的补偿措施[10].通过对总体电路的频率特性影响以及设计复杂度的综合考虑,采用低通负反馈结构来实现直流失调补偿.DC-OC模块电路图如图6所示,在模拟信号的输出到输入之间加入低通滤波器,形成负反馈,再与输入管的低频信号相减,整个电路呈现出高通特性,对直流和低频信号进行衰减,从而减小输入端的直流失调量.

图6 DC-OC模块电路图

在输出到输入之间引入低通滤波器,形成负反馈.低通滤波器的截止频率很低,将输出端的低频和直流信号通过低通滤波器取出,再经过跨导单元放大后,在输入管经过纠正电阻进行低通信号的衰减,从而减小输入端的直流失调量[11].其中,跨导单元由OTA组成;纠正电阻阻值越大,直流失调的补偿能力越强,但带来的热噪声越大.另外,为了不影响有用信号的传输,高频特性需要有很低的高通截止频率[12].但高通截止频率太低会导致直流失调电路的建立时间越长,环路的响应时间很慢,即低通负反馈消除直流失调会存在高通带宽和环路响应速度的折中.

1.4 比较器设计

比较器是进行逻辑控制的重要电路,将一个输入信号与参考信号做比较,经过电路转换成二进制信号,输出比较器的处理结果.本文利用电阻分压式结构与参考电压进行比较的输出结果来控制开关,采用静态开环比较器即可.通过综合考虑比较器的增益,失调电压和精度等性能,设计的比较器电路如图7所示,采用以PMOS差分对输入的OTA和共源级的二级级联结构来实现电压比较的功能.

图7 比较器电路图

1.5 LDO电源模块设计

为满足较大输入电压波动的应用领域和稳定合适的工作电压,设计了低压差线性稳压器(low dropout regulator,LDO),LDO电路如图8所示,通过负反馈来维持稳定的输出电压.

图8 LDO模块结构图

考虑到等效输入噪声以及输出摆幅的影响,采用PMOS充当功率管.另外,由于功率管的栅极与漏极作为电路的两个极点且频率相差较小,则引入密勒补偿,增大主极点,拉低输出极点.其中,

Vip=Vout[R1/(R0+R1)]

(6)

当输出电压Vout变化引起Vip变化时,通过将Vip与Vref进行比较,进而控制功率管的栅极,改变MOS管的导通电阻,进而调整压降以控制输出电压的稳定.即

Vout降低→VR1降低→Vip降低→VGS0增大→Ids0增大→Vout增大

2 仿真验证及结果分析

2.1 比较器输入输出特性仿真

通过采用TSMC 0.18μm工艺库,使用Cadence Spectre对电路进行仿真.对比较器进行DC直流仿真,设定参考电压为1.8 V,对输入电压从0~3.3 V进行直流扫描,仿真结果如图9所示.

图9 比较器输入输出仿真图

当输入电压小于1.78 V时,输出为低电平,误差约为0.02 V;当输入电压大于1.84 V时,输出为高电平,误差约为0.04 V.可以看出,比较器能实现输入电压与参考电压的比较功能,从而控制反馈环路的开关.此外,比较器的输出误差范围较小,传输特性接近于理想的传输特性,可以满足设计要求.

2.2 DC-OC失调补偿仿真

对直流失调补偿模块进行AC仿真,在引入反馈网络后,当PGA的设计增益为18 dB档位时,波特图如图10所示.可以看出,DC-OC模块实现了低频直流信号的衰减,对0~100 hz的低频信号具有明显的抑制效果,可以实现直流失调信号的补偿,功能满足设计要求.

图10 加入反馈的DC-OC波特图

2.3 增益控制仿真

通过采用两级30 dB级联实现60 dB,6 dB步进的PGA,建立好静态工作点后,对整体模块进行AC仿真,通过对输入电压进行扫描,可以得到11个增益值,其输出结果如图11所示.可以看出,增益步进稳定在6 dB左右,且增益误差小于调节精度的1/2LSB,实现了设计功能.

图11 增益控制模块仿真图

2.4 LDO性能仿真

本设计的LDO模块,为整体电路的各个模块提供稳定的工作电压,仿真结果如图12所示.对LDO电路进行瞬态响应仿真,最大过冲电压为242 mV,最低跌落电压为75 mV,输出电压能稳定在3.035 V,具有良好的性能指标,满足设计要求.

图12 LDO输入输出仿真图

3 结论

设计一种应用于CMOS传感器模拟前端的宽增益范围PGA,基于TSMC 0.18 μm工艺,使用Cadence Spectre对电路进行了仿真验证.设计的比较器电路的参考电压为1.8 V,当输入电压小于1.78 V时,输出为低电平,误差为0.02 V;当输入电压大于1.84 V时,输出为高电平,误差约为0.04 V,电路具有良好的精度;DC-OC模块能够实现直流失调量的抑制.另外,LDO能够为其它模块提供3 V的稳定工作电压,满足实际需求.设计的PGA实现了在0~60 dB范围内以6 dB为步进的增益变化,且增益误差小于调节精度的1/2LSB.