碳化硅单晶位错研究进展

2022-12-10张家鑫陈秀芳谢雪健杨祥龙胡小波徐现刚

张家鑫,彭 燕,陈秀芳,谢雪健,杨祥龙,胡小波,徐现刚

(山东大学新一代半导体材料研究院,济南 250100)

0 引 言

碳化硅(SiC)单晶作为第三代宽禁带半导体材料,具有许多优良的性质,表1[1-3]是对第一、第二以及第三代半导体典型材料基本性质的对比:相比于第一、第二代半导体材料,SiC的禁带宽度宽、热导率大[4-5]、载流子迁移速度快、临界击穿场强强[6]、抗辐射能力强、键合能高、热膨胀系数小、硬度仅次于金刚石、抗氧化[7]、热稳定性和化学稳定性极好,是目前最重要的第三代宽禁带半导体材料之一。基于这些优良的性质,SiC被广泛应用于太阳能[8]、航空航天、军工、汽车、信息通信雷达、照明等领域。随着应用的扩展和深入,这对SiC单晶材料的质量提出了很高的要求。

近10年来SiC材料研发产业的重点集中在尺寸扩大、缺陷降低和电学可控等多个方面,控制和降低SiC中的缺陷是其中重要工作之一。在SiC单晶中,常见的缺陷有:位错[9-11]、多型夹杂[12-13]、微管[14-19]、晶面弯曲[20]、小角度晶界[21-22]、异质包裹物[23]等。根据缺陷在三维晶格空间的几何特征将SiC晶体缺陷分为三维、二维、一维、零维缺陷。三维缺陷如碳夹杂物、硅滴夹杂物、多型、六边形孔洞和微管等缺陷;二维缺陷如晶界、孪晶界、堆垛层错等缺陷;一维缺陷如螺位错(TSDs)、刃位错(TEDs)、基平面位错(BPDs)、混合位错;零维缺陷如硅空位、碳空位、碳硅反空位、外来取代原子、填隙碳原子等造成的缺陷。除去经典分类,Sudarhan等[24]根据缺陷的产生原因,把SiC晶体缺陷分为两类:第一类是从籽晶继承并繁衍的缺陷,包括沿晶体生长方向延展的TEDs、TSDs、微管(MP)等缺陷;第二类是晶体生长时产生的热应力引起的塑性变形、晶核取向错误、第二相硅和碳夹杂物等导致“意外”成核的缺陷。这种分类的出发点是明确缺陷产生原因,有助于研究人员针对不同原因采取不同措施降低缺陷。Chen等[25]根据缺陷在晶体中的位置将SiC晶体缺陷分为两类:第一类是晶体内缺陷;第二类是晶体表面或近表面缺陷。明确了SiC加工过程引入的划痕、亚损伤等也会引入缺陷,这一发现值得单晶及外延生长中关注。

缺陷会严重阻碍以SiC单晶为主要材料的器件的发展和应用,例如一维位错缺陷会造成电子设备的劣化和失效[26],影响高阻断电压和低导通电阻的功率器件的应用,表2[25]是SiC位错对不同器件的影响情况汇总,位错会使金属-氧化物半导体场效应晶体管(MOSFET)[27-29]、肖特基势垒二极管(SBD)[30-32]、p-n结、绝缘栅双极型晶体管(IGBT)的栅极氧化膜可靠性(gate oxide reliability)、载流子寿命(τ)、击穿电压(VB)下降,导通电阻(Ron)和漏电流(Ileak)增大,也会导致双极性功率半导体元件正向特性退化[33-34]。

因此降低SiC单晶中的位错密度仍是待解决的重要问题之一。本文将对SiC单晶中位错的形成原因、检测技术手段、减少方法、现阶段位错密度水平进行总结归纳,并提出了SiC单晶需要继续突破和发展的方向。

表1 Si、GaAs、SiC、金刚石半导体材料的基本性质[1-3]Table 1 Basic properties of Si, GaAs, SiC and diamond semiconductor materials[1-3]

表2 SiC位错对不同器件的影响[25]Table 2 Impact of SiC dislocations on different devices[25]

1 位错及位错的形成原因

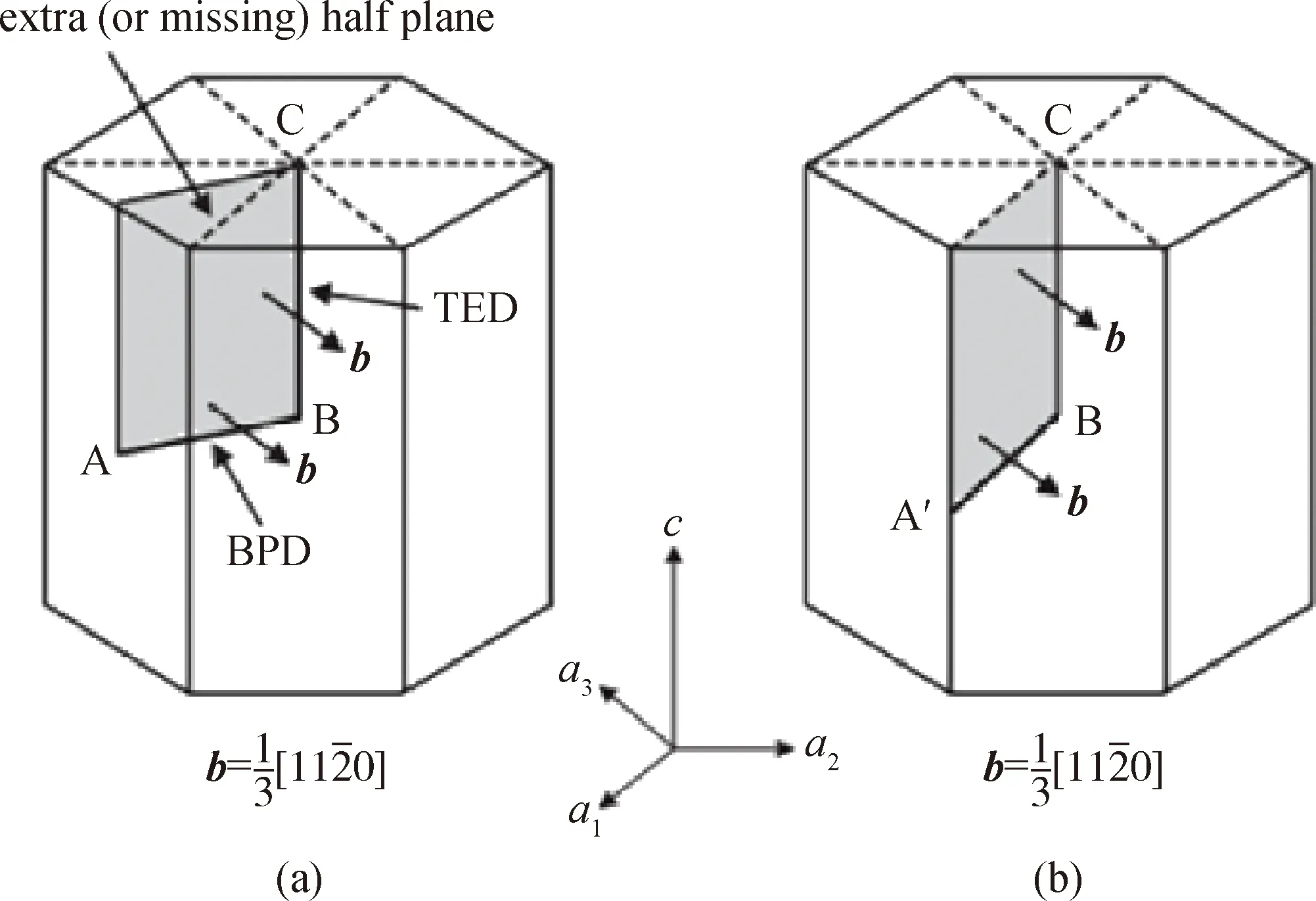

位错是晶体内部的微观缺陷,是原子局部的不规则排列造成的,发生在晶体已滑移部分和未滑移部分的分界线处[35-37]。在SiC单晶中,常见的位错有TEDs、TSDs、BPDs[38]。

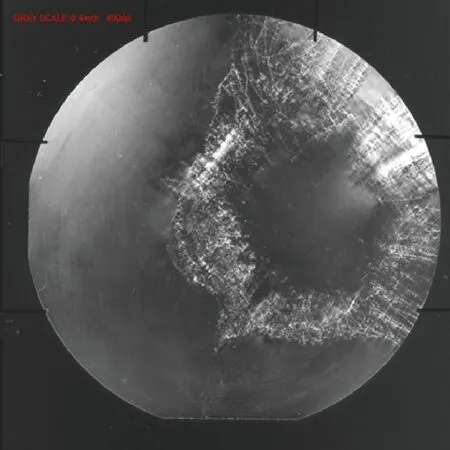

MP是指在SiC单晶中直径在0.1~10 μm的空心管道。图2为SiC衬底未腐蚀之前光学显微镜下的MP形貌。依据Frank的MP形成机理[46],MP是具有较大Burgers矢量的空心螺位错,又叫超级螺位错,MP的直径D与Burgers矢量b之间满足关系式:

(1)

式中:D为MP的直径(m);μ为晶体的剪切模量(Pa);b为Burgers矢量(m);γ为晶体的比表面自由能(J·m-2)。MP在SiC单晶中普遍存在,一般沿晶体生长的<0001>方向拓展。形成MP的原因有三种[47]:一是在晶体生长过程中,其他缺陷如包裹物、层错、多型界面诱导产生;二是籽晶中MP延伸到新形成的SiC晶体中;三是晶体本身的MP发生合并和分解产生新的MP。

图1 螺位错结构示意图[39]Fig.1 Schematic diagram of screw dislocation structure[39]

图2 腐蚀之前光学显微镜下的微管形貌Fig.2 Micropipes morphology under optical microscope before corrosion

图3 TED和BPD结构示意图。(a)引入SiC晶体的多余(或缺失)半平面示意图;(b)TED和BPD的典型构造[39]Fig.3 Schematic diagram of edge dislocation and base plane dislocation structure. (a) Schematic illustration of an extra (or missing) half plane introduced into a SiC crystal; (b) typical configuration of threading edge and basal plane dislocations[39]

表3 TSD、TED、BPD的Burgers矢量及位错线方向汇总Table 3 Burgers vector and dislocation line direction of TSD, TED and BPD

2 SiC位错检测方法

为了生长出高质量的SiC晶体,需要确定籽晶的位错密度和分布情况来筛选出优质的籽晶。此外,研究位错在晶体生长过程中的变化也有利于生长工艺的优化。掌握衬底位错密度及分布对于研究外延层中的缺陷也十分重要。因此,通过合理的技术对SiC晶体的结晶质量、缺陷进行表征分析对加快实现高质量大尺寸SiC的生产制备是必要的。SiC缺陷的检测方法[54]可分为破坏性的方法和非破坏性的方法。破坏性的方法有湿法腐蚀[55-60]、透射电子显微镜(TEM)[39,61];非破坏性的方法有阴极荧光(CL)无损表征[39,62]、X射线形貌(XRT)技术[39,49,52,63-65]、光致发光(PL)[66-67]、光应力技术、拉曼光谱[68]等。

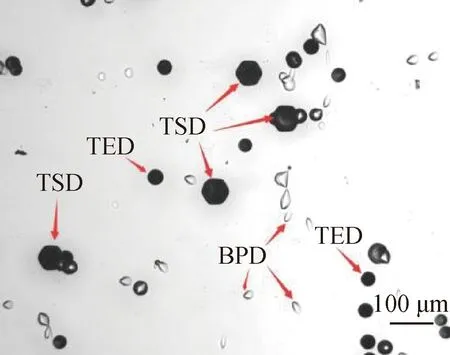

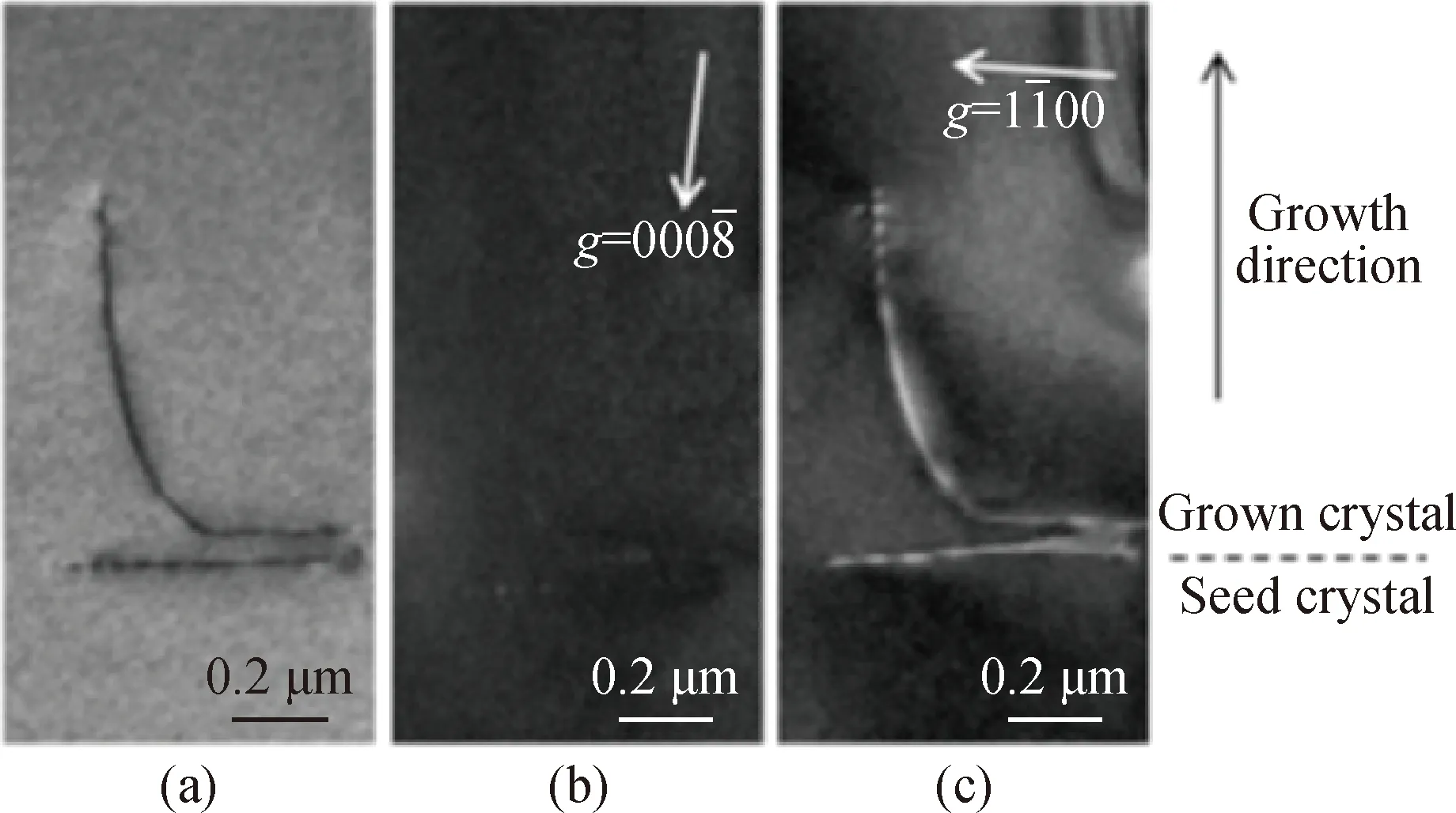

湿法腐蚀是最常见的研究位错的方法,由于需要在高温熔融碱中进行腐蚀[57-59],该方法具有极强的破坏性。腐蚀后的SiC晶片用显微镜观察,可以看到形状大小不同的腐蚀坑,一般地,Si面腐蚀坑的形状有3种:近圆形、六边形、贝壳形。分别对应TEDs、TSDs、BPDs缺陷[60],图4为腐蚀坑形貌图,随着检测设备的发展,研制的晶格畸变检测仪、激光共聚焦显微镜、位错检测仪等都可全面直观地检测出腐蚀片的位错密度和分布情况。透射电子显微镜可以在纳米尺度上观察样品的亚表面结构,也可以观察到SiC中的BPDs、TEDs和SFs等晶体缺陷,如图5所示为籽晶和生长晶体界面处位错的TEM照片[61]。CL和PL可无损地检测晶体亚表面的缺陷,如图6、图7所示,但相比于PL,CL可测量的波段范围更宽,宽带隙半导体材料可得到

图4 TSDs、TEDs、BPDs的腐蚀坑形貌图Fig.4 Corrosion pit morphology of TSDs, TEDs and BPDs

图5 不同衍射矢量下,籽晶和生长晶体界面处位错的TEM照片。(a)明场;暗场;暗场[61]Fig.5 TEM images of dislocation at interface between seed crystal and growth crystal with different diffraction vectors. (a) Bright field;

图6 位错在CL图像中的原理[62]Fig.6 Dislocations in CL image[62]

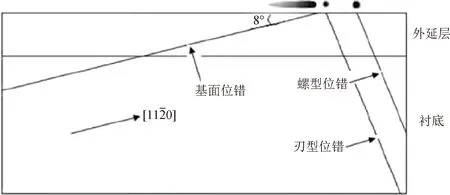

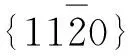

有效的激发[39]。X射线形貌术是一种强有力的无损技术,可以通过衍射峰宽表征晶体缺陷,基于同步辐射的单色束X射线形貌图(synchrotron monochromatic beam X-ray topography, SMBXT)利用高度完美的参考晶体反射获得单色化X射线,在样品的反射曲线不同部位拍摄一系列形貌图,不同的区域显示不同的衍射强度,从而可测量不同区域的点阵参数和点阵取向的差异[63],位错的成像结果对研究位错的形成具有重要作用,如图8(b)、(c)为位错的X射线形貌图[49,65]。光应力技术可以对晶片中缺陷的分布进行无损检测,图9为光应力技术对SiC单晶衬底的表征。拉曼光谱也是一种非破坏性的亚表面检测手段,Feng等[68]利用拉曼散射法发现~796 cm-1处为MP、TSDs和TEDs敏感峰位,如图10所示。

图7 PL法检测位错。(a)4H-SiC的TSD、TMD、TED、无位错区测得的PL光谱;(b),(c),(d)TED、TSD和TMD的光学显微镜图像与PL强度映射图[67];(e)BPDs的PL图像Fig.7 Dislocations detected by PL method. (a) PL spectra measured in TSD, TMD, TED and dislocation-free regions of 4H-SIC; (b), (c) and (d) optical microscope images and PL intensity maps of TED, TSD and TMD[67]; (e) PL image of BPDs

图8 XRT法检测位错。(a) XRT的原理示意图[52];(b)生长界面处穿线位错的XRT图像[65];(c)BPD的SMBXT图像[49]Fig.8 Dislocation detection by XRT. (a) Schematic diagram of XRT principle[52]; (b) XRT image of threading dislocations at the growth interface[65]; (c) SMBXT image of BPD[49]

图9 光应力技术对SiC单晶衬底的表征Fig.9 Characterization of SiC single crystal substrates by photostress technique

图10 MP、TSD、TED的拉曼散射峰位图[68]Fig.10 Raman scattering peak bitmap of MP, TSD and TED[68]

3 降低位错的技术方法及位错的优化水平

在观察位错的基础上,结合产生位错的影响因素,即生长条件、生长界面、籽晶等,各产业和研究单位在降低位错密度方面也做了诸多的努力。首先,可通过优化生长条件和生长设备降低位错密度。在采用PVT法生长时,增加生长气体流量,避免N2的掺杂,使TEDs密度下降[69]。在籽晶托开沟槽,填充与石墨热导率不同的材料,或者在籽晶托上镀与石墨热导率不同的薄膜,来调节籽晶表面温度场分布,可达到降低穿透性位错密度的目的[70]。

其次,可通过优化籽晶和生长晶体的界面来降低位错密度。在1 400 ℃下采用H2刻蚀籽晶,完全去除亚表面损伤,籽晶表面的凹坑密度相比于机械抛光法的凹坑密度下降一个数量级,位错密度也有所下降[71]。或在SiC衬底上外延生长多个周期的低掺杂浓度的复合缓冲层,并对每个缓冲层进行高温H2刻蚀,利用界面高温处理及掺杂诱导引入多个界面,促进BPDs缺陷向TEDs缺陷的转化,有效降低外延层中的BPDs缺陷密度[72]。

目前,100 mm SiC单晶中的TSD密度从103cm-2[77]逐渐降低到670 cm-2,总位错密度可达到1 060 cm-2[78],150 mm SiC单晶中TSDs密度控制在149 cm-2[79-80],Cree公司生长的150 mm的晶体,BPDs密度达112 cm-2,TSDs平均密度在230 cm-2以下[81],Ⅱ-Ⅵ Incorporated生产的200 mm N型SiC衬底中总位错密度为3 885 cm-2,BPDs密度为951 cm-2,TSDs密度为716 cm-2[82],代表了现阶段研发的最高水平。

图11 RAF过程示意图。(a)RAF法生长的3个步骤;(b)上侧视图,显示步骤1和步骤2中籽晶和生长晶体{0001}晶面不规则[75]Fig.11 Diagram of RAF process. (a) Three steps of RAF growth; (b) top side view, shows irregular lattice surface of seed crystal and growth crystal {0001} in steps 1 and 2[75]

4 结语与展望

以SiC为代表的第三代半导体材料具有优异的物理性质,在电力电子器件等方面的应用空间和市场需求逐渐增加,随着生长工艺的改善,SiC单晶位错密度呈快速降低趋势,能否在目前位错密度的基础上再降低一个数量级是下一阶段的目标。同时,目前国产的SiC衬底的位错密度相比于国际主流的商用公司如Cree、Ⅱ-Ⅵ等仍有一定差距,研发和制造国产的高质量低缺陷密度的大尺寸SiC单晶衬底也是如今迫切需要解决的问题。