基于PXIe的EPS试验台多通道数据采集系统设计

2022-11-02卢俊杰郑永军胡晓峰

卢俊杰,罗 哉,郑永军,郭 斌,2,胡晓峰

(1.中国计量大学,浙江杭州 310018;2.杭州沃镭智能科技股份有限公司,浙江杭州 310018)

0 引言

随着汽车电子技术的日益成熟,汽车电动助力转向系统(electric power steering,EPS)的装车率越来越高,EPS系统是一种使用电机提供辅助扭矩的新型汽车动力转向系统。无人驾驶汽车以及各种驾驶辅助设备,都在一定程度上受EPS系统的发展影响[1]。

EPS的研发需要获取重要的技术参数,通过搭建EPS试验台进行仿真实验相比于实车实验可以缩短产品的开发周期,节约开发成本。EPS试验台的测试系统包括工控机、数据采集卡及传感器等,如回正性能试验中需要对输入及输出端扭矩、助力电机的电压和电流等信号进行监测、分析和处理[2]。因此EPS试验台对数据采集系统的采样精度、通道数量、缓存容量和传输速率等提出了较高的要求。目前国内EPS试验台中数据采集系统多采用NI公司的产品如PCI-6259、PCIe-6320,以及研华公司的产品如PCI-1710等,该类板卡有通用性强、成熟度高等优点,但是价格较高[3-4]。

针对以上问题,设计了一款基于PXIe(PCIe exte-nsion for instrumentation)接口和FPGA控制的32通道数据采集系统,具有成本低、可靠性强、大容量高速传输的特点[5-8]。PXIe结合了PCIe的电气总线特性与Compact PCIe的机械规范,并增加了专门的同步总线、环境测试规范等,广泛应用于航空、汽车生产及工业测试等领域[9]。

1 系统方案设计

根据性能指标需求,整个系统架构由信号调理电路、输入选择电路、ADC数据采集模块、FPGA芯片及其外围电路、DDR3数据缓存模块、电源管理系统、PXIe连接器和上位机软件组成,系统总体设计框图如图1所示。其中PXIe连接器为PXIe规范定义的XJ3与XJ4连接器,XJ3连接器由2对PCIe高速差分数据信号线以及100 MHz参考时钟、热插拔检测、复位信号线等组成;XJ4连接器提供工控机机箱背板的12 V电源经过DC-DC转换和稳压芯片及其外围电路变换为±15 V、5 V、3.3 V、2.5 V等电源网络为其他模块供电。

图1 系统总体设计框图

系统的基本工作流程为:传感器输出的模拟信号通过背板连接器输入信号调理电路,每路模拟信号经过偏移衰减、差分转单端和抗混叠滤波处理后送入4块8∶1多路复用器组成的输入选择电路;然后FPGA通过MUX控制总线对多通道模拟信号轮询切换将数据送入ADC数据采集模块;其次FPGA完成数字信号的接收和FIR滤波处理,并根据需要把采集的数据存储到用户逻辑侧AXI外设寄存器,以备PXIe进行少量采样数据上传,寄存器同时对工控机下发的采样配置参数保存,或者把数据传输至DDR3存储器中大容量缓存;最后,通过PXIe接口将数据送入工控机进行处理和显示。

2 硬件电路设计

2.1 ADC数据采集模块

本系统使用14 bit ADC芯片AD9240,其主要功能和指标为:高采样速率,最高达10 MSPS;低功耗,单一的+5 V电源供电,功耗仅285 mW;低噪声,积分非线性误差为0.5 LSB,微分非线性误差为1 LSB。AD9240的电压转换范围由参考电压VREF决定,如式(1)所示:

-VREF≤VINA-VINB≤VREF

(1)

式中:VINA和VINB为施加在芯片引脚上的差分电压。

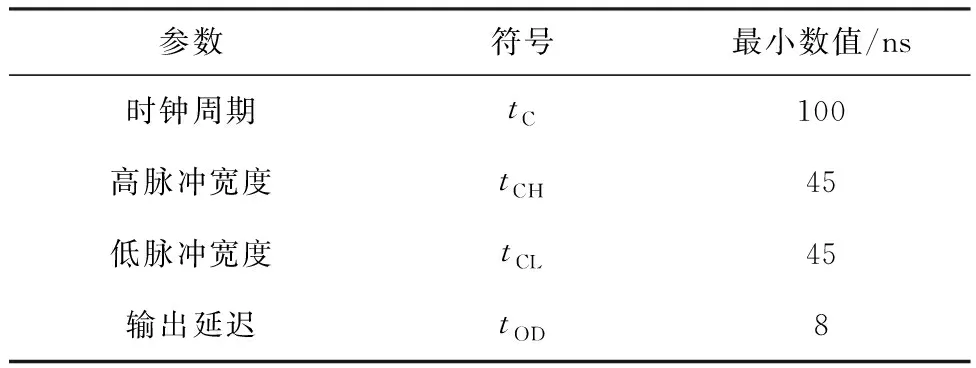

AD9240内部参考电压温度稳定度可以满足使用要求为20×10-6V/℃,因此本设计将SENSE和VREFCOM端口相联,得到内部参考电压VREF为2.5 V。AD9240的转换速率由采样时钟决定,每个时钟上升沿处采集的模拟信号会在延迟3个时钟周期后输出,AD9240时序图如图2所示,表1为时序约束。时钟稳定性对采样精度有很大影响,因此采样时钟由FPGA的全局时钟资源优化后提供,同时由于FPGA的BANK电压为3.3 V,采用高速逻辑门芯片实现5 V电平转换。

图2 AD9240时序图

表1 时序约束

2.2 信号调理电路

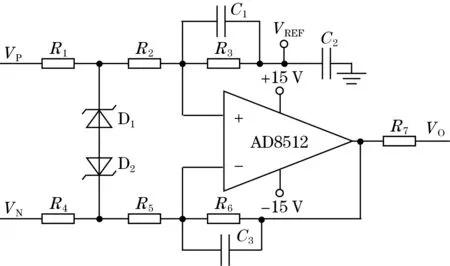

系统指标要求差分输入电压范围为±20 V,因此需要在模拟信号进入ADC之前进行信号调理,信号调理电路如图3所示。

图3 信号调理电路原理图

首先,电容C1、C3组成一阶RC低通滤波器,限制到达ADC输入端的带宽外噪声,同时采用2个相反方向串联的稳压二极管保护运放输入免受任一方向的过压影响。其次,AD8512是一款高精度、低噪声、高带宽的JFET运算放大器,在供电电压为±15 V的情况下,具有增益带宽积8 MHz,CMRR最小值86 dB及输入失调电压0.08 mV和输入偏置电流20 pA等特性。基于AD8512组成差分放大电路,当R1=R4,R2=R5,R3=R6,C1=C3时,经过计算可得该电路的传递函数为

(2)

式中:VP和VN为差分输入电压;VO为调理电路输出电压。

电路增益为R3/(R1+R2),差分输入阻抗为2(R1+R2),通过合理选择阻值使得输入模拟电压转为在ADC的电压转换范围内,同时与信号源输出阻抗做匹配,本设计中R1=47 kΩ,R2=1 MΩ,R3=127 kΩ。式(3)为共模抑制比计算经验公式。

(3)

式中:G为电路增益;ε为电阻容差;α为比例参数。

当参数α取4时计算最小共模抑制比,计算可得电阻容差ε为0.1%。数据采集卡一般采用多块ADC芯片方案,随着通道数的增加,成本也越高,本设计采用单块ADC芯片,当增加通道数量时,只需增加调理电路和多路复用器,具有低成本的扩展性。

3 FPGA逻辑设计

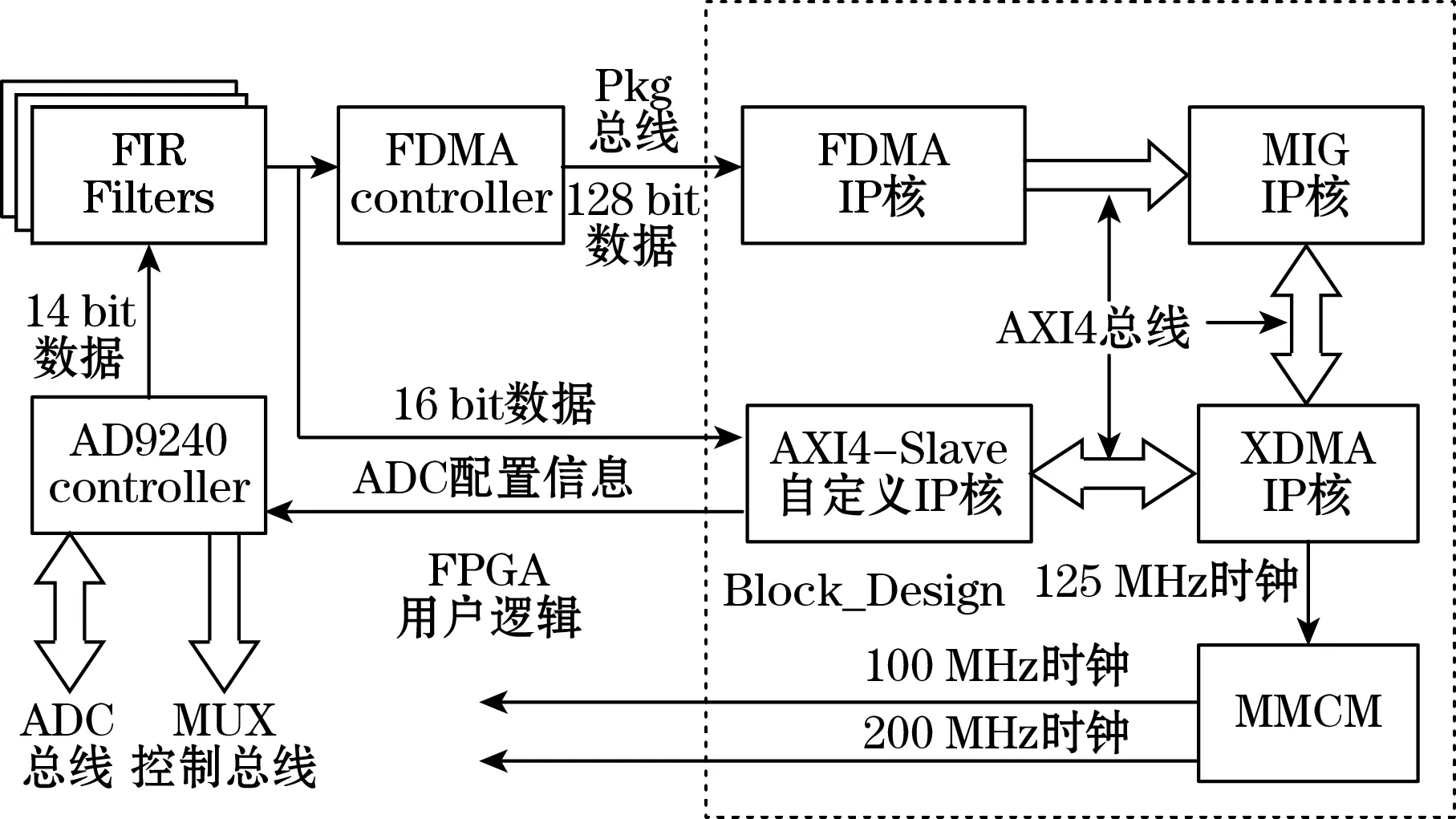

FPGA作为整个系统的主控单元,其逻辑设计是系统性能的关键,XC7A100T型FPGA的逻辑设计采用Xilinx官方推出的VIVADO开发环境,主要包括ADC数据接收控制、FIR数字滤波器、数据缓存控制和Block Design,内部逻辑框图如图4所示。

图4 FPGA内部逻辑设计框图

Block Design是基于Xilinx丰富的IP核和AXI协议的一种FPGA程序设计方式,本设计使用了Xilinx官方提供的PCIe IP核XDMA,DDR存储器IP核MIG和MSXBO公司提供的IP核FDMA。除此外,时钟管理单元MMCM将XDMA提供的125 MHz时钟分别转化为100 MHz时钟用于用户逻辑和200 MHz时钟用于MIG控制器。

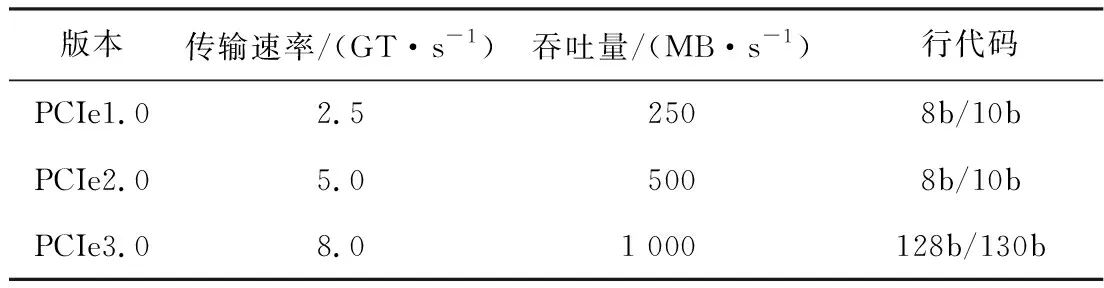

PCIe接口各版本的性能参数见表2。本设计采用PCIe2.0 X2接口,可提供链路带宽为10 GT/s,满足高速传输设计指标。

表2 PCIe各版本性能参数

XC7A100T芯片带有PCIe硬核模块,在不占用额外逻辑资源的情况下便可完成高性能、高效率的PCIe接口设计。Xilinx提供了3种关于PCIe的IP,分别为“7 Series Integrated Block for PCIe”、“AXI Memory Mapped to PCIe”和“DMA/Bridge Subsystem for PCIe(XDMA)”,其中第一种IP集成度低,仅包含了PCIe协议,第二种IP在前者基础上集成AXI内部总线。本设计采用的IP核为XDMA不仅包含有PCIe协议的物理层、数据链路层和事务层,并且实现了一个高性能、可配置的分散聚集式DMA[10]。本设计将XDMA配置为AXI MemoryMap接口,以实现PCIe地址空间和AXI地址空间之间的高性能数据传输,除此外添加AXI-Lite Master总线实现PCIe BAR地址到AXI-Lite地址空间的映射,主要用于上位机CPU与AXI4-Slave自定义IP核内外设寄存器进行通信。

存储芯片选用2片DDR3内存,数据接口32 bit,容量为512 MB,在200 MHz工作频率下理论带宽可达3 200 MB/s,满足最高32通道10 MSPS的大容量数据缓存要求。MIG控制器IP核包括了物理层、内存控制器和用户接口模块,完成DDR3的初始化、刷新和预充电操作,并且把DDR3复杂的读写时序简化,本设计配置为标准AXI接口,以实现与用户逻辑的连接。

FDMA是一种方便用户逻辑进行AXI4 Full Master操作的IP核,主要用于采集数据到DDR3的DMA传输。同时为了实现用户逻辑与PCIe的简单高速通信,设计了AXI4-Slave自定义IP核存储上位机PCIe发送的ADC配置信息和采样数据,寄存器地址见表3。

表3 AXI4-Slave寄存器地址表

将所有IP核挂载到AXI4总线上,则上位机和用户逻辑分别可以通过PCIe和FDMA来访问对应AXI地址空间的各个模块。自定义IP外设寄存器和DDR3通过地址映射成为上位机和FPGA的共享存储器。当上位机向FPGA发送写请求时,XDMA把配置信息写入外设寄存器,进而控制ADC数据接收模块把数据通过FDMA存入DDR3;当上位机向FPGA发出读请求时,XDMA将数据从DDR3读出到上位机内存。

3.1 ADC数据接收控制模块

用户逻辑接收到配置信息后,ADC数据接收控制模块开始控制ADC芯片,图5为模块的FPGA逻辑架构。通过除法器IP核由配置采样速率和启用通道数计算ADC的单通道采样时钟;由于AD9240输出在时钟沿后3个周期出现,数据处理单元根据启用通道数包含的二进制位置信息,经过寄存器延迟产生当前数据的通道位置、数据有效标志和14 bit并行数据;同时MUX控制单元产生MUX总线选通相应模拟通道;除此外,状态处理单元对配置采样深度和采样计数器比较,控制全局使能信号。

图5 数据接收模块逻辑架构

3.2 FIR数字滤波器设计

ADC转换后的数据仍存在高次谐波和其他高频信号,这些噪声的存在会影响到数据处理和分析结果,因此将数据传输到下一级前需要对数据进行滤波处理。本设计采用9阶FIR有限长单位冲击响应滤波器,具有线性相位、幅度特性可设置的特点。图6是基于式(4)的FPGA逻辑架构,其中x(n)为输入信号,N为阶数,g(n)为输出信号,利用MATLAB的FDATOOL工具产生滤波器系数h(k),将系数导入FPGA通过寄存器延迟和加乘法操作实现,由于滤波器系数为小数,而FPGA只能处理整数,采用移位算法实现先放大后取整,再除以相同的倍数,可以减少硬件资源消耗。

图6 FIR数字滤波器逻辑架构

(4)

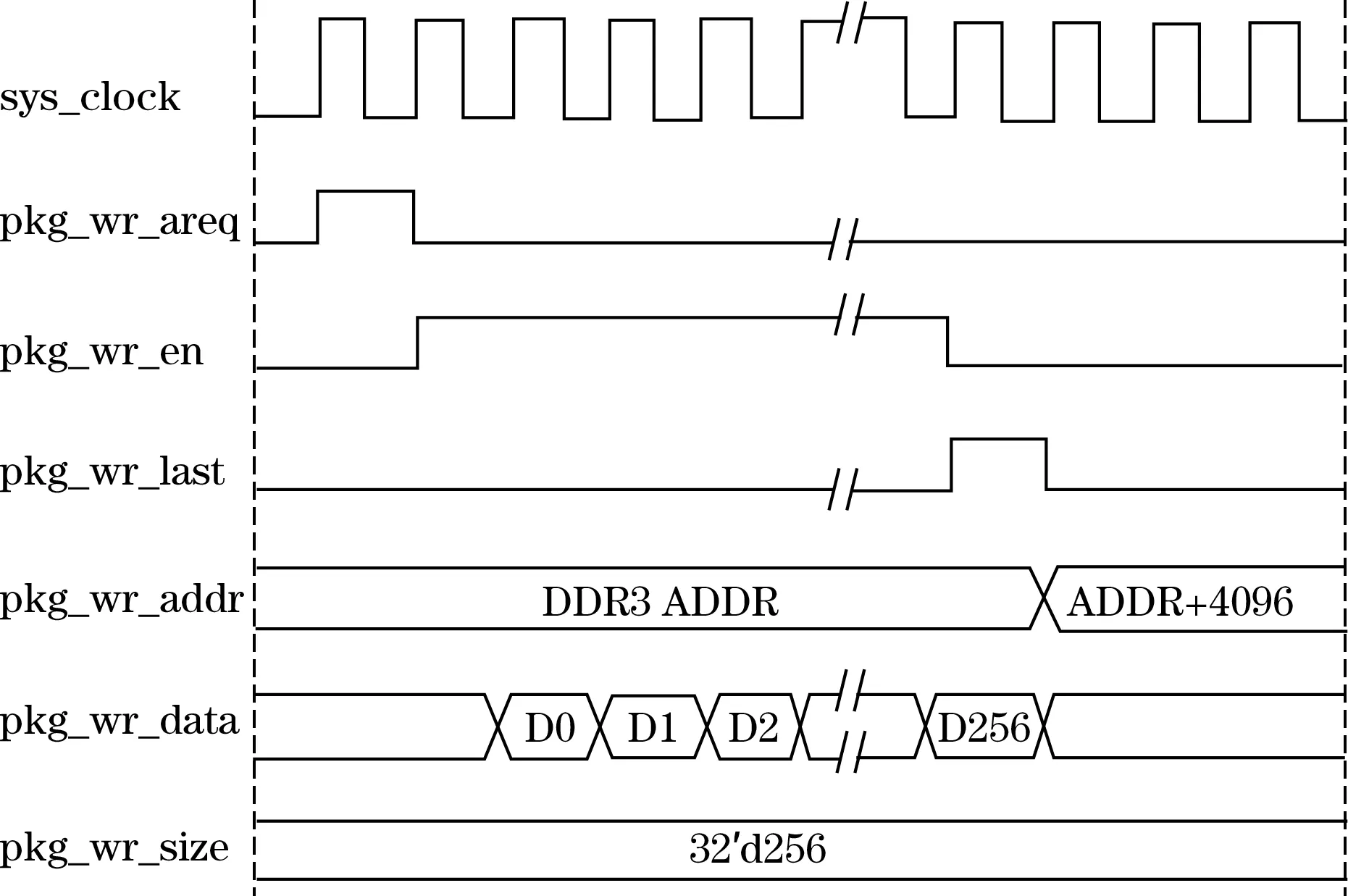

3.3 数据缓存控制模块

FDMA controller模块实现将滤波后数据打包为FDMA的Pkg总线,由状态机和FIFO组成。本设计只用到FDMA的写通道,其时序图如图7所示;采用同步FIFO,输入时钟为100 MHz系统时钟,输入使能和数据为滤波器的有效信号和16 bit输出,输出使能和数据为Pkg总线的en信号和128 bit数据。状态机包括IDLE和WRITE状态,IDLE状态下,设置AXI突发传输一个数据包大小为128 bit×256=4 096 B,当FIFO读计数器达到256时产生一个标志位,则状态机检测到标志位后产生一个Pkg总线的areq高脉冲,并且状态机跳转;WRITE状态下,一个数据包经过FIFO传输到FDMA,则FDMA会产生一个反馈信号last,状态机检测到该信号后将地址增加4096并返回IDLE状态。

图7 FDMA写通道时序图

4 系统性能测试

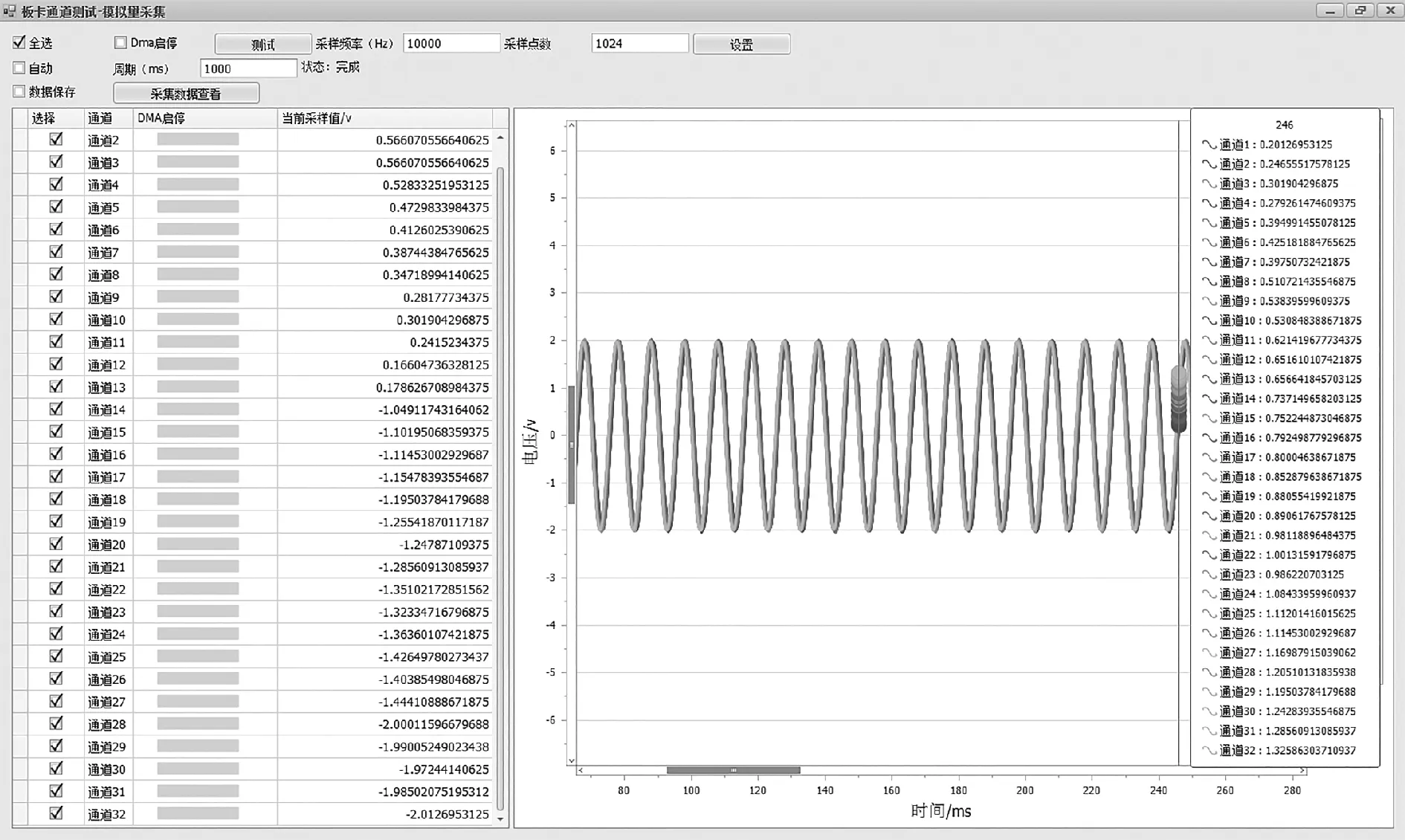

系统上位机软件分为驱动和应用程序,本系统基于XDMA驱动生成动态链接库DLL,使用Visual Studio平台进行应用程序的开发,编程语言为C#。图8为应用程序界面图,操作流程为:首先,通过选择启用通道号,输入采样频率和采样点数后,点击设置按钮;然后,点击自动,界面实时刷新显示当前各通道采样值或点击测试,上位机将采集到的数据保存创建Excel文件且作图显示。

图8 应用程序界面图

4.1 采样精度测试

通过直流电源GPD-2303S输出被测直流电压,该直流电源的电压读值精度为±(0.03%×读数+10 bit),可以满足对系统采样精度测试。上位机设置采样率为2.5 MHz,采样点数为10 240,测量结果如表4所示,结果表明本系统采样精度优于0.1%,满足性能要求。

表4 采样精度

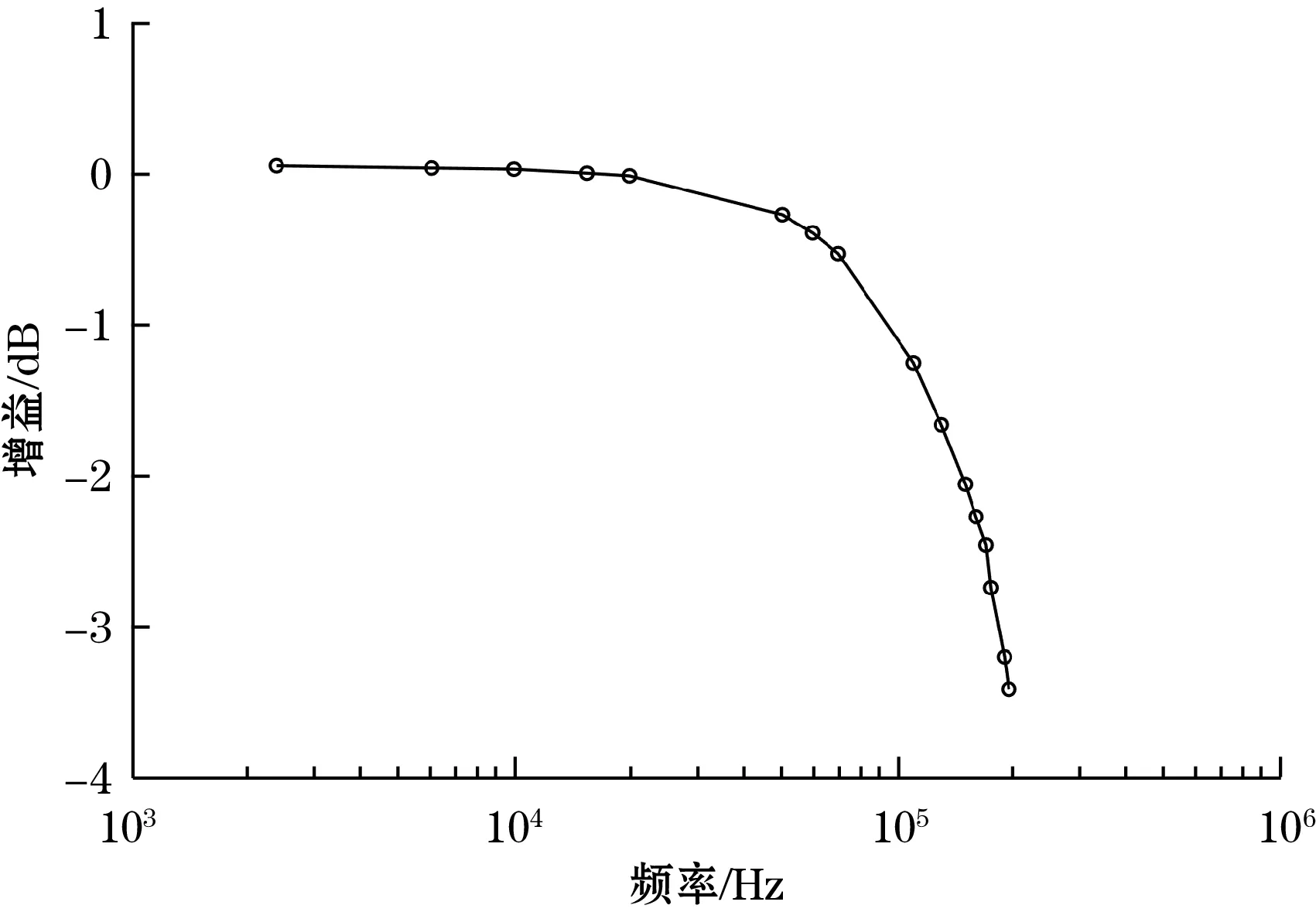

4.2 系统带宽测试

使用信号发生器输出峰峰值为20 V、频率为f的正弦信号作为测试信号,其中f的取值范围为:{2.4,6.1,10,15.5,20,50,60,70,110,130,150,160,170,175,190,195…},单位kHz,上位机设置采样率为2.5 MHz,采样点数为10 240,记录每个频率下系统采集到的信号峰峰值VO,则VO/20即为系统的增益,将其转换为对数,当增益衰减到-3 dB时输入信号的频率即为系统带宽,测量结果如图9所示,结果表明系统带宽约为190 kHz。

图9 增益-频率变换曲线

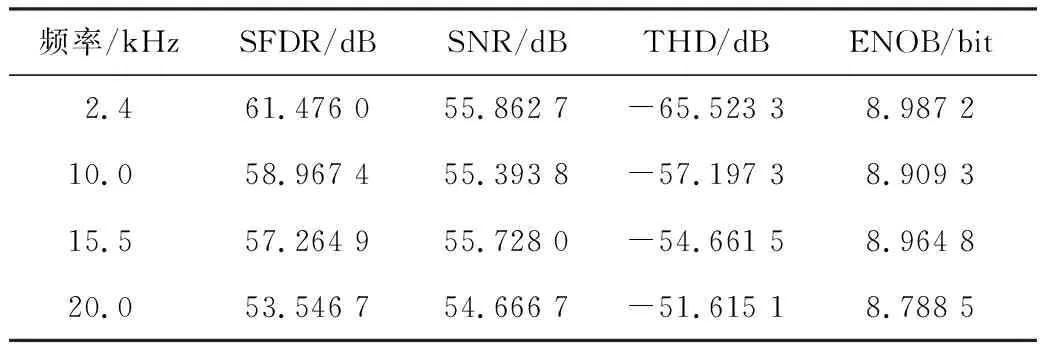

4.3 动态性能测试

选取系统带宽内若干频率点,使用MATLAB将采集到的数据做FFT变换并加窗,计算得到各频率点动态性能参数如表5所示,结果表明系统动态性能良好,信噪比约为55 dB,有效位数接近9 bit。

表5 动态性能参数

5 结束语

本文根据汽车EPS试验台中对测试系统的性能指标需求,设计了一款基于PXIe总线和FPGA的32通道数据采集系统,对系统采样精度、模拟带宽和动态性能进行测试,结果表明本设计在满足测试需求的同时与同类型数据采集系统比较具有价格优势。本设计增加输入通道时,只需增加信号调理电路和多路复用器,具有低成本的扩展性,同时FPGA逻辑设计中XDMA+MIG+AXI4-Slave自定义IP的Block Design逻辑架构可以方便地运用在其他类型PXIe板卡设计中,具有灵活的移植性,对国内EPS试验台的研发具有实用价值。