用于FPGA 的高效可测性设计

2022-10-12陈波寅胡晓琛

陈波寅,胡晓琛,张 智,赵 赛

(无锡中微亿芯有限公司,江苏无锡 214072)

1 引言

现场可编程门阵列(FPGA)电路规模大,内部结构复杂,其测试实现和成本控制一直是FPGA 生产上的难点。FPGA 知识产权(IP)核具有独特的特性,其结构组成有别于传统专用集成电路(ASIC)设计。例如高速串行计算机扩展总线标准(PCIe),其主体结构事物层、数据链路层、物理编码层以及配置管理模块集成在PCIe IP 核;外围应用层、功耗管理、配置管理、数据链路层包(DLLP)存储都由FPGA 内的可配置逻辑块(CLB)、嵌入式随机存储器(RAM)块、锁相环(PLL)等单元完成。目前采用自动测试设备(ATE)测试FPGA主要是针对其内部资源,如输入/输出(IO)单元、可编程逻辑单元和可编程布线资源[1-2],对于FPGA 协议类复杂IP 核的ATE 测试研究相对较少。传统FPGA 协议类IP 核的测试方法主要是环回功能(即数据通过发送端经过外部逻辑后到达接收端)测试[3],以此来验证高速接口类IP 核的正确性,由于PCIe 工作模式分为根复合体(RC)和端点(EP),该方法不适用于PCIe ATE 测试。传统的集成电路可测性设计(DFT)方案需要时钟和IO,这些单元都是通过FPGA 的时钟资源、开关矩阵(SWB)、可编程互联点(PIP)等系列结构互联PCIe IP 核的,但是上述结构对于可测性设计工具Tessent 而言是黑盒子,并且没有对应的库可以描述这些黑盒子,所以Tessent 不能自动识别这些FPGA 的内部结构,导致时钟和测试路径不通,进而无法进行DFT[4]。这些特性决定了板级测试PCIe IP 核的实现需要一套复杂的系统,ATE 测试缺乏有效的方案,而板级测试复杂且不利于高低温测试。

为了解决FPGA IP 核的测试难题,本文结合传统DFT 方法和FPGA 可编程的架构特点,提出一种可编程的高效FPGA IP 核可测试性方案。

2 测试设计整体方案

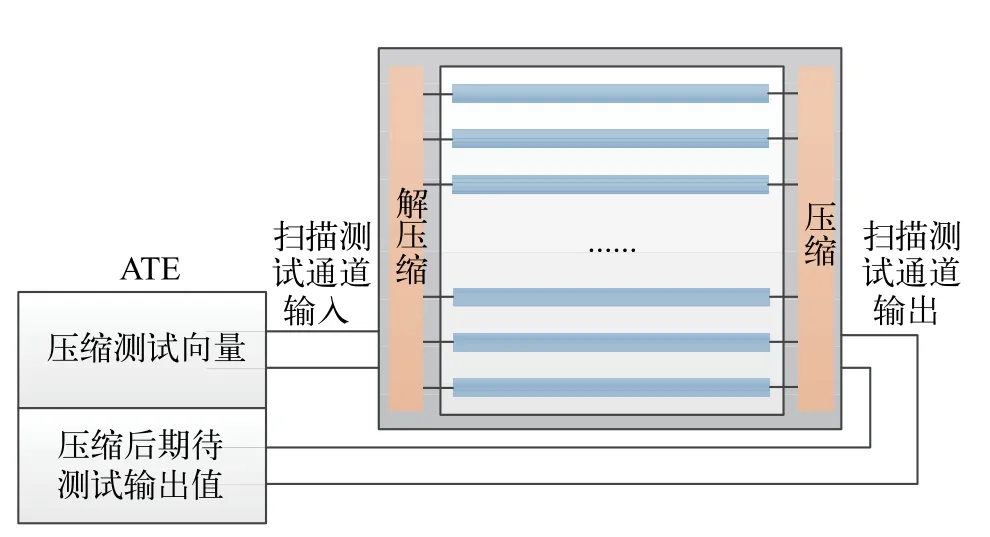

ATE 整体测试方案如图1 所示,基于Tessent 在IP 核上实现具体DFT 设计,ATE 通过芯片引脚输入压缩后的测试激励,基于FPGA 开关矩阵的可配置特性,将测试激励送到芯片内部IP 核的输入端口。同理,IP 核的输出响应由开关矩阵输出,ATE 接收压缩后的测试输出响应并判断测试结果,从而完成对IP 核和开关矩阵制造缺陷的测试。整体测试方案主要包括两部分:扫描压缩设计和开关矩阵绕线算法设计。

图1 ATE 整体测试方案

3 可测性设计原理

3.1 IP 核DFT

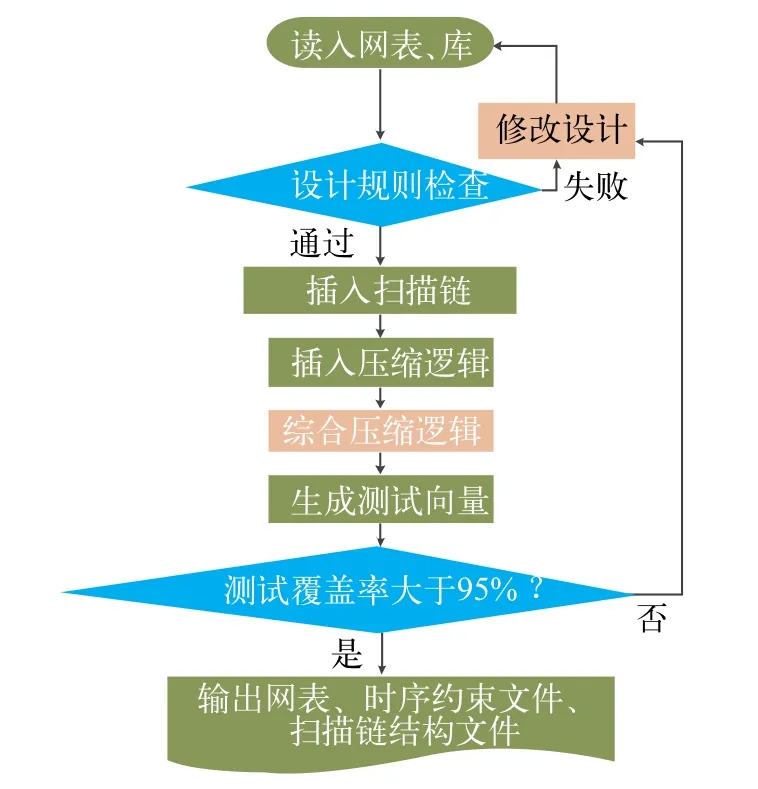

PCIe 模块中主要是数字逻辑,因此DFT 主要指实现扫描链设计。PCIe 模块中有近10 万寄存器,数量可观,但是测试端口有限(测试输入和测试输出均为25 通道),因此通过扫描压缩实现输入端解压缩和输出端压缩,将内部的长链转化为多条并行的短链,可减少ATE 测试时间,从而大幅降低测试成本。PCIe 内部的测试电路结构如图2 所示,配置开关矩阵,打开测试IO 与内部测试接口的通路,可将测试激励输入到解压缩模块,解压后送入PCIe 模块,测试响应由压缩模块输出。基于Tessent 实现具体的扫描设计,整体设计流程如图3 所示。

3.2 扫描压缩设计原理

由于集成电路的规模不断增大,内部的寄存器数量也越来越庞大,但是芯片上的测试端口有限,如果没有压缩技术,扫描链会非常长,相应在ATE 上的测试时间就长,而测试时间是影响整个芯片成本的一个关键因素。

扫描压缩采用的线性反馈移位器(LFSM)结构如图4 所示,图中黑色粗线路径为扫描压缩结构的数据路径。将内部的长链转为短链,在外部测试端口不增加的情况下,在内部将一条长链分成并行的4 条扫描链,从而使扫描移位时间缩短,测试成本随之大幅度降低,此时的测试时间取决于压缩后内部最长的那条链。蓝色线为旁路路径,内部并行的4 条链合成一条,多用于测试初期的接口调试。

压缩结构的内部核心算法模块有:1)解压缩模块,负责将测试输入通道移位进来的压缩后测试向量进行解压缩,并输出给内部所有的扫描链,位置在测试的输入通道(连接到ATE)和内部的扫描链输入端之间,解压缩模块主要由一个LFSM 构成;2)压缩模块,将内部所有的扫描链输出响应进行压缩,并由测试通道移位输出,位置在内部扫描链输出端和测试输出通道(连接到ATE)之间,压缩模块主要由门控逻辑构成;3)旁路模块,通过多路选择器(MUX)将输入解压缩、输出压缩的逻辑进行旁路,把内部所有的扫描链连接成长扫描链,并连接到测试输入、输出通道,实现内部扫描链的直接访问,多用于调试。

图3 PCIe 扫描设计流程

3.3 开关矩阵绕线算法设计

FPGA 可编程部分可测性设计算法实现的布线结果包括2 部分:1)从一个互连节点到另一个互连节点之间的连线;2)PIP 的配置选通。对于FPGA 的硬件来说,连线其实是不可更改的,也就是所谓的硬连线。真正实现模块间可配置通路的是那些可配置的互连节点。

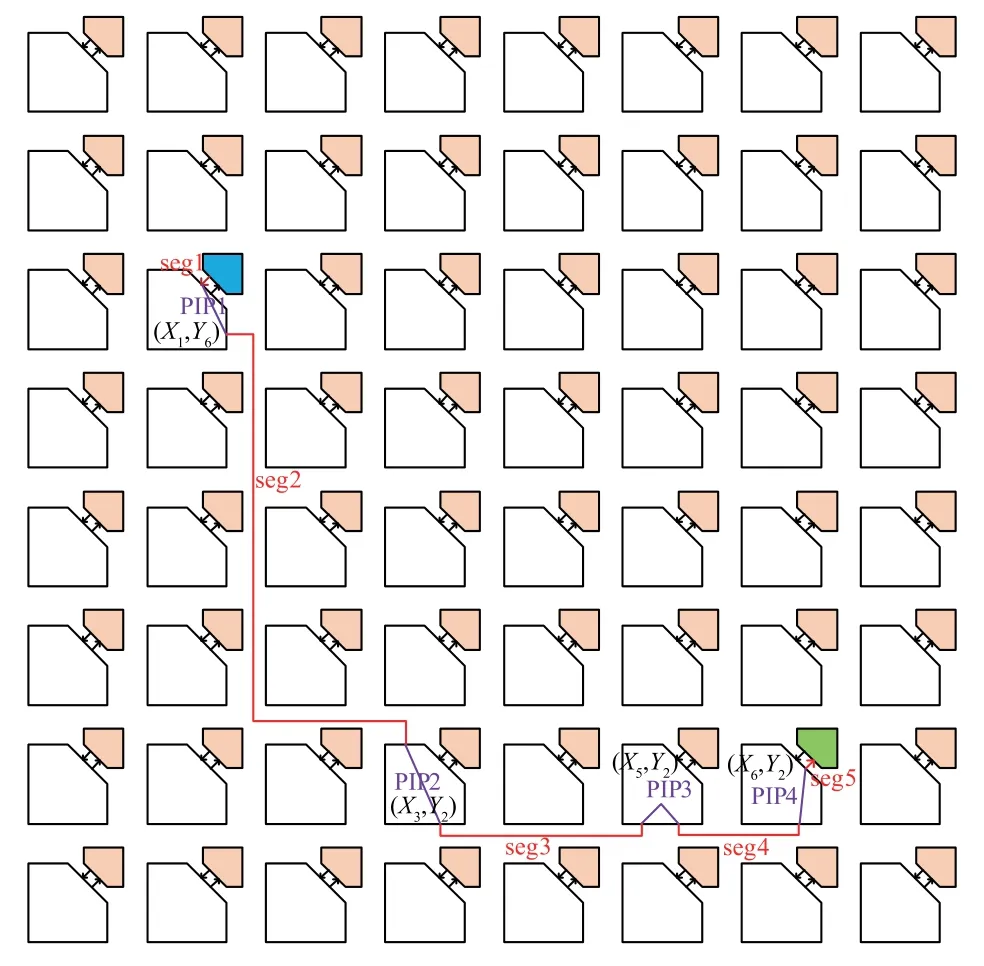

FPGA 的布线结构如图5 所示,橙色图形为逻辑模块,白色图形为开关矩阵模块,蓝色图形是输出模块,绿色图形为输入模块。红色线段表示连线,紫色线段表示可配置互连节点。从图5 中可以看到,该条布线包括了5 段连线和4 个PIP。根据上面的描述,连线都是与PIP 直接相连的,因此实际上也可以直接就用这4 个PIP 来表示整条布线,即当这4 个PIP 连通之后,从输出点到输入点的整个连接成功打通了。

图5 FPGA 布线结构

由于整个FPGA 中的连线和PIP 是非常多的,因此上述布线只是从输出点到输入点的很多条路径中的一条而已。而布线程序就是要尽量找到一条长度更短、延时更低的路径。在工程上来说,一个设计在实现的时候会面临非常多的布线需求,布线工具往往还需要具备能处理各种布线冲突以及优化迭代的能力。由于布线算法只针对一些简单的测试需求,是对EDA工具的一种补充,因此考虑的布线能力仅限于能尽量布通每一条测试通路。

针对测试需求实现的布线程序算法流程如下。

1)将整个FPGA 中的所有连线和PIP 以顶点和边的形式模型化为一张有向图并加载到内存中。

2)以起点位置作为当前点,分析终点和当前点的相对物理位置。

3)根据相对物理位置选择可使用的PIP 集合:

a)若物理位置重合,则选用输入专用PIP;

b)若物理位置不重合,则根据方向优先选择更优(在不超过范围的前提下尽量长)的路径。

4)判断可用PIP 集合是否已标记用尽:

a)若是,将前一PIP 标记为暂不可用,并从路径中剔除,判断路径中是否还有PIP,若是,则将上一节点设为当前点,返回流程3),若不是,返回错误并退出布线程序;

b)若不是,选择一个可用PIP,并继续以下步骤。

5)以PIP 的输出端作为当前点,将该PIP 放入路径中,并标记为已使用。

6)判断当前点是否为终点(或与终点直连):

a)若是,返回当前路径中的所有PIP,将布线过程中标记为暂不可用的全部PIP 标记为未使用,并完成当前布线;

b)若不是,返回流程3)。

算法中为了保证布线的时候不会重复计算,并保证每条布线之间的独立性,也为了确保每次布线的资源都能合理释放,对每个PIP 添加了2 个属性:已使用和暂不可用。已使用是指一个PIP 在当前或者其他布线中已被使用,这时所有的布线都不能再使用这个PIP;而暂不可用指这个PIP 在当前布线中已经尝试过,但是并不能完成布线,因此告诉后续程序避开此PIP,暂不可用的PIP 在本次布线完成之后会释放给后续的布线使用。

结合上述的算法流程,得到具体开关矩阵的可编程算法如下。

1)起点坐标为(X1,Y6),终点坐标为(X6,Y2),因此优先选择连接南至东(SE)方向所接线段跨度为6 的PIP。

2)当前点来到(X3,Y2),此时终点的相对位置为(X5,Y2),应选择连接东方向的PIP,如果使用最长线,则下一位置将直接到(X7,Y2),该位置已超过目标位置(X6,Y2),因此使用更短一些的线,完成(X3,Y2)→(X5,Y2)布线。

3)当前点来到(X5,Y2),此时终点的相对位置为(X6,Y2),依然应选择东方向,与2)类似的,完成(X5,Y2)→(X6,Y2)布线。

4)当前点来到(X6,Y2),此时终点的位置与当前点重合,因此应在输入专用PIP 中进行选择,完成(X6,Y2)→输入专用PIP 的布线。

以上示例是一个比较顺利的情况,因为每个方向的线其实是有很多通道的。每一个通道往下布线都可以到终点附近,但是可能并不能直接送到对应的那个输入专用PIP/旁路的点上去,所以可能需要多次退回,重复计算。

本文为布局一个PCIe 模块的所有DFT 信号,有25 个输出和33 个输入需要通过布线到IO 上来实现,因此在布线之前应该准备好58 个可用的IO,把它们的位置信息和输入/输出点放到一个列表中,然后再把PCIe 的测试端口在相应SWB 上的位置信息放到另一个列表中,2 个列表一一对应,基于上述算法实现最优点导通。

4 可测性设计结果

4.1 压缩算法优化效果

PCIe 扫描测试的输入/输出均为25 通道,扫描时钟频率为25 MHz,压缩与未压缩设计结果对比如表1中所示,从ATE 测试时间对比可以看出,压缩后的测试时间仅约为未压缩的1/22,测试成本大幅降低。

表1 压缩与未压缩设计结果对比

4.2 布线EDA 验证

全FPGA 验证方法是利用ISE 软件产生的ncd 和xdl 文件,从xdl 文件中提取出端口信息,将ncd 转换成的比特流加载在EDA 验证平台上,并添加激励文件进行仿真,最后对比输出结果来判断验证方案是否通过,EDA 验证平台如图6 所示。

图6 EDA 验证平台

根据设计的用例,将ncd 转换成相应的比特流,在全芯片仿真阶段,将该比特流信息加载到全芯片网表中,用于实现和设计用例相同的功能,功能相同代表验证方案通过,反之亦然。

比特流配置完成后,将扫描验证激励添加到验证平台中,通过测试端口输入激励,并观察输出端,完成测试比对。EDA 验证波形和结果如图7 所示。

图7 EDA 验证波形和结果

4.3 ATE 测试

ATE 加载STIL 格式的测试激励,按照STIL 中定义的时序打入测试激励,并完成输出数据的比对,若与STIL 中所定义的期望输出一致,则测试通过,否则判定为测试失败,ATE 输出测试失败信息,可通过工具分析、定位测试失败点。ATE 测试电路如图8 所示,实际测试通过。

图8 ATE 实测电路

5 结论

本文论述了FPGA 的可编程、低成本可测性设计的实现,解决了协议类IP 核无法进行ATE 测试的难题,优化了测试时间,满足FPGA 芯片的生产要求。上述方案可在FPGA 复杂IP 核测试的问题上通用,对于未来搭建全FPGA 自动化测试流程有重要意义,同时为FPGA 的高速测试研究奠定了基础。