一种GaN FET的窄脉冲激光器驱动电源系统设计

2022-09-29倪小龙闫钰锋白素平

许 源,王 武,倪小龙, 闫钰锋 ,于 信,白素平

(1.长春理工大学 光电工程学院,长春 130012; 2.北方导航控制技术股份有限公司,北京 100176)

0 引言

由于半导体激光器具有小体积、高可靠性、高功率密度等特点[1],半导体激光器目前广泛应用于工业、军事、科学研究领域并发挥着巨大的价值。在激光引信、激光测距及部分通信等领域,为满足特定场景对脉冲信号的要求,系统内需要驱动电路产生脉宽和重复频率均可调节的脉冲信号[2],并且对最终输出的光脉冲信号的上升时间、脉宽和可调节性有较为严苛的要求。

在激光雷达系统的应用中,为实现对周围环境的感知,需要激光发射电路发射激光[3-4]。激光驱动电路控制着加载到激光器的电压和驱动电流,可直接影响光脉冲信号的脉冲精度、功耗、信号强度和稳定性等,深刻影响整个系统的测量质量和稳定性[5]。产生精度更高、重复频率更高且更易于调节的激光光脉冲是该研究领域的热点之一。

国外在半导体激光器的研究起步较早。德国Kassel大学,在脉冲激光雷达系统研究中,使用振荡器电路产生高频脉冲,进而控制半导体激光器,产生了皮秒级别脉冲[5]。在国内,近些年来取得了较多成果:中国科学院研制出的LD驱动系统,在工作电压22~30 V下,可输出脉宽小于15 ns、最高功率141 W的光脉冲[6],但是脉冲宽度调节范围小、最低脉宽精度略显欠缺;天津大学微电子学院团队研究的驱动电路在200 v大电压输入下,实现输出脉宽 5~200 ns 内可调、重复频率 0~50 kHz、上升时间小于5 ns 的光脉冲信号[7],是国内较为先进的研究成果。由上看出,国内对半导体激光器驱动方式的研究不尽相同,能在纳秒级别产生激光脉冲,但是在更高精度上和更高重复频率下对光脉冲的驱动和调制仍存在不足。

此设计着眼于半导体激光器驱动电源的设计与优化,在已有驱动的研究基础上,采用GaN FET 宽禁带半导体器件,实现并验证了可稳定产生最低光脉宽至3 ns、最高重复频率达到1 MHz且脉宽和频率可调的驱动电路。在实现上:首先,以FPGA编辑门阵列电路,输出可调节的时序脉冲信号;然后,设计信号驱动电路,用以驱动高速器件GaN FET的低侧栅极,形成开关电路;最后,由储能电路中脉冲电流激发半导体激光器发出光脉冲。最终根据实验及数据分析,设计可稳定输出脉冲宽度3~200 ns、脉冲重复频率0~1 MHz,峰值功率超过70 W,上升沿时间小于5 ns的激光光脉冲信号。

1 系统结构及原理

半导体激光器由载流子注入而工作,类似于二极管的工作原理,并具有阈值门限。当注入半导体激光器的脉冲电流超过其阈值,则会受到激发产生相应光脉冲[8-11]。电路系统设计如图1所示。

图1 电路系统设计示意图

对光脉冲信号的调制,关键在于对半导体激光器所在电路中驱动电流的调制。此驱动控制系统的设计主要可分为时序产生电路设计和激光驱动电路设计。第一部分设计产生时序信号作为控制信号:利用混合时钟管理(MMCM,Mixed Mode Clock Manager)单元对低频信号进行倍频,通过Verilog语言编辑逻辑门阵列电路,最终综合并映射到FPGA上,生成时序控制电路,输出精准的时序信号;第二部分为激光器驱动设计:经过理论分析与验证,使接入的FPGA输出信号经过提高负载能力等处理后作为控制信号,设计驱动开关频率高、导通电阻小的GaN FET半导体器件的电路以及作为能量供应的储能电路,最终产生流向激光器的可控电流脉冲,实现半导体激光器光脉冲的输出与调制。

1.1 时序信号产生电路

时序信号产生电路旨在发生频率、脉宽可调的稳定窄脉冲信号,设计此电路使其具有实时调节信号的功能,同时满足严格的时序要求。方案采用Xilinx Zynq-7series 全可编程芯片,利用PL端丰富的全局时钟和全局布线资源,设计出兼顾低功耗、高性能及现场可编程的时序逻辑电路。

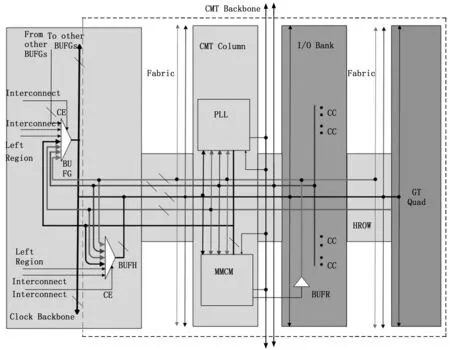

在原理上,全局核心是以时钟计数法,使用PL端时钟管理单元(CMT,clock manager tile)的MMCM硬核倍频生成的500 MHz的高速时钟进行计数,以高速同步时钟合成一路可调节脉冲信号。在布线上,将时钟布局到全局时钟线上,使用全局时钟缓冲器(BUFG)对其驱动。BUFG能够到达设备上的任何时钟点,利用其强大的驱动能力,将布线时延尽可能缩减到最小。FPGA时钟宏观结构垂直时钟中心线(时钟主干线)将设备分为相邻的左右区域,而水平中心线将设备分为顶部和底部。所有水平时钟资源都是包含在时钟区域中心的水平时钟行(HROW,horizontal clock row)区域,非区域性时钟资源包含在时钟主干或CMT主干中,如图2所示。

图2 时钟区域宏观结构

每个7系列FPGA都有时钟区域和I/O时钟树,可以在一个时钟区域中为所有顺序资源计时。每个设备还具有多时钟区域缓冲器(BUFH),允许区域时钟和I/O时钟跨越多达3个垂直相邻的时钟区域。BUFG和BUFH在HROW中共享12条时钟轨道,可以驱动该区域的所有时钟点。BUFG和区域BUFH/CMT/CC引脚连接以及区域内可用资源数量的右侧区域详细的内部结构如图3所示。

图3 BUFG/BUFH/CMT 时钟区域细节

在电路的逻辑设计中使用数据流级、行为级等方式进行建模信号,形成逻辑门电路。由于用单时钟进行信号产生的设计,避免了多时钟合成引入的时钟偏移和相位倾斜问题,最终能实现以2 ns为调节步长的调整。设计生成的时序发生模块部分的电路如图4所示。

图4 时序发生模块电路

在数字信号设计中,时序设计十分重要[12]。为保证信号质量,需要优化电路布局设计,设计应尽量满足合适的时间裕量,时间裕量的计算公式如下:

Slack=Trequired_time-Tarrival_time

(1)

Tarrive_time=Tco+Tdelay+Tsu

(2)

公式(1)中Slack表示时间裕量;Trequired_time表示约束的时长,即为所规定的时长;Tarrival_time表示实际时延;公式(2)中Tco是内部延时参数,表示寄存器在有效上升沿来临,将数据送至输出口的延时;Tdelay为数据因组合逻辑的走线延迟时间;Tsu表示数据最小建立时间。

经过对时序和引脚的约束及时序分析后,综合并映射形成电路网表下载到门阵列硬件中,生成时序信号产生电路,并进行实验验证及迭代。

1.2 激光器驱动电路

激光器驱动电路包含三部分电路:信号处理电路、GaN FET驱动电路和储能电路。

FPGA输出电平标准为LVCMOS 33的时序信号,其输出的VCCO保持在3.3 V附近,负载能力较弱。为了能够有效驱动后级电路,并对信号进行滤波,设计了时序信号处理电路。为了保证FPGA输出的时序信号的高速特性,使用了TLV3601高速比较器输出推挽信号,并上拉输出信号,有效提高了信号的负载能力。信号处理电路如图5所示。

图5 信号处理电路

FPGA时序信号经过此处理电路后作为控制信号,作为后级GaN FET栅极的驱动器件的脉冲输入信号。

GaN FET功率器件具有低的击穿电压、低的阈值电压以及低的栅极电荷,在高温、高压、高频等场合下具有优于Si基半导体器件的特性,但其存在的缺点不可忽略,GaN FET栅极在高频情况下容易产生振动不稳的情况[13-14]。这就对其驱动的要求相较于传统的Si基半导体器件更为严苛。为保障其稳定工作,使用LMG1020驱动器件设计了具有快速、稳定驱动能力的前置电路。该驱动芯片用于驱动GaN FET的低侧栅极,传播时延可短至1 ns,工作时典型信号上升和下降时延在210 ps,能够保证GaN FET的快速反应。其LMG1020及外围电路结构如图6所示。

图6 驱动芯片及外围电路结构

另一方面,为了提高对半导体激光器驱动的性能,对储能电路中电流的分析至关重要[15]。在高速脉冲电流下,电路会产生寄生电容和寄生电感,可以将储能电路简化为一个RLC回路进行电路分析。电路中电感L、回路电流i、包括半导体激光器和其他器件的电路总负载电阻Rc、电荷量Q、回路中储能电容C、供电电压为Vbus,电路的回路方程列为:

(3)

对上式微分后得出:

(4)

(5)

其中如下变量:

α、ω、A分别代表电路电流的衰减因子、频率和振幅。由(5)式,电路中的回路电流会呈类正弦曲线状态。为保证良好的窄脉宽光脉冲产生,应提高衰减因子,使得衰减速度加快,减少光信号的波动;并减小频率,使得触发电流快速上升和下降,减少上升沿和下降沿时间;提高电流的振幅A,用以提高电流脉冲的振幅,进而提高光脉冲的峰值[16-18]。

定义电路阻尼参数的计算公式为:

(6)

储能电路开始放电时,电路中电流的上升和衰减具有时间延迟。为有助于窄脉宽脉冲的形成,电路应保持<1时的欠阻尼状态[19]。在此状态下,电路振荡放电,有较好的反应能力。将电路中负载电阻固定,可通过调节电路中储能电容实现欠阻尼状态,达到如下条件关系:

(7)

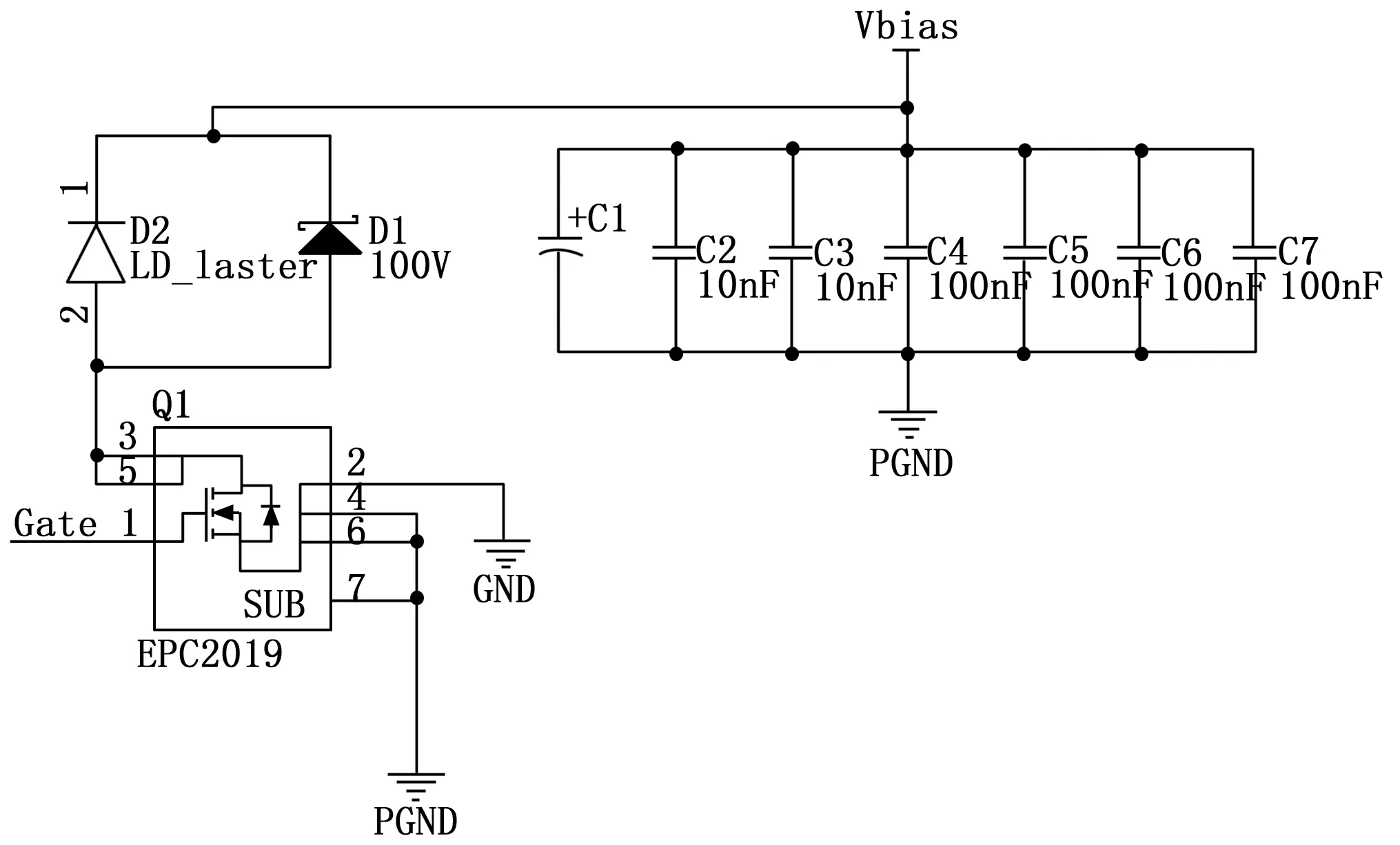

最后,在纳秒甚至百皮秒级对电路中电流进行开断时,电路中的寄生电容和寄生电感会谐振到储能电容中,产生过调电压。这种过调电压会增加电路压力,使输出光信号不稳定[20-21]。为避免无钳位电路时的感应大电压,减轻过调电压对电路器件的冲击,最终在储能电路中半导体激光器两端设计了一个反平行并联的传导路径,最终储能电路如图7所示。

图7 储能电路

2 软件设计

FPGA是一种硬件可编程的门阵列电路,原理上一般是基于查找表的内部结构,可通过程序语言对其内部电路设计,以时钟为驱动实现指定逻辑功能。

设计中使用自顶向下和自底向上相结合的设计思路,用Verilog设计了按键式人机交互、时序信号生成的逻辑设计,形成寄存器转换(RTL,Register Transfer Level)级模型。软件设计框图如图8所示。

图8 软件设计框图

设计的软件设计主要是对人机交互接口的设计。在人机交互软件设计中,最初选用按键式调整参数的方式,主要设计按键消抖和按键功能逻辑,缩减了前期的验证时间。后期在优化实验时用FPGA加入了LCD屏显示和UART串口通信的软件设计,优化了人机交互操作。

2.1 LCD屏驱动软件设计

在LCD屏显示的设计,选用薄膜晶体管液晶显示屏(TFT-LCD,Thin Film Transistor-Liquid Crystal Display),每个像素点由其背后镶嵌的薄膜晶体管独立控制。每个像素的显示由红绿蓝3种颜色通道分量配合控制,像素格式使用RGB888格式,即共有24bit的数据控制颜色,理论上颜色可有1677多万种类的调控。TFT-LCD行显示时序如图9所示。在驱动TFT-LCD时,由像素时钟作为最小单位驱动,每次扫描完一行时会发出水平同步信号(HSYNC,Horizontal Sync)作为每一行结束的标志。HSYNC的作用时间由行同步信号宽度(HSPW,Horizontal Sync Pulse Width)表示。由于器件特性,在进行下一行前会有一段延迟称为水平同步后肩(HBP,Horizontal Back Porch),与此对应会有水平同步前肩(HFP,Horizontal Front Porch);行有效显示区域HOZVAL和屏幕的分辨率有关,表示一行中有效数据时间。通过程序设计在HBP时间结束后,拉高DE信号电平,进行数据操作。

图9 行显示时序

相似于行,帧同步信号(VSYNC,Vertical Sync)由帧同步信号宽度(VSPW,Vertical Sync Pulse Width)、帧显示后肩(VBP,Vertical Back Porch)、帧显示前肩(VFP,Vertical Front Porch)以及帧有效显示时间(LINE)构成。VSYNC的时序以HSYNC为计量的基准,帧显示时序如图10所示。

图10 帧显示时序

由上驱动时序列屏幕显示一帧图像的时钟数的计算公式为:

Tcount=(VSPW+VBP+LINE+VFP)*THorizontal=

(VSPW+VBP+LINE+VFP)*

(HSPW+HBP+HOZVAL+HFP)

(8)

式中,THorizontal表示扫描一行所用时钟计数,根据公式(8)以及屏幕单位时间内显示帧个数则可得出像素时钟的频率。设计所用帧率为每秒60帧、像素时钟为50 MHz。此设计采用分辨率1 024*600的显示屏,则一帧图像将由600行的有效区域。系统时钟即可作为像素时钟,并以像素时钟生成上述的时序信号,循环往复地按时序位置对数据引脚输出图像数据,打印对应位置像素值,最终就描绘成一帧图像。

2.2 通信及控制帧软件设计

为提高对时序信号脉冲宽度和重复频率参数调整的灵活性,设计了串口通信模块、数据帧协议,能实现上位机对FPGA输出时序脉冲信号的脉冲宽度以及重复频率的实时灵活调节。在FPGA上进行串口通信的设计时,主要完成对通信中接收数据的串并转换,提取通信中的各数据位,而信号的传输由板载外部驱动电路实现。图11所示是串口接收引脚接收数据时序。

图11 串口接收引脚接收数据时序

此设计使用了1 bit起始位、8 bit数据位和1 bit停止位,未使用校验位,Uart_rxd表示串口接收引脚的电平信号。当外部信号来临时会将电平拉低,形成一位起始位,标志数据传输的开始。由通信的波特率f波特率,就能计算出每个数据位的保持时间。由公式(9),根据时钟频率f时钟计算每位保持时间内的计数个数NCOUNT。在每计数到NCOUNT时,标志着上一位的结束,用以区分不同时序段的对应位,并在新的一位计数到来前将此位存到相应寄存器中。经过以上过程,将串行数据各位拆分转存为并行数据,完成数据的读取及存储。

(9)

为将调节参数包含到一个数据帧中,需要设计合适的数据帧协议并在FPGA端对接收的有效数据帧进行数据解码。图12表示对通信数据进行控制帧封装示意图。图中数据为16进制表示,帧头帧尾分别为0X55、0XAA,两字节固定不变,标志一个控制帧的开始和结束。重复频率控制字是上位机对时序脉冲信号重复频率的调节步长数;脉宽控制字是上位机对时序脉冲信号的脉冲宽度的调节步长数;控制字的设计用于标识此帧对重复频率或是脉冲宽度的调节以及调节的步长大小、调节方向。控制字的最高位做控制参数的符号位,标识此帧增加或减小的调节方向;第6位为选择位,用以标识此帧对重复频率或是脉冲宽度的调节;其余6位用于设置调节步长。由以上控制帧的软件设计,能完成上位机对FPGA时序脉冲信号重复频率和脉冲宽度灵活的调节。

图12 通信帧封装

2.3 程序固化设计

在软件的保存设计中,通过 JTAG 接口将 FPGA 配置文件和应用程序直接下载到 Zynq 器件中的方式具有易失性。为了能保证程序掉电不易失,需将生成的BIT流等配置文件建立启动文件下载到Quad SPI Flash非易失存储器中。Zynq器件具有特别的启动方式,每次上电由PS端先启动,从flash中读取FPGA配置文件,保证程序的不易失。BootROM是片上的一块非易失性存储器件,里面包含启动执行程序,Zynq Soc启动第一步从此开始。BootROM中执行代码会并调用含有启动信息的头文件以及FSBL(First-Stage Boot Loader)的偏移地址[22]。BootROM执行之后,进入FSBL配置阶段。FSBL配置了 DDR 存储器和硬件设计过程中所定义的一些外设利用。FSBL是根据工程设计自己创建的。最终,通过处理器配置访问接口(PCAP,Processor Configuration Access Port)对PL进行配置,它允许对PL 进行部分配置或者完全配置。固化软件的设计流程如图13所示。

图13 设计流程

最终,用Verilog硬件编程语言进行通信接口、显示屏驱动软件和信号产生等设计后,将PL端程序例化到PS端,并将工程综合生成RTL级原理图。Zynq的整体工程设计模块如图14所示。在信号引脚的设计中,外部引脚由TFT-LCD驱动引脚、串口引脚、按键引脚、信号输出引脚等组成,内部引脚包括双倍速率(DDR,Double Data Rate)同步动态随机存储器片内互联引脚等。通过工程对代码的综合及布局布线,最终将各模块互联形成了系统工程。

图14 整体工程模块

3 实验结果与分析

根据理论分析和电路绘制后,制作出实验验证板,用以验证光脉冲的调制状态。设计的激光器驱动电路尺寸4.4×3.6 cm,如图15(a)所示。对FPGA控制信号输出的验证,使用示波器可直接观测。对激光驱动电路产生的光脉冲,为近红外波长,使用DET08C/M探测器观测,输出结果显示在示波器上,分析调制信号的脉宽、上升沿宽度和重复频率。由于半导体激光头输出光信号有一定的发散现象,为了聚焦便于观察,在半导体激光发射头与探测器之间放置一个聚焦镜,使焦点落置于探测器的光敏面上,实验过程如图15(b)所示。

图15 实验装置及测试

在时序信号产生的电路设计中,使用了Xilinx的Zynq 7020 板卡,其具有106 400个触发器、53 200个6输入的LUT,板上搭载了4个CMT,每个CMT包含一个MMCM单元,并有32个采用全铜工艺的全局时钟线,资源在设计使用中尚有富余。所以,在“速度”和“面积”转换原则使用时,将可拆分的复杂逻辑和能并行计算部分铺开,以面积换取速度。最终总片上功耗为1.803 W,资源利用如表1所示。

表1 资源利用

FPGA输出脉冲信号的宽度在纳秒级别时,信号的上升比较稳定,在下降到底端会产生小振幅呈衰减的波动,其最高振幅在1 V以内;并且随着信号宽度的增大,信号逐渐呈现方波状态。FPGA中对时序脉冲信号脉宽分别设置在5 ns、10 ns时,将信号接到示波器上显示,输出的脉冲信号为5.09 ns和9.98 ns如图16(a)、(b)所示。

图16 FPGA时序脉冲信号输出

设计的钳位电路与半导体激光器支路并联,使用钳位二极管尽量与半导体激光器的电感相近,避免电流大量流过半导体激光器支路的状况。在选用钳位二极管和放置位置均有考究,经调试后钳位二极管选用了100 V、2 A的肖特基二极管,遏制过冲电压效果明显。在20 V的供电电压时,在存在钳位电路下半导体激光器的端位电压约为23.633 V,过冲电压控制在4.8 V之内,如图17所示。

图17 20 V供电电压下

调整FPGA输出的时序控制信号,设置使光脉冲输出在3 ns时,经驱动电路后输出信号由探测器测得约为3.2 ns脉宽的光脉冲如图18所示。

图18 3.2 ns光脉冲输出

设置输出重复频率为1 MHz,即信号重复周期为1 000 ns时,探测的光信号输出约999.17 ns的重复周期如图19所示。

图19 1 MHz重复频率,周期999.17 ns光脉冲输出

由于引脚及电路走线的特性影响,FPGA输出的时序脉冲在主脉冲后存在脉冲波动现象,但波动峰值较小在容错范围之内,并在后续信号处理电路设置阈值予以消除。在最终输出的光脉冲信号最低脉冲宽度可达到3.2 ns,实验的最高频率可调节到1 MHz,观测其误差在1 ns以内。

4 结束语

通过实验与验证,设计的可调窄脉冲驱动电源系统能够通过FPGA端的人机交互对输出的脉冲光信号进行纳秒级调制,输出可调控光脉冲的脉宽最窄为3 ns,最高调节重复频率高至1 MHz,实现脉冲宽度和频率在高频的高精度实时调节,能有效避免因修改电路来改变半导体激光器输出方案的操作复杂性。

在控制储能电路开关设计中有效驱动GaN FET,能够实现纳秒级快速开关,在半导体激光器驱动电路设计的研究上给予一定参考。此设计后期应继续提高FPGA调节精度及驱动电路的稳定性,并提升光脉冲的光功率,使得驱动电源系统性能进一步提升,对激光器的控制更加精密。