抗高过载千兆以太网数据记录器设计

2022-09-17刘跃泽熊继军洪应平

刘跃泽,熊继军,洪应平

(中北大学 仪器科学与动态测试教育部重点实验室,山西 太原 030051)

0 引 言

随着测试技术的发展,飞行器状态的测试手段更丰富,数据更详细,记录器需要记录的数据量不断增大,这对记录器的记录速度及容量提出了更高的要求[1⁃3]。抗高过载千兆以太网数据记录器是针对于飞行器运行过程中传感数据进行实时记录、存储,并在打击完成后,将数据进行回读。传统记录器采用LVDS、422等接口芯片,只能满足低速数据接收需要[4⁃7]。为了能更快地记录数据,已有研究采用千兆以太网接口[8⁃9],在和控制系统交互指令的同时也可以高速接收数据。采用eMMC作存储单元,与传统记录器内的NAND FLASH相比,单片容量更高且体积更小,便于进行抗高过载防护[10⁃13]。

本文提出了一种基于eMMC、采用以太网接收数据并通过DDR缓存的抗高过载千兆以太网数据记录器设计方案。eMMC作为一种新型存储介质,内部集成了NAND FLASH和控制器,由控制器对NAND FLASH进行读写控制,同时还具备坏块管理、损耗均衡以及ECC校验等较为复杂的功能。相对于NAND FLASH,eMMC容量大、读写速度快,高性能eMMC芯片在HS400模式下读写速度高达400 MB/s,能够满足抗高过载冲击信号记录仪高速、大容量、低功耗和小型化等要求。

1 抗高过载记录器系统

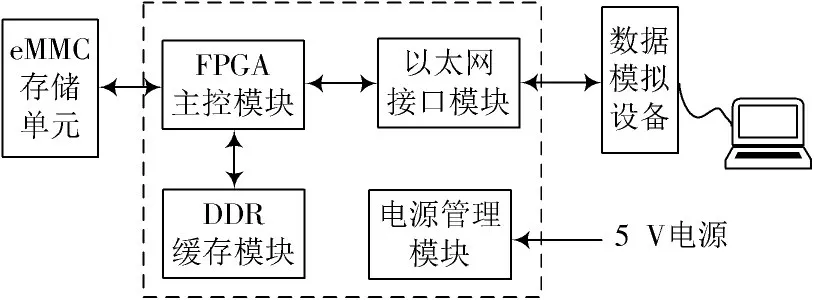

针对记录器设计时高速存储的难点要求,本文设计了一款可满足高速存储的新型记录器。该记录器采用模块化设计,整体系统的设计框图如图1所示,分为FPGA主控模块、以太网接口模块、DDR缓存模块、电源管理模块、数据模拟设备以及eMMC存储单元等六部分。本文主要对一些主要模块的选型和设计进行介绍,各主要模块的选型如下:FPGA主控模块选用Xilinx公司的具有4 GB的容量缓存数据XC7K160T⁃1FBG484I芯片;以太网模块选用Marvell公司的88E1111千兆网传输芯片;存储单元选用三星公司的KLMCG2KERM⁃B041,具备64 GB的存储容量用于存储数据;DDR缓存模块选用MT41K256M16JT⁃125,满足本系统需要长时间记录的要求。

图1 记录器设计框图

整个系统上电后,采用数据模拟设备发送数据和指令,保证模拟速率稳定,同时能发送编帧后数据,方便回读数据时判读,也可通过该装置回读数据到计算机端判读数据。

2 关键技术设计

数据记录系统关键技术主要为以下三点:以太网数据处理、编帧;高速数据通过DDR3缓存处理;eMMC数据存储逻辑设计。本文主要对这几个模块的关键技术进行叙述。

2.1 以太网数据处理编帧设计

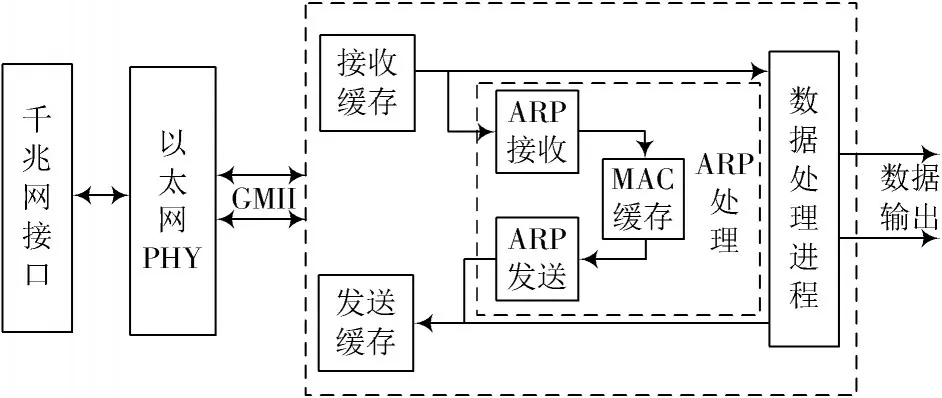

以太网模块选用Marvell公司的88E1111千兆网传输芯片,FPGA通过以太网模块对数据的收发进行控制,主要包含数据缓存进程、ARP地址绑定进程及数据处理三部分。数据缓存用于数据接收和发送;ARP地址绑定进程,通过ARP地址解析协议绑定MAC地址、IP地址,保证通信顺利进行;数据处理在UDP协议层对数据进行解析提取。以太网模块的整个通信原理如图2所示。

图2 以太网通信原理图

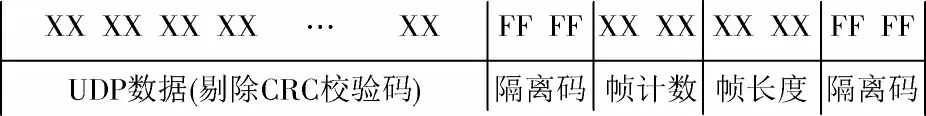

以太网控制模块采用PHY倍频生成的125 MHz的时钟作为主控时钟,首先通过ARP绑定地址后,模拟信号源收到ARP回复,开始发送模拟数据,模拟帧格式如图3所示,总长256 B,选用递加数便于分析是否有数据误码。数据处理进程判断解析UDP报文同时校验后,提取整包数据,并提取UDP协议内数据长度和UDP协议内的包计数写入帧尾,组成方便后期解析、判读数据,判断是否有误码、丢数及丢包。编帧后以太网数据包如图4所示。

图3 模拟帧格式

图4 编帧后以太网数据包

2.2 DDR缓存设计

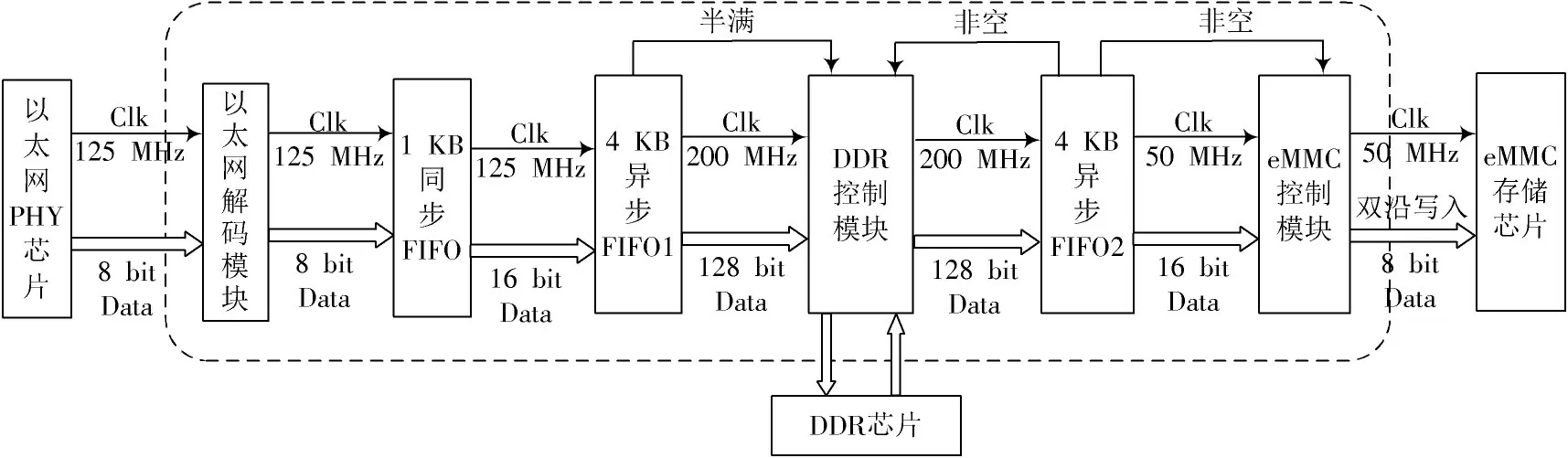

缓存模块用DDR3缓存,因写入读取数据宽度、时钟速率不同,采用异步FIFO实现跨时钟域处理和数据位宽转换,其原理图如图5所示。以太网解码模块采用同步于以太网PHY芯片倍频产生的125 MHz时钟作为驱动时钟,提取UDP数据帧中的有效数据写入同步FIFO,将DDR3的写入位宽设置为128 bit,FIFO无法直接将8 bit转化成128 bit数据,所以采用一个同步FIFO预先将数据转化为16 bit,同步FIFO的读使能保持拉高,将读数据有效接入下一异步FIFO的写使能,保证读数据有效时直接写入下一FIFO。因DDR3芯片读写共用地址数据总线,无法实现同步读写,所以DDR3控制需要设置优先等级,控制逻辑图如图6所示。控制流程主要有3个触发信号,最高优先级触发信号为DDR3忙,DDR3 IP在工作过程中Rdy信号及Wdf_rdy信号会随时拉低,这时DDR无法响应读写命令,所以状态要切入空闲状态,等DDR3结束忙状态。第二优先级为FIFO1半满,首先要保证FIFO1不会被写满导致丢数,因DDR3的带宽远远大于以太网的数据带宽,所以正常的控制逻辑图中,FIFO1永远不会被写满。当前两个触发条件没有达成时,只要DDR3内有数据,且FIFO2没有被写满,就执行写FIFO2操作。

图5 DDR缓存模块原理图

图6 DDR控制逻辑状态图

图7为用XILINX Vivado软件抓取的实时信号读写时序。

图7 DDR读写时序

2.3 存储模块设计

存储单元选用三星公司的KLMCG2KERM⁃B041芯片,该芯片具备64 GB的存储容量,在HS400模式下存储速度最大可达到400 MB/s,但时钟速率太高,必定会增大功耗和逻辑资源的消耗。本文记录器为保证抗高过载,将存储单元外挂,减小存储模块占用空间,实物图如图8所示。为了兼顾长线传输及结构设计,保证数据信号质量及数据写入速度,记录器采用双沿传输,50 MHz传输时钟(High Speed DDR模式)。在兼顾各方面需求的情况下,存储速度在满速时,瞬时存储速度达到100 MB/s,但因eMMC特性上有写入等待时间及命令字写入时间,平均速率可以保证大于60 MB/s。任务指标UDP通信速率最大为500 Mb/s,将数据包设置为最大包1 500时的最大通信数据速度约为57 MB/s,所以记录器满足实际记录以太网UDP数据包的能力。

图8 存储单元实物图

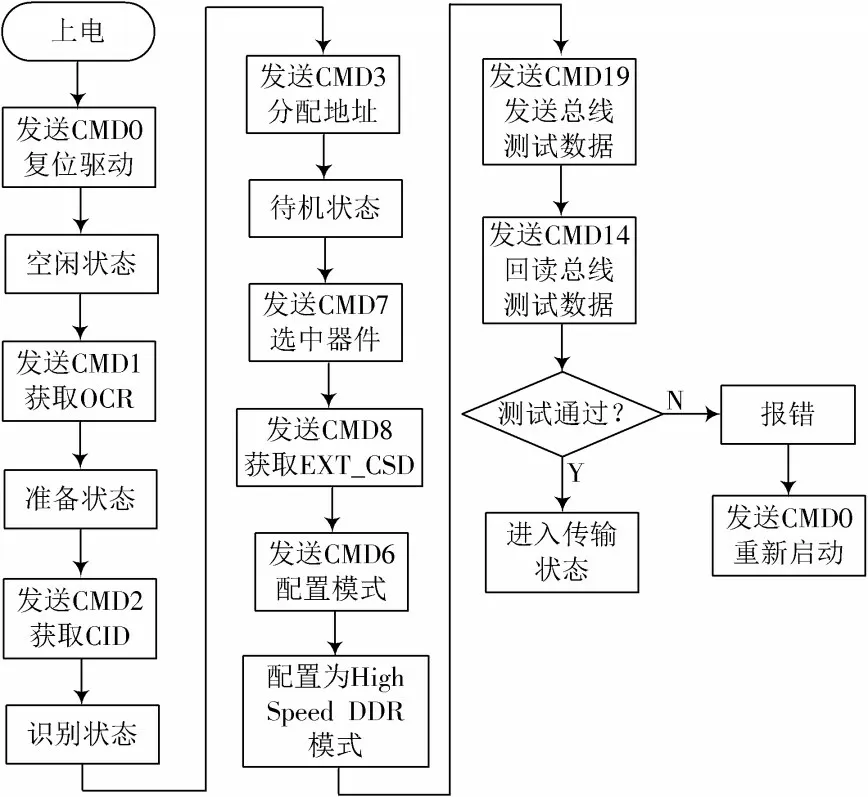

存储模块的初始化流程如图9所示。系统上电后,首先用400 kHz的低速时钟对eMMC存储芯片进行初始化,包括器件识别、容量识别和相关寄存器配置等。本系统将eMMC器件配置为High Speed DDR模式,该模式下最大时钟为52 MHz,设置总线数据为8 bit,I/O电压为1.8 V,最大数据速度为104 MB/s。

图9 初始化流程

初始化完成后,eMMC进入传输状态,该状态下存储单元可以响应读、写、擦命令。因任务要求,本系统分为4种模式:常规监控记录模式、硬启动模式、数据擦除模式及回读模式,工作模式流程如图10所示。存储单元初始化完成后处于传输状态,等待外部控制系统发送记录模式指令进入记录模式,在记录模式实时记录以太网数据,存满循环记录,便于随时回读以太网数据。

记录模式的详细工作流程为:首先发送CMD23设计多块存储块数,eMMC芯片每块容量为512 B,每次申请后,需要写入足够申请的数据才可以开始存储。因eMMC芯片特性,写入时间存在延时,所以每次申请的块数越多,存储速度越接近最大速度。本系统申请存储块数为2 048块,也就是每次申请1 MB存储空间;之后发送CMD24命令,设置存储起始地址,每完成一次存储,起始地址递加,存入接下来的2 048块地址。当没有外部其他命令输入,存储器一直停留在循环记录状态。

擦除模式下,eMMC芯片也是依据块地址进行擦除。在配置阶段,可以从寄存器中获取该芯片的容量,得到该芯片的最大地址。本系统不需要进行部分擦除,所以接收到擦除指令后,进行全空间擦除。首先发送CMD35将起始设置为0地址,发送CMD36将结束地址设置为最大地址,发送CMD38执行全空间擦除操作,擦除完成退出该模式。

硬启动模式是任务要求的特殊模式,在飞行器发射前5 min启动,将全空间擦除,进入记录模式,保证系统准确记录飞行器发射前及发射过程中的传感数据,保证记录器回收时可以得到整个飞行器飞行过程前后实时传感数据。

回读模式下,主要用于模拟测试时及记录器回收时对数据进行回读。与存储模式相似,首先发送CMD16设置读取块数;再发送CMD18设置读取起始地址,同时通过LVDS接口芯片将数据输出到计算机,用于数据判读。如果外部控制命令一直存在,系统会读取所有容量的数据;当控制命令不存在,则退出回读模式。

3 系统验证与分析

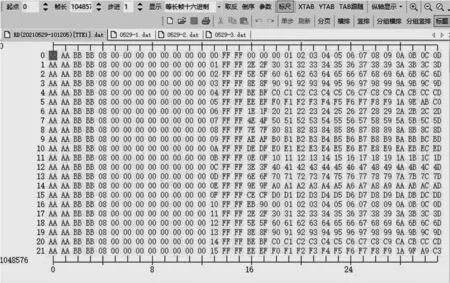

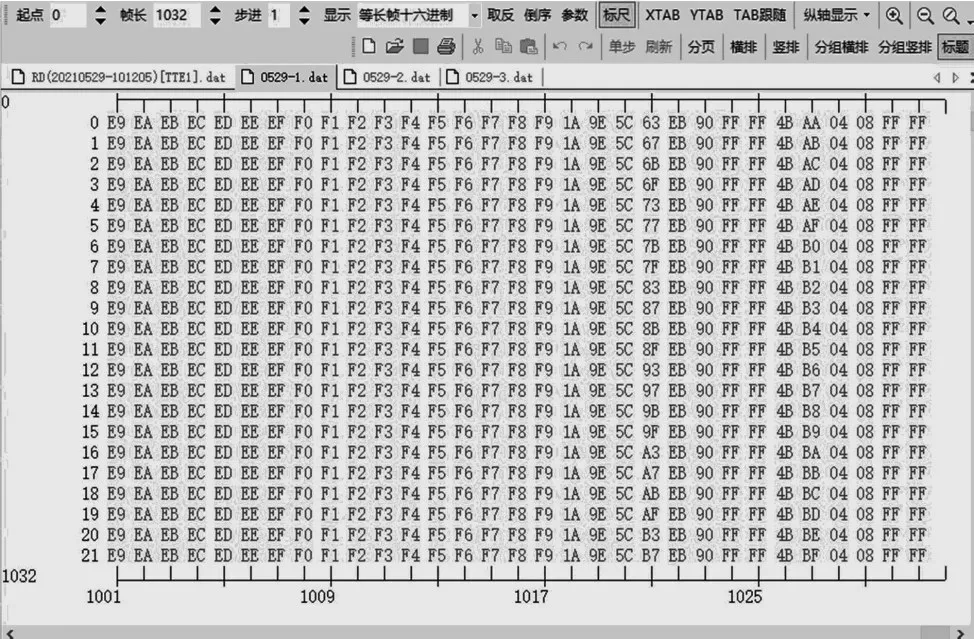

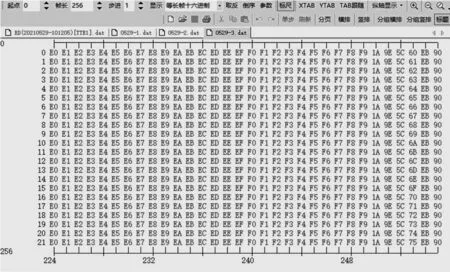

为验证记录器的可靠性和数据记录的准确性,本文采用地面信号源作为模拟数据设备,模拟数据格式如图3所示,发送速率为526 Mb/s,在记录模式下持续写入数据,通过地面回读设备回读数据,原始数据见图11。将单次申请存储容量设置为1 MB,即1 048 576 B,将帧长设置为1 048 576 B,帧头对齐,可通过数据软件直观查看。经数据分析软件第1次拆解,分析数据帧头计数值连续,并去掉帧头,拆解出以太网打包数据,格式见图4,拆解后数据见图12。因每包含数据1 024 B和帧尾8 B,所以将帧长设置为1 032,可以看到帧尾内的帧计数、帧长度、隔离码。经数据分析软件验证后,确定以太网包计数连续没有出现丢包情况,做第2次拆包,提取出实际数据。实际数据如图3所示,拆解后数据见图13。因数据为连续输入,且帧尾前包含包计数,经数据分析软件验证后,无误码。验证了本系统记录数据的准确性。本记录器连续做大于100次地面试验,在记录模式下每次记录容量大于30 GB,同时验证硬启动模式。经数据软件判读,无错误出现。

图11 原始数据

图12 第1次拆解数据

图13 第2次拆解数据

4 结 论

本文介绍了抗高过载千兆以太网数据记录器设计,实现了单路千兆网数据记录,记录速率为526 Mb/s。

该记录器能够准确地回收数据、拆解出原始数据,通过型号项目验证,其具备60 MB/s的平均存储速度。将存储单元与主板分离适用于弹上狭小空间,有利于设计抗高过载结构,可抵抗高过载冲击,能够满足弹上的以太网数据记录及测试要求。