叠层芯片粘接强度与剪切强度试验研究

2022-09-17王世楠万永康闫辰侃张凯虹虞勇坚

王世楠,万永康,闫辰侃,张凯虹,虞勇坚

(中国电子科技集团公司第五十八研究所,江苏 无锡 214000)

随着集成电路技术的发展,摩尔定律受到前所未有的挑战。人们日益认识到在单一芯片集成更高密度的电路越来越困难,三维集成技术被认为是超越摩尔定律,成为持续实现器件小型化、高密度、多功能化的首选方案。硅通孔(TSV)、再布线(RDL)等技术由于可靠性低等因素影响,在军用及航天领域的应用受到限制,而叠层封装技术由于其高成熟度,在这些领域得到广泛的应用。军用及航天等领域的产品在应用过程中要经历多种特殊的力学环境,对所采用的关键器件的力学可靠性要求较高。在国军标和美军标的微电子器件试验方法和程序(GJB548B—2005、MIL⁃STD⁃883K)中,对此类高可靠气密性封装器件均要求进行相关力学试验,如粘接强度试验和剪切强度试验。但在实际科研生产中,对这两类试验的选用存在不清晰的现象。本文基于两款叠层芯片,对其粘接强度试验和剪切强度试验的选用展开研究。

1 标准分析

1.1 试验标准

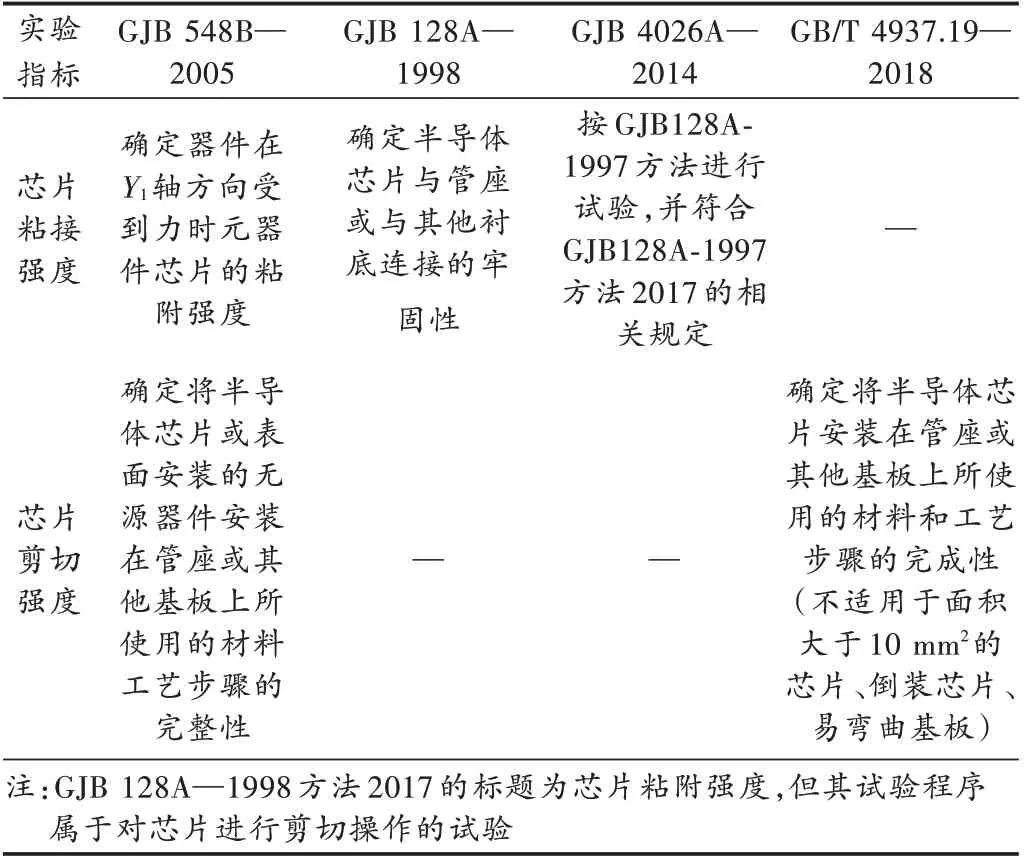

国内外有许多标准对微电子器件的剪切强度和粘接强度进行规定,如国军标GJB 548B—2005、GJB 128A—1998、国标GB/T 4937.19—2018及美军标MIL⁃STD⁃883K、MIL⁃STD⁃750E等。这些标准对芯片粘接强度试验与芯片剪切强度试验分别都有详细的规定,具体内容如表1所示。

表1 几种标准对两类试验的规定

从表1所列出的各标准中对于芯片粘接强度和芯片剪切强度的规定来看,这两项试验的本质都是针对外部载荷对于连接芯片(及无源器件等)与管座、衬底或基板的材料的力学强度试验。

以军用标准中最常使用的GJB 548B—2005为例,其中对于芯片粘接强度试验,主要针对器件在轴方向受到力时的粘附强度;对于芯片剪切强度试验,主要针对器件在或者轴(一般为针对长边)方向受到力时材料的工艺步骤的完整性(即粘附强度)。GJB 548B—2005关于施力方向的取向如图1所示。

图1 GJB 548B—2005关于施力方向的取向

综上,芯片粘接强度试验与芯片剪切强度试验在相关标准的规定及选用上存在不清晰的现象。

1.2 载荷曲线

以GJB 548B—2005为例,设芯片粘接面积为,载荷为,对芯片粘接强度试验和剪切强度试验的载荷曲线进行分析。

1.2.1 芯片粘接强度试验

芯片粘接强度试验的载荷曲线根据以下公式计算:

以下情况应判定为失效:

1)<1.0时发生脱离;

2)1.0 <<2.0时发生脱离,且在芯片与底座间无明显残余。

1.2.2 芯片剪切强度试验

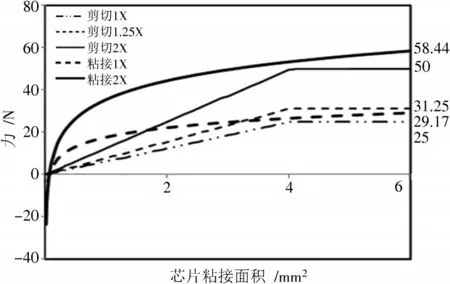

芯片剪切强度试验的载荷曲线如图2所示。

图2 芯片剪切强度载荷曲线

以下情况应判定为失效:

1)当<1X时发生脱离;

1.2 精液采集 男方禁欲3~7 d,手淫法收集精液到无菌取精杯中,37 ℃水浴中液化。采用计算机辅助精液分析系统(北京伟力WLJY-9000)分析精子浓度、活力,根据精液体积计算精子总数、前向运动精子总数。精子总数=精子浓度×精液体积,前向运动精子总数(TMS)= 精子浓度×精液体积×前向运动精子率。

2)当1X≤<1.25X时发生脱离,同时芯片在附着材料上的残留小于附着区面积的50%;

3)1.25 X≤<2X时发生脱离,同时芯片在附着材料上的残留小于附着区面积的10%。

由图2可知:当>4.13 mm时,应承受最小25 N或其倍数的力;当0.32 mm≤≤4.13 mm时,通过图1确定;当<0.32 mm时,应承受最小力为6 N/mm(1X)或其倍数。将芯片粘接强度与芯片剪切强度试验载荷曲线整合,如图3所示。粘接强度载荷恒大于剪切强度载荷,且>4.13 mm时,粘接强度载荷持续增加,剪切强度载荷保持不变。

图3 载荷曲线整合图

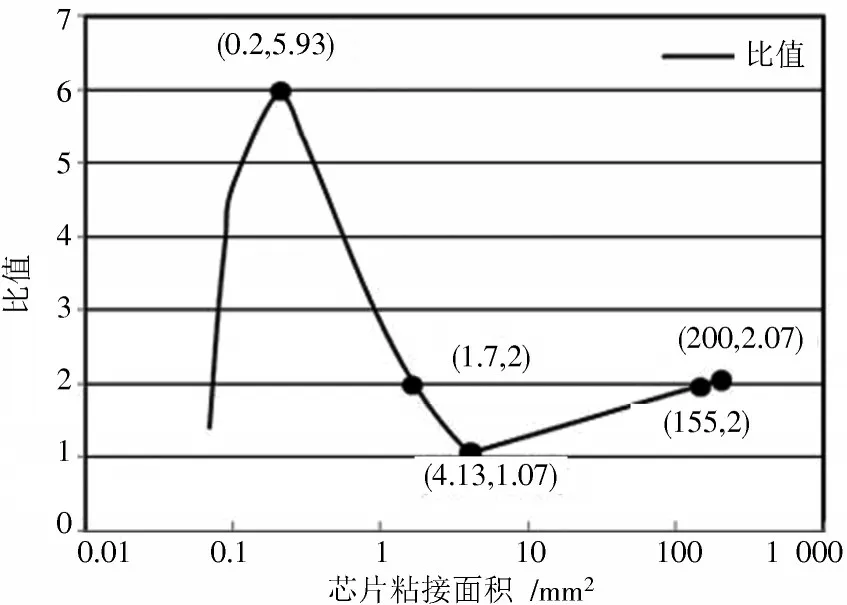

将芯片粘接强度与芯片剪切强度载荷曲线相除,建立两项试验的比值图像进行进一步分析,如图4所示。

图4 芯片粘接强度与芯片剪切强度载荷比值曲线

通常认为芯片面积≥0.1 mm,由图4可知,芯片粘接强度与剪切强度载荷比值随着芯片粘接面积的增大,呈现先增大、后减小、再增大的趋势。当=0.2 mm时,比值达到最大值,为5.93;当=4.13 mm时,比值最小,为1.07;当=200 mm时,比值为2.07。由图4可知,当芯片粘接面积较大或较小时,芯片粘接强度与剪切强度载荷存在较大差距;当≤1.7 mm或≥155 mm时,比值达到2倍以上。两项试验的载荷施加方式存在差别,要研究两项试验的实际考核效果,需对芯片及粘接材料具体受力状态进一步分析。

2 试验及仿真

2.1 芯片试验对比

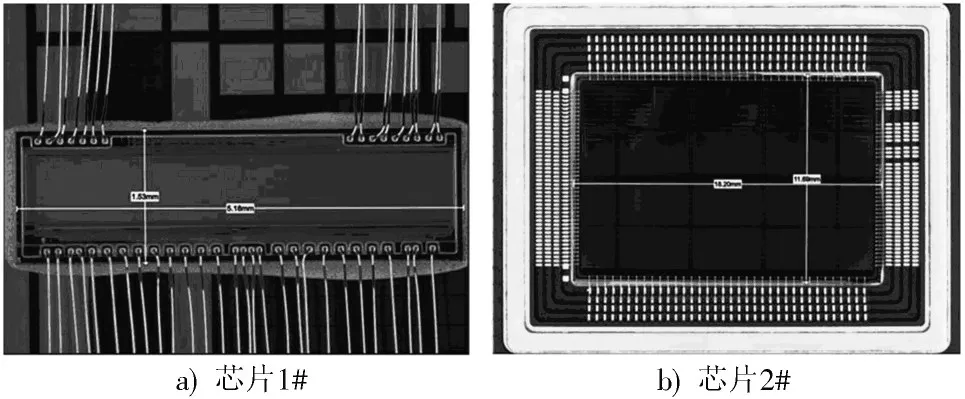

两颗芯片编号分别为芯片1#与芯片2#,如图5所示。其中芯片1#上层芯片面积为7.9 mm,芯片2#上层芯片面积为212.8 mm。根据图3确定芯片1#和芯片2#的载荷强度,如表2所示。对芯片1#与芯片2#分别进行粘接强度与剪切强度试验,均施加2倍载荷,结果显示,两颗芯片试验结果均为合格。

表2 试验载荷强度

图5 叠层芯片

2.2 仿真对比

2.2.1 模型建立

根据芯片封装设计图建立三维模型,由于芯片粘接强度与剪切强度试验主要对芯片、管壳及粘接材料进行研究,因此对无关结构如键合丝等进行简化,如图6所示。

图6 三维模型示意图

表3 芯片主要材料特征参数

2.2.2 边界条件

分别建立以下边界条件:

1)芯片1#粘接强度,对芯片1#上层芯片上表面施加62 N垂直拉力;

2)芯片1#剪切强度,对芯片1#上层芯片短边施加50 N水平剪切力;

3)芯片2#粘接强度,对芯片2#上层芯片上表面施加104 N垂直拉力;

4)芯片2#剪切强度,对芯片2#上层芯片短边施加50 N水平剪切力。

2.2.3 仿真结果与分析

芯片1#和芯片2#的粘接强度、剪切强度仿真结果云图如图7所示。仿真结果如下:图7a)中应力沿上层芯片与基板结合边缘处呈对称状均匀分布,最大应力值为23.051 MPa,出现在边角处;图7b)中应力沿着受力的长边一侧分布,为主要受力部位,中间及另一边应力极小,应力最大值位于上边侧上层芯片与管壳结合的边角处,最大值为102.23 MPa;图7c)中应力沿上层芯片与中间转接板结合边缘处呈对称状均匀分布,最大应力值为68.368 MPa,出现在边角处;图7d)中应力沿着受力的长边一侧分布,为主要受力部位,中间及另一侧应力极小。应力最大值位于长边侧上层芯片与中间转接板结合边角处,最大值为36.257 MPa。

图7 仿真结果云图

从应力状态来看,芯片1#的剪切强度最大应力值为粘接强度最大应力值的4.4倍;芯片2#的剪切强度最大应力值为粘接强度最大应力值的0.53倍。结合图2载荷曲线分析可知:对于面积较小的芯片,建议使用剪切强度试验进行考核;面积较大的芯片,使用粘接强度试验进行考核。

3 结 语

本文基于叠层芯片对粘接强度与剪切强度试验展开研究,将相关标准中两项试验的载荷曲线整合,并通过试验及仿真进行对比分析。结果表明:对于小面积芯片,建议使用剪切强度试验进行考核;对于大面积芯片,建议使用粘接强度试验进行考核。