基于FPGA 和USB 3.0 的超高速数据传输系统设计

2022-08-15王鑫幕芦夜召孟立凡赵凯明

王鑫幕,芦夜召,孟立凡,赵凯明

(1.中北大学 仪器科学与动态测试教育重点实验室,山西 太原 030051;2.电子测试技术重点实验室,山西 太原 030051;3.中北大学,山西 太原 030051)

0 引 言

随着USB接口技术的不断发展和移动数据与测试数据技术的提升,USB 2.0 接口最高传输速度为30 MB/s,但无法匹配测试速度。继续使用USB 2.0 产品不仅影响实验测试的高精度、高效率,而且严重影响人们的日常生活体验。USB 3.0 接口的出现使该问题得到大大改善,并且USB 3.0 向后兼容了USB 2.0,因此对USB 3.0接口数据传输进行研究极其重要。相比USB 2.0,USB 3.0有更高的传输速度、更低的功耗和向下兼容2.0 等优点。USB 3.0 最大传输速度达到5 Gb/s(即625 MB/s),是USB 2.0 传输速度的10 倍,具有很好的发展前景。

本文采用CYUSB3014 芯片,设计一种基于FPGA、SLIVEFIFO工作模式和USB 3.0的高可靠性、高速数据传输系统。经测试,本文系统的传输速度可达320 MB/s,并且在该速度下能够长时间稳定工作,满足现有工业场合的大批量数据传输要求。

1 系统总体设计

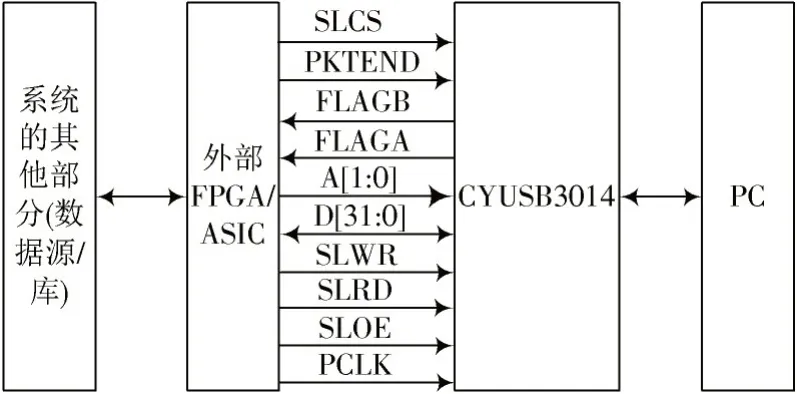

本系统采用模块化设计,主要由电源模块、FPGA控制模块和USB 3.0 数据传输模块组成,通过Cypress 官方固件给FPGA 发送命令进行数据传输。数据传输系统总体设计框图如图1 所示。

图1 数据传输系统总体设计框图

2 硬件电路设计

2.1 同步从设备FIFO 接口设计

在外部处理器访问CYUSB3014 中数据缓冲区的应用场合下,可以使用同步从设备FIFO 接口技术。同步从设备FIFO 接口的灵活使用,可以满足高吞吐量数据传输的要求。在包模式数据的快速传输过程中,使用该接口能够有效缓存数据,保证包模式下数据的连续性,提高数据传输的可靠性指标。因此,本文所述系统或模块均使用同步从设备FIFO 接口设计,如图2 所示。

图2 同步从设备FIFO 接口示意图

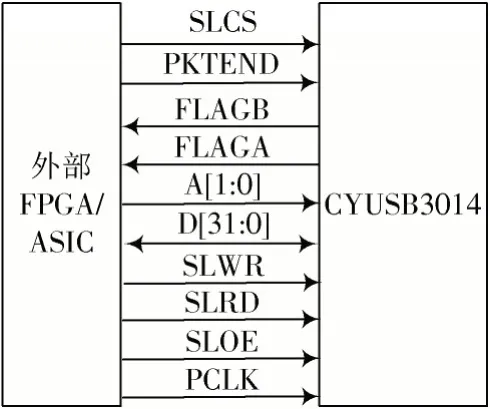

2.2 电源电路设计

本文采用USB 3.0 接口供电,供电电压为5 V。因为FX3 芯片内部各模块要求的供电电压不同,所以需要使用不同的电路将5 V 的电压转换为各模块所需的工作电压,且输入电流要满足900 mA 的条件。针对电路的供电电压需求,最终选用TPS650243 电源芯片。该芯片采用锂电子供电技术,内部集成压降转换器和LDO稳压器,而且还有热关断保护功能,可以满足本文系统需求。电源电路如图3 所示。

图3 电源电路

设置外围电路可以得到不同的输出电压值,其中VDCDC 输出电压和电阻配置关系如下:

式中:,为电压值,单位为V;,为电阻值,单位为Ω;为默认电压,一般为0.6 V。通过计算,配置相应的电阻就可以得到所需的输出电压。

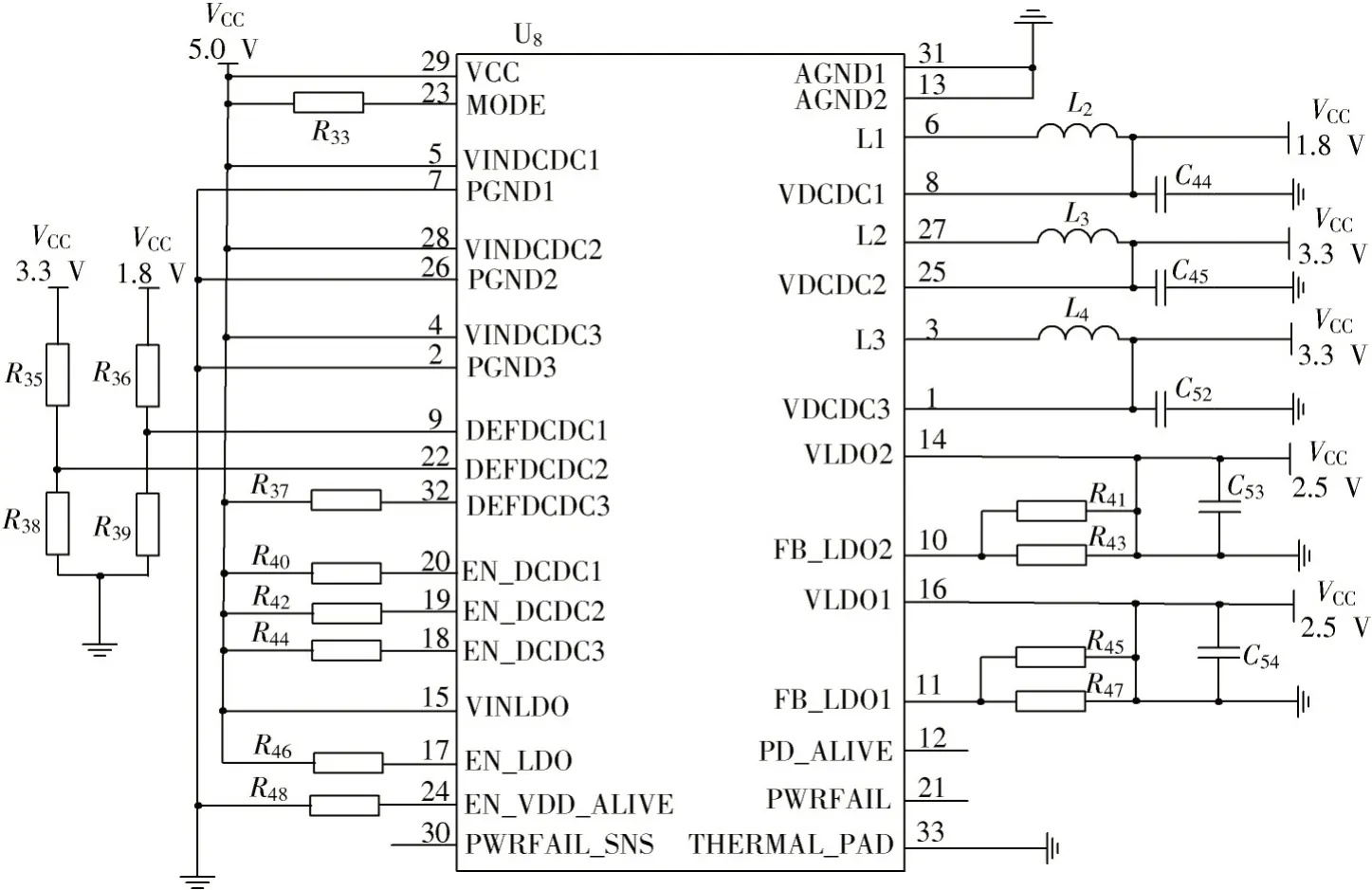

2.3 USB 接口电路设计

本 文 设 计 采 用USB 3.0 标 准B 型 接 口,该 接 口 扁平小巧、支持热插拔、强度高、寿命长,相对于其他类型的接口更普遍、通用性更好。接口电路如图4 所示。VBUS 引脚可以承受6 V 的电压,在USB 3.0 插座上的“屏蔽”引脚通过接一个2.2 mH 电感BLM21P 与0.1 mF电容的并联电路,然后接地可以实现隔离屏蔽的作用。在本系统中,采用四通道的RCLAMP0524J 作为两对差分数据线(SSRX+/SSRX-和SSTX+/SSTX-)的外部ESD器件来防静电保护,以此来降低静电对系统性能的影响。其中RCLAMP0524J 具有低功耗、高性能等优点。

图4 USB 接口电路

2.4 USB 3.0 逻辑设计

2.4.1 同步从设备FIFO 读序列

同步从设备FIFO 接口进行读取操作的时序为:激活片选信号SLCS#;激活输出使能信号SLOE#,驱动数据总线;激活SLRD#信号,同时FIFO 指针在PCLK 上升沿到来时更新,启动重新寻址的FIFO 至数据总线的数据传输,经过的传输延迟时间后即可得到最新的数据。

2.4.2 同步从设备FIFO 写序列

同步从设备FIFO 接口进行写操作的序列为:激活片选信号SLCS#;外部主设备或外设将数据传输到数据总线上;激活SLWR#信号,在PCLK 上升沿时将数据写入到FIFO 中,并且FIFO 指针递增,指向下一个FIFO。

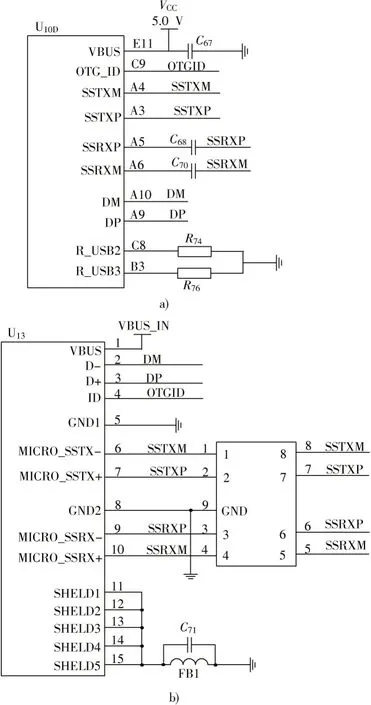

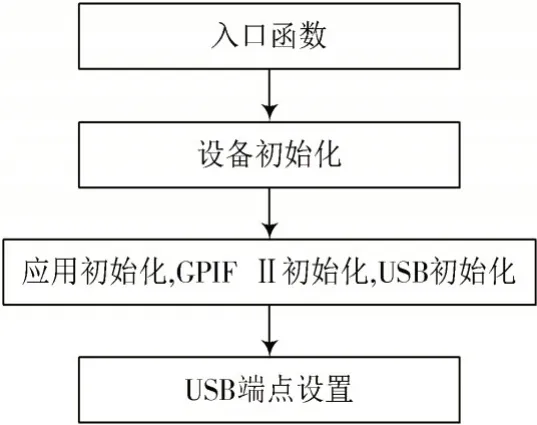

3 固件设计

固件是与硬件电路联系最为密切的应用程序之一,开发难度大、周期长,而且还需要具有丰富的固件设计经验。为快速开发固件应用,固件框架成为了最好的选择。本系统采用Cypress 公司的CYUSB3014 芯片,在USB 固件设计中使用Cypress 提供的SDK 开发包,其中包含固件框架和应用变成接口函数库。FX3 固件框架程序流程如图5 所示。

图5 FX3 固件框架程序流程

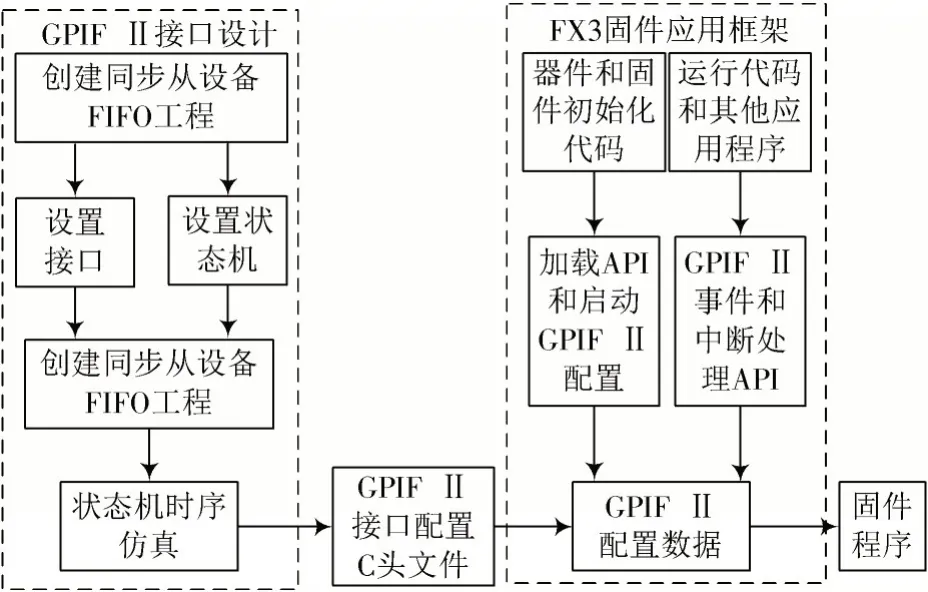

固件设计主要分为两部分:一是用GPIF ⅡDesigner 工具设计FPGA 和USB 接口部分,通过编译生成一个GPIF Ⅱ接口的C 头文件;二是用Eclipes 工具编译固件框架,把头文件加到固件工程中,通过API 接口函数实现固件应用程序。FX3 的固件框架如图6 所示。

图6 FX3 的固件设计框图

为实现数据双向传输,需要创建2 个DMA 通道,分别作为读、写操作的传输通道,按图2 所示连接。用GPIF ⅡDesigner 工具进行接口设计,定义的接口界面如图7 所示。

图7 GPIF II 接口的接口界面

4 结 论

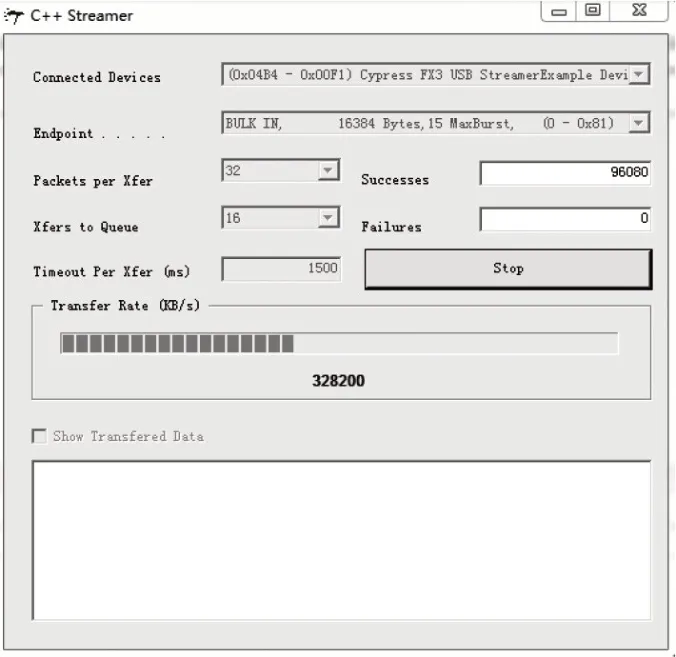

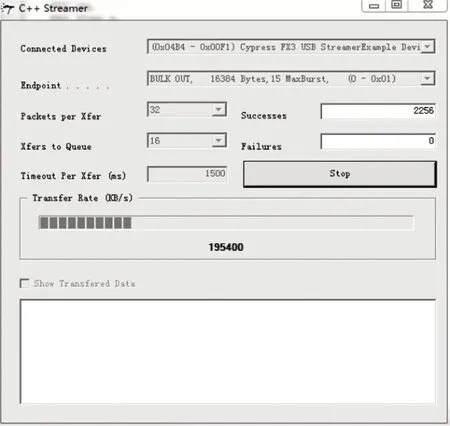

在串流IN 传输时,FPGA 等待FLAGA 变为1;当缓冲区可用时,FPGA 立即将数据连续写入到FX3 的PIB_SOCKET_0。串流IN 传输速度如图8 所示。

图8 串流IN 传输速度

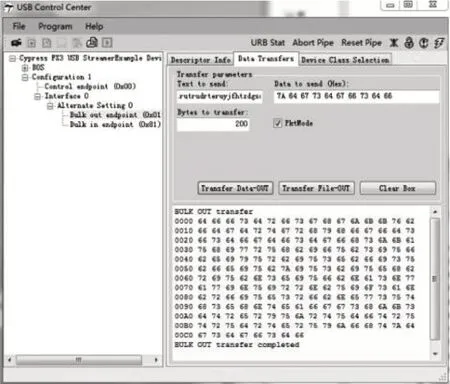

FLAGA 和FLAGB 是EZ⁃USB FX3 的DMA buffer 的空满状态标志信号,由FX3 的固件控制。当FLAGA 信号为高电平时,进入Stream_IN 传输模式,FLAGB 信号也为高电平时意味着Socket buffer 为空,此时FPGA 拉低SLRD 信号线,并向FX3 的CYUSB3014 套接字缓冲区写入数据,同时启动DMA 通道;当缓冲区写满数据后,FLAGA 拉低,调用DMA 回调函数,数据从U 口上传到PC 端。在串流OUT 传输时,FPGA 等待FLAGC 变为1,当缓冲区可用时,FPGA 立即连续读取FX3 的PIB_SOCKET_3 中的数据。包模式下用PC 向FPGA 传输数据,如图9 所示,串流OUT 传输速度如图10 所示。

图9 包模式下串流OUT 传输

图10 串流OUT 传输速度

5 结 语

本文介绍一种基于USB 3.0 同步从设备FIFO 的高速数据传输系统,并通过多次数据传输验证得出,该系统高速传输数据稳定,能够满足各种视频信号及大数据传输的需求,可应用于大容量数据处理系统中。USB 3.0配合DDR 可达到更高的传输速度,更加实用,可以继续深入开发。