支持9种工作模式的ARM寄存器堆结构设计方法

2022-08-04章复嘉谢澄扬高顶冲

章复嘉, 谢澄扬, 高顶冲, 樊 谨

(杭州电子科技大学 a.计算机国家级实验教学示范中心; b.计算机学院; c.圣光机联合学院,杭州 310018)

0 引 言

长期以来,国内计算机专业在人才培养上存在偏差,导致底层架构设计和系统软件开发的高端人才极为匮乏。“人才”成了国内计算机行业发展的“终极瓶颈”,重视基础研究人才培养成为了国家战略[1-5]。危机也是契机,“卡脖子”事件促进了国内IT龙头企业开展校企合作办学、共建课程等项目[6-7]。制裁和系统能力培养需求等多种原因促进了国内高校计算机体系结构课程改革。

在这样的时代背景下,全国各大高校与国际同步,纷纷开展继MIPS之后新一代教学模型机结构研究,RISC-V和ARM是新一代教学模型机研究的两大方向[8-13]。

袁春风等[14]率先出版了基于开源架构的RISC-V版《计算机组成与设计》教材。陈微[15]翻译了图灵奖得主David A.Patterson等改版的经典教材《计算机组成与设计(硬件/软件接口)(ARM版)》。国内多所双一流和985高校基于开源的RISC-V架构,设计、研究了教学模型机和配套的实验教学方案。

目前国内《计算机组成原理》课程采用的主流CPU架构,包括处于研究前沿的RISC-V和Legv8(即ARMv8简化版)教学模型机结构,都与早先的MIPS32结构存在许多相似之处,结构相对简单,不支持类似ARMv7这样多工作模式切换和基于其上的中断优先级等更为高阶和复杂的系统级底层设计实验。

多工作模式是ARM架构CPU的特色,在实现上极具复杂性。开发ARMv7教学模型机并实施教学的意义在于,让学生有机会通过多样化实例,学到更多高端计算机底层设计的方法,促进人才培养国家战略得以更好实现。

9种工作模式是ARMv7及以上架构芯片的重要特点,也是实现ARM模型计算机结构的重点和难点。本文围绕9种工作模式可访问的寄存器范围和逻辑结构,提出一种实现多工作模式寄存器堆的设计方法。对于组成原理课程而言,多工作模式寄存器堆是计算机部件设计的一种新方法。

1 ARMv7架构下通用寄存器使用规则

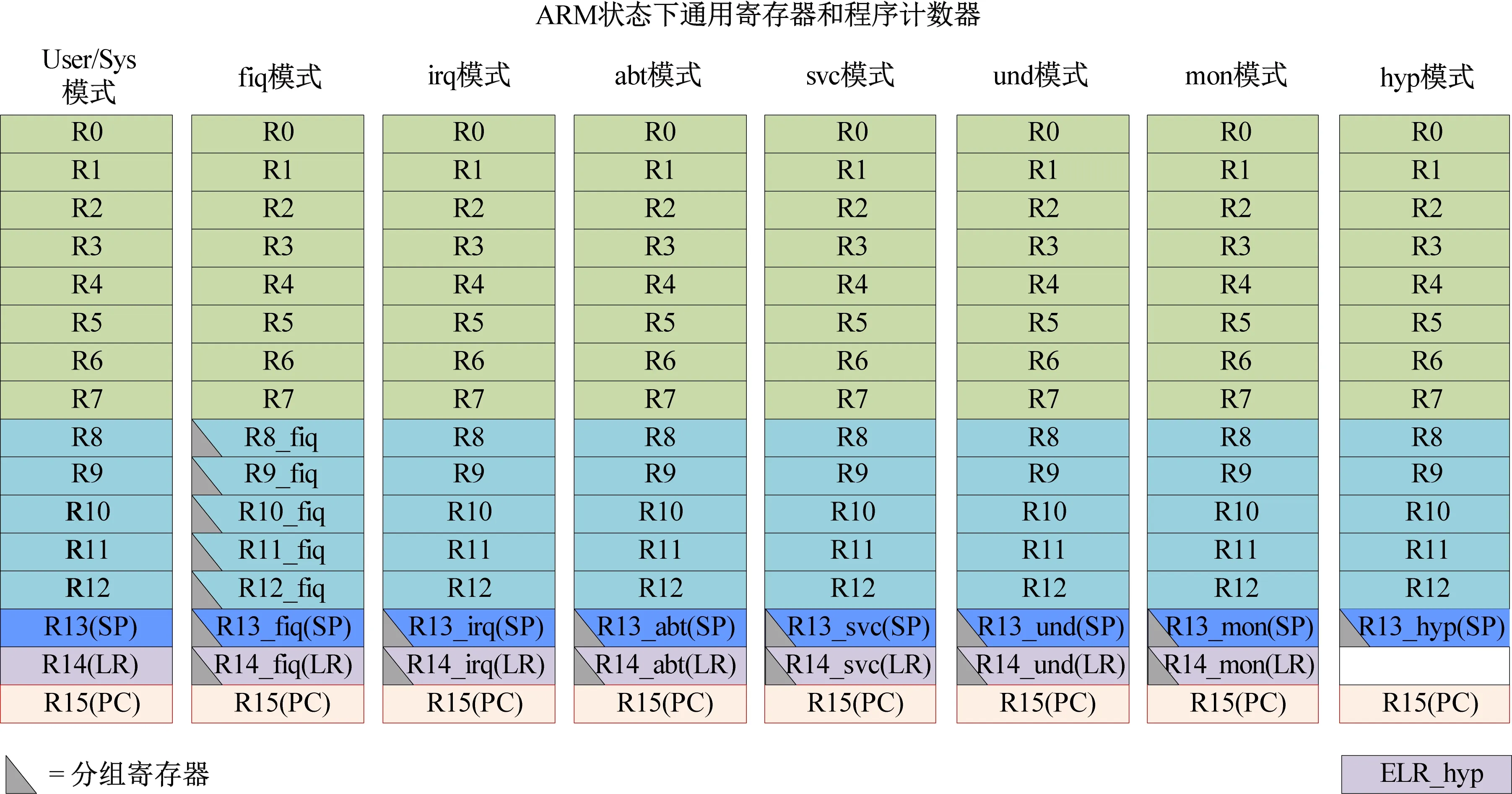

如图1所示,ARMv7架构CPU中,通用寄存器堆包含34个宽度为32 bit的寄存器。ARM状态下有9种工作模式,见表1。当前程序状态寄存器CPSR的最低5 bit二进制M[4∶0]代表当前处理器的工作模式。

图1 ARM状态的9种工作模式下的通用寄存器堆组织

表1 ARMv7 CPU的9种工作模式编码和可访问寄存器范围

R0~R7、程序计数器R15(PC)和当前程序状态寄存器CPSR是所有模式公用的寄存器。R8~R12是除快速中断fiq模式外,其他模式公用的寄存器。除hyp、User和Sys模式外,每种模式都有自己的13、14号寄存器。User和Sys模式访问的逻辑寄存器范围是一样的;hyp模式没有14号寄存器,中断返回地址保存在专用寄存器ELR_hyp里。

2 支持9种工作模式的通用寄存器堆设计

2.1 读/写端口设计

ARMv7指令集中有部分指令需要同时读出3个寄存器的值,写入1个寄存器,需要将通用寄存器堆设计成3个读端口和1个写端口。因程序计数器PC(即R15)的特殊性,在实验教学方案中可单独设计读/写控制逻辑。

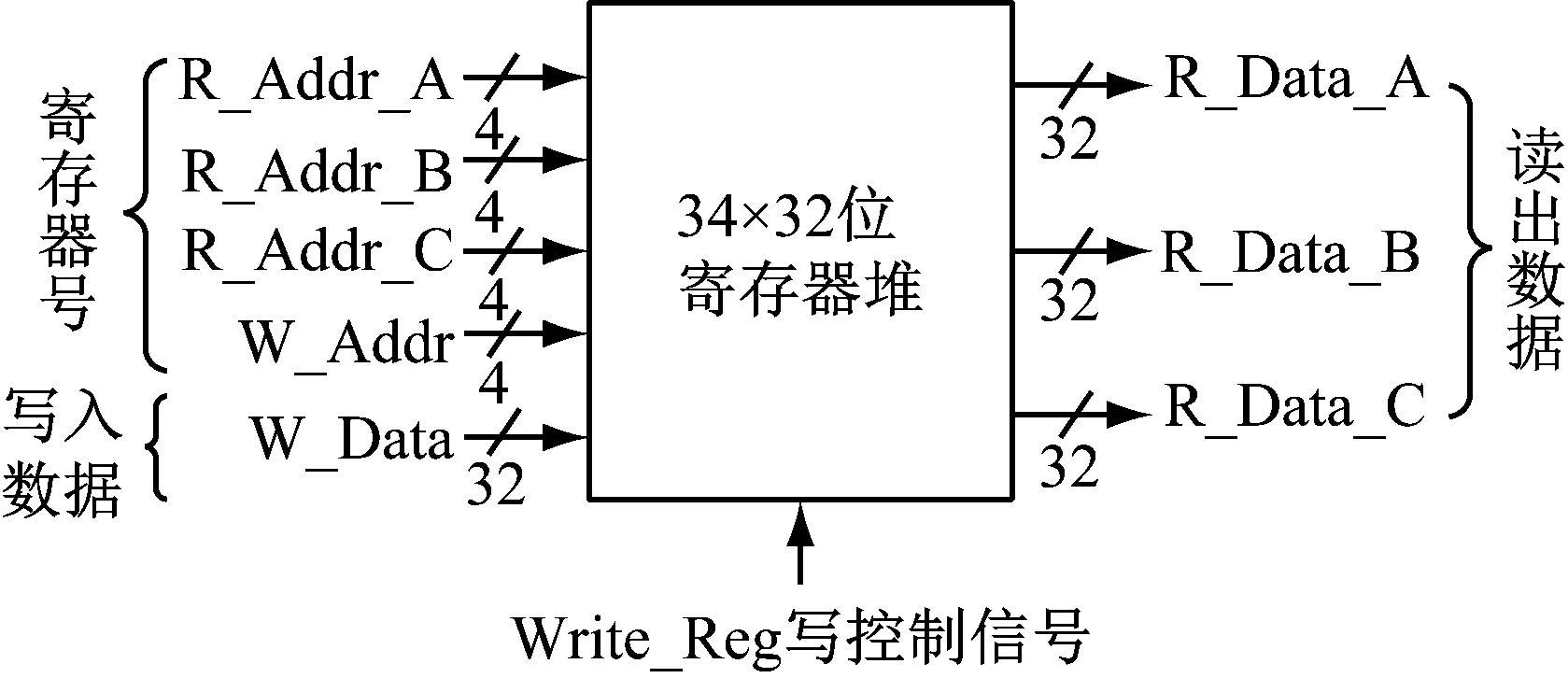

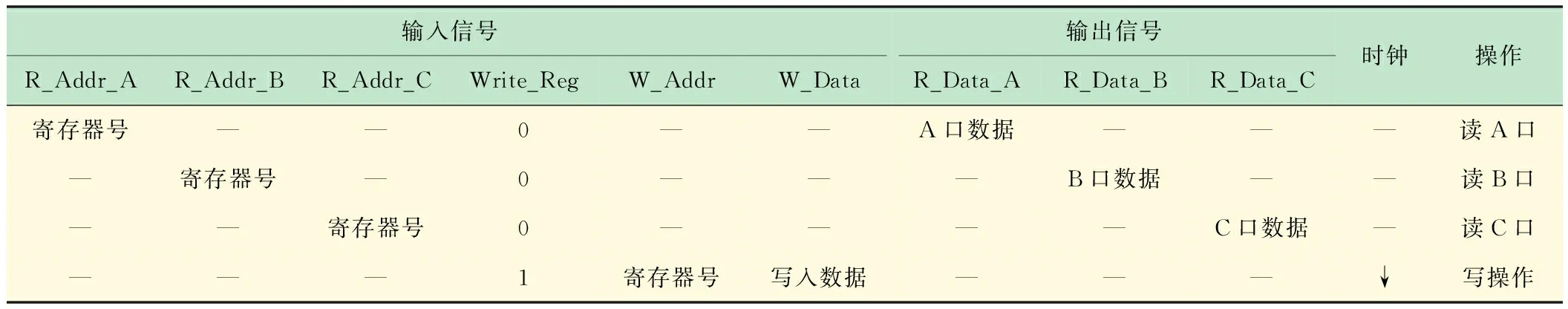

图2为通用寄存器堆模块的读/写端口示意图,表2为其功能表。宽度为4 bit的R_Addr_A、R_Addr_B和R_Addr_C分别寻址3个读端口对应的寄存器号,读出的32 bit数据由R_Data_A、R_Data_B和R_Addr_C分别输出。寄存器由边沿型D触发器实现,读访问时,无须使能或者时钟信号控制,给出寄存器地址,便可读出寄存器中的数据。在时钟下降沿写入寄存器,要求同时写控制信号Write_Reg必须有效,才能将数据写入寄存器。写操作的条件是:写寄存器地址W_Addr、写入数据W_Data和写控制信号Write_Reg,必须在时钟下降沿有效。

图2 通用寄存器堆模块读/写端口示意图

表2 通用寄存器堆功能表

用Verilog HDL编程时,建议将通用寄存器堆定义为一个reg类型的数组。对于通用寄存器堆的读操作和写操作的地址译码,只需引用寄存器地址作为数组的下标即可。

2.2 9种工作模式访问寄存器范围设计

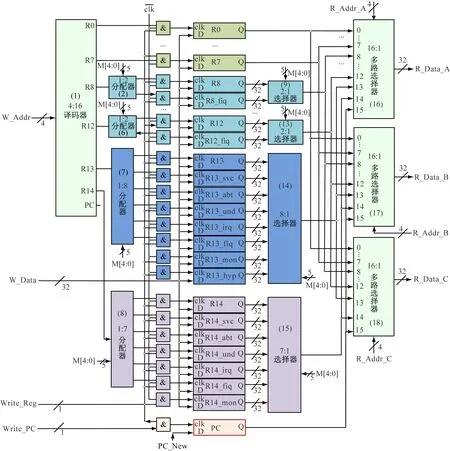

支持9种工作模式的通用寄存器堆内部结构如图3所示。工作模式位的最高位M[4]必须为1,它可用作(1)~(15)所示的译码器、数据分配器和多路选择器的使能端。

4∶16译码器(1)的作用是选择写端口地址。(2)~(8)这7个分配器的作用是选择写入何种模式下的寄存器,且(2)~(6)的结构一样,(7)、(8)的结构一样。14号寄存器比13号寄存器少一个,即R14_hyp不存在。图3中(16)~(18)这3个16∶1多路选择器的作用是分别根据3个读端口的地址,选择对应寄存器的内容。其左边的(9)~(13)这5个2路选择器结构相同,(14)、(15)这2个16∶1多路选择器的结构相同,(15)的输入比(14)少一个。(9)~(15)这7个多路选择器的作用是将当前处理器工作模式对应的所有寄存器的内容全部读出,然后由(16)~(18)这3个16∶1多路选择器分别送往A~C读端口。

图3 ARM多模式通用寄存器堆结构设计实验原理图

图3中的数据分配器和多路选择器的控制电路与工作模式的对应关系,见表3。表中(1)~(15)的使能端是M[4],当M[4]=1时,(1)~(15)使能。(1)~(15)的选择信号都是M[3∶0]。在M[4]=1的前提下,根据M[3∶0]的取值,数据分配器将要写入的数据分配给指定模式下的寄存器;数据选择器输出指定模式下的寄存器的读数。

表3 分配器和多路选择器控制表

3 教学实施情况

3.1 实验教学方法

采用自研制的RSIE-SPOC硬件实验课翻转教学方法[16],借助自制可交互式FPGA实验板卡和7×24小时开放的远程实验云平台,实施多工作模式寄存器堆设计实验教学。课前学生在网络教学平台上观看实验讲解短视频,按要求完成寄存器堆编程,在远程FPGA平台上调试程序。课上验收实验并让学生按小组交流展示,课后在网络平台上提交实验报告。

3.2 学生作品举例

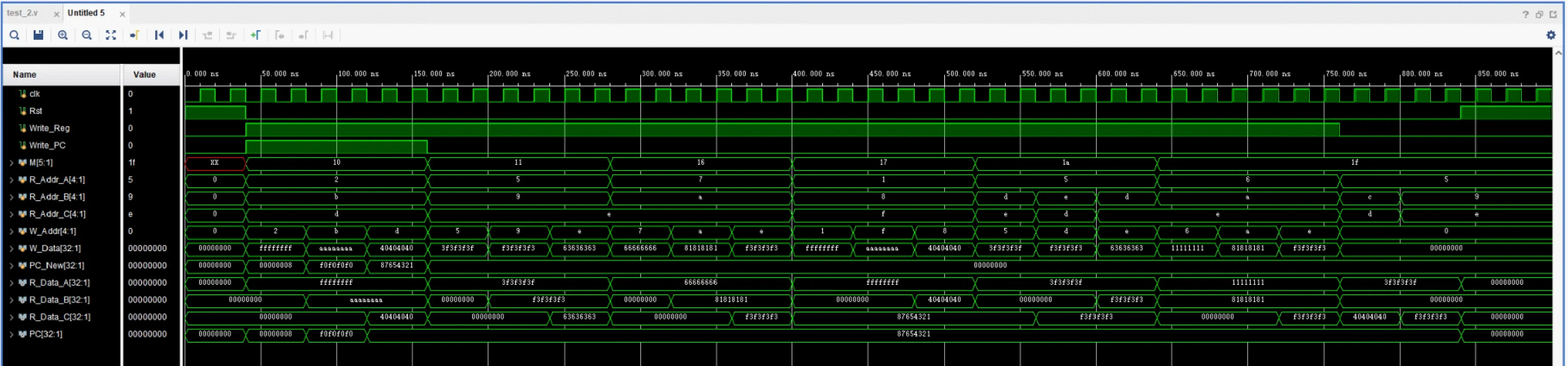

学生用Verilog HDL编程完成设计,并开展仿真调试和板级调试。作品的仿真波形图举例如图4所示。其中M[5∶1]是工作模式位,由图5所示的仿真波形可知,该作品能正确实现读写寄存器的操作,且实现了9种工作模式下访问不同的寄存器范围。

图4 学生作品举例

图5 学生满意度调查

3.3 实施效果分析

2021年,ARM多工作模式寄存器堆设计实验正式投入教学使用。课程调查表明,学生对课程整体满意度达到90%以上,其中90.5%学生认为实验促进了深入理解ARM CPU结构,76.2%学生认为课程提高了对计算机硬件系统的学习兴趣。

4 结 语

支持9种工作模式的ARM寄存器堆结构设计方法是地方高校开展高端模型计算机结构设计的研究成果。实践证明,基于该方法设计的实验教学,促进了学生深入理解ARM CPU结构,促进学生更好地掌握计算机底层设计技术,为进一步实现ARM架构系统级设计实验打下基础。