基于VADL 的8 路抢答器的设计与仿真

2022-07-26邹毅军

邹毅军

(湖北工业大学工程技术学院,湖北 武汉 430000)

随着电子技术的高速发展,EDA(Electronics Design Automation)技术应运而生。电子系统设计者们可以利用EDA 技术,采用“自顶而下”的设计方法,在集成开发环境QuartusII 16.0 内,使用ⅤHDL 语言( Ⅴery-High-Speed Integrated Circuit Hardware Description Language),将电路的硬件设计转化为软件设计[1]。

抢答器在众多场景中均有使用,如电视台智力问答节目、学校组织活动,它是重要的基础设备之一。目前设计抢答器的传统方法非常多,如74LS192 芯片设计,基于52 系列单片机设计等。但传统方法在设计上不够简洁明了,电路可靠性较低。本文以计算机为平台,以5CSEMA5F31C6N 芯片为载体,使用ⅤHDL语言设计出的抢答器,代码简洁明了、使用稳定、可扩展性强。

1 简介

1.1 VHDL 语言

ⅤHDL 语言即“超高速集成电路硬件描述语言”,该语言最早在1982 年由美国军方开发出来。

使用ⅤHDL 语言的优点如下:①语法简单。它类似于一般的计算机高级语言,容易学习,减少设计在使用过程中的错误与开发使用的时间。②泛用性强。ⅤHDL 语言已成为一种电子设计文本输入标准,可以在多种开发工具上使用。

1.2 QuartusII 16.0

QuartusII 16.0 是由Altera 公司出品的第四代PLD(Programable Logic Device)开发平台,它的兼容性强,接口直观易用,编译速度快,广受系统设计者的喜爱[2]。

1.3 5CSEMA5F31C6N 芯片

5CSEMA5F31C6N 芯片由Altera 公司出品,有896个引脚,用户可供自定义的I/O 引脚多。

2 实现功能与设计思路

2.1 8 路抢答器功能

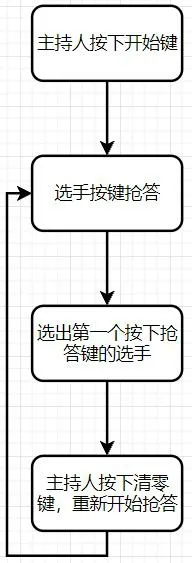

8 路抢答器功能框图如图1 所示。本设计以竞赛为例,其功能如下:①8 路抢答器需要满足8 位选手各控制一个按键进行抢答,故分别记为key0,key1……key7。②主持人需要对抢答器进行控制,如开始抢答与清零。将清零设为rst,开始抢答键设为key_start。③在主持人按下开始抢答键后,选手开始抢答。在一名选手按下抢答按键key0,key1……key7 中的任意按键后,数码管显示该选手的号码,对应号码的LED 灯亮起。其余选手按下按键无反应。④在主持人按下清零键rst 后,下一次抢答重新开始。

图1 8 路抢答器功能框图

2.2 抢答器系统原理

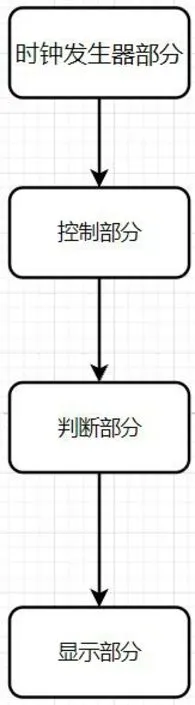

抢答器系统原理框图如图2 所示。根据上述设计的思路与要求,可将该抢答器分为4 个部分:①时钟发生器部分。一个50 MHz 的时钟源给予CLK 信号。②控制部分。该部分让抢答器开始抢答。③判断部分。该部分是该抢答器的核心部分,可以判断是否有选手按下按键,并在第一个选手按下按键后停止。④显示部分。该部分在选手按下按键后会将选手的号码显示在数码管上,并将对应的LED 灯点亮。

图2 抢答器系统原理框图

3 抢答器的VHDL 设计

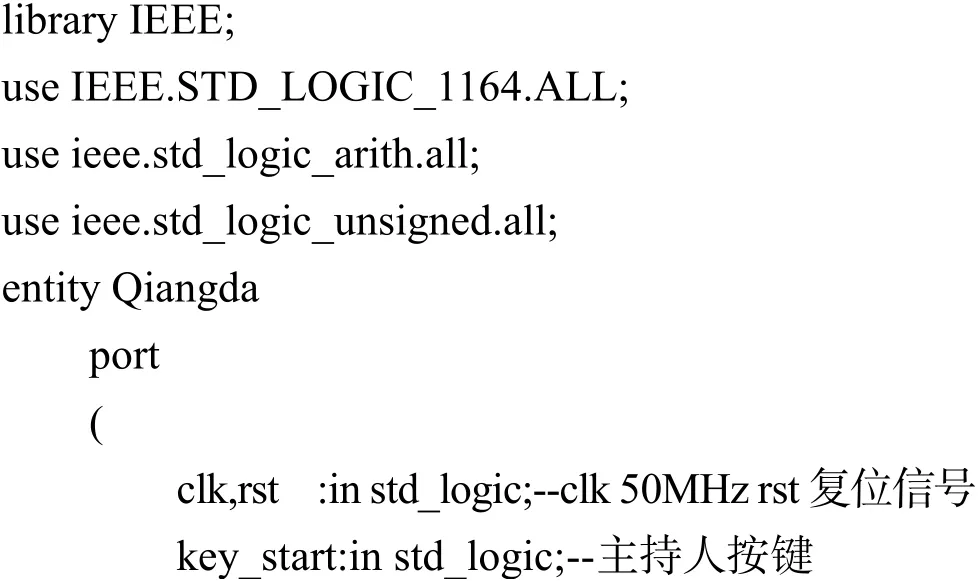

3.1 VHDL 实体部分

在端口部分共设计了11 个输入端口、15 个输出端口。输入端口包括1 个时钟发生器、8 个抢答按键、1个开始按键、1 个清零按键。输出端口包括1 个数码管、8 个LED 灯。

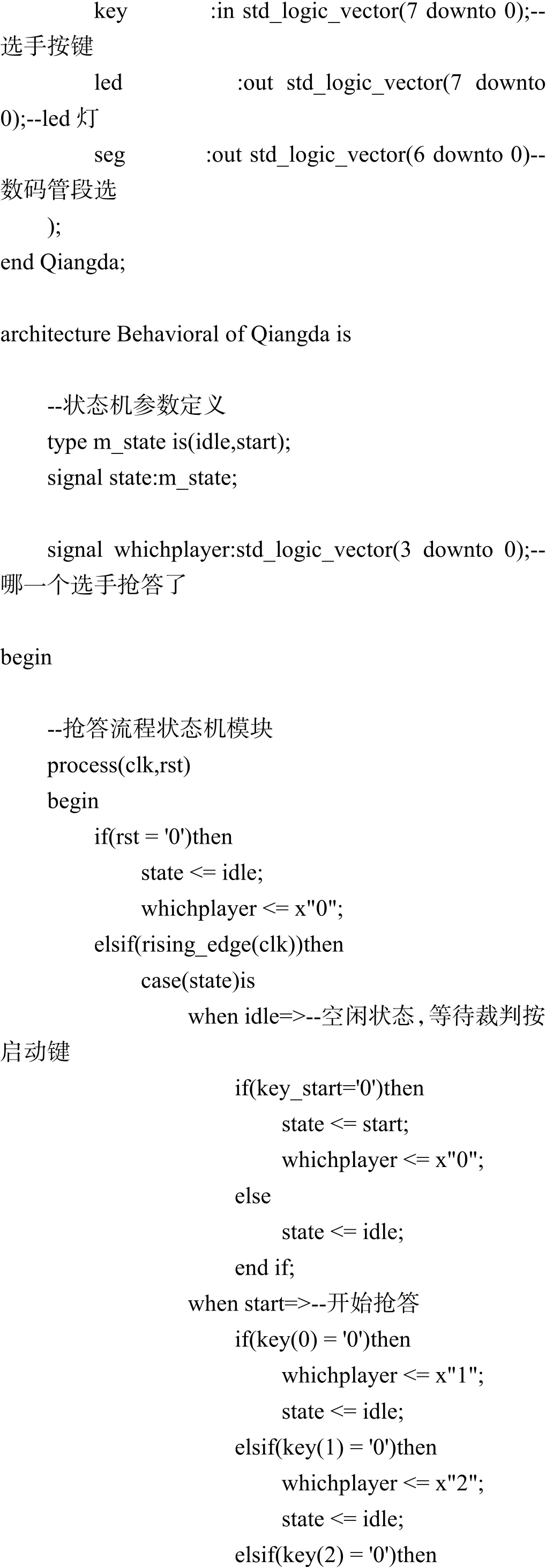

3.2 VHDL 构造体部分

构造体部分以时钟信号、开始与复位按键、抢答按键为敏感信号,当敏感信号变化后,激活程序,顺序执行语句。

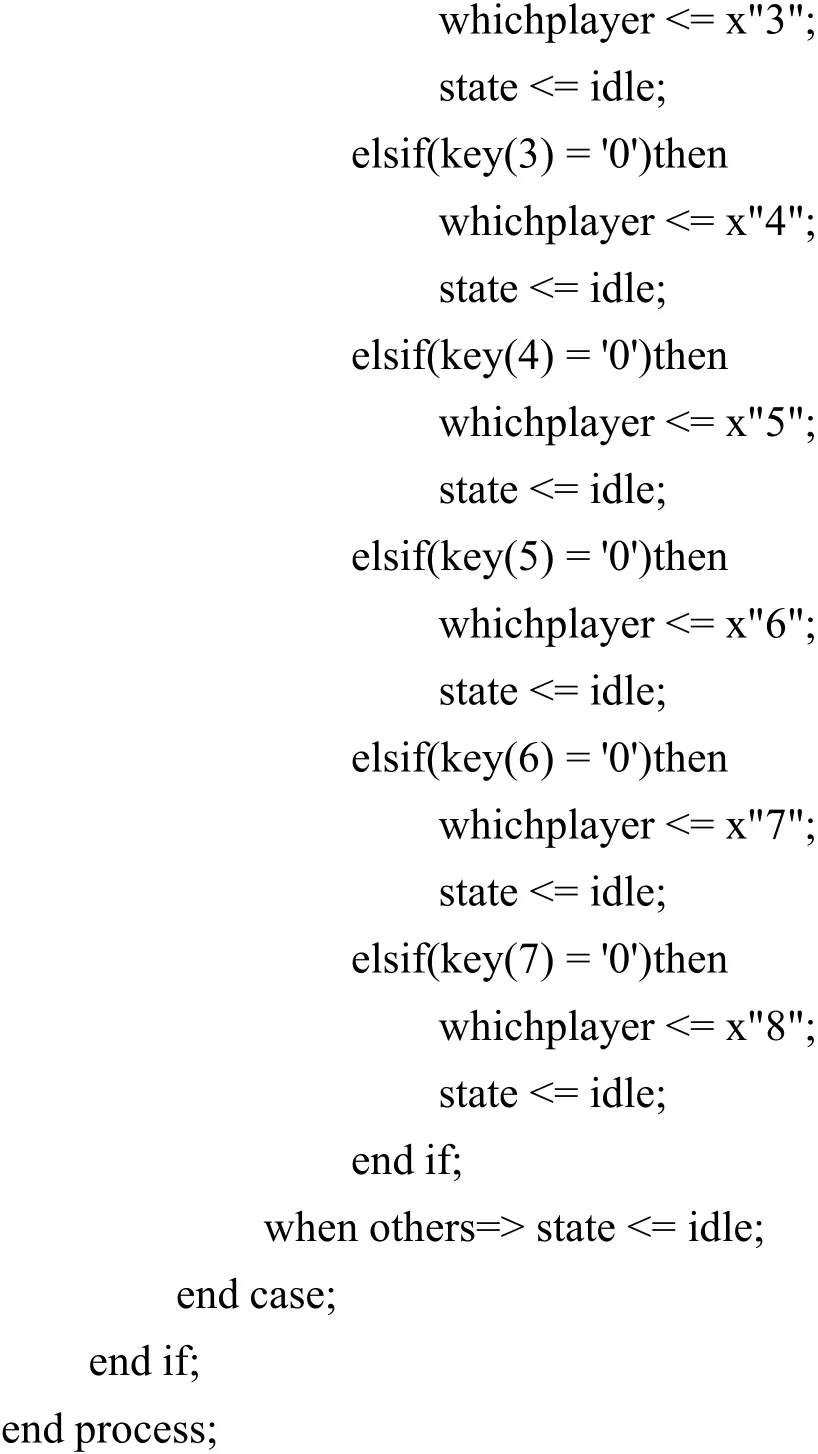

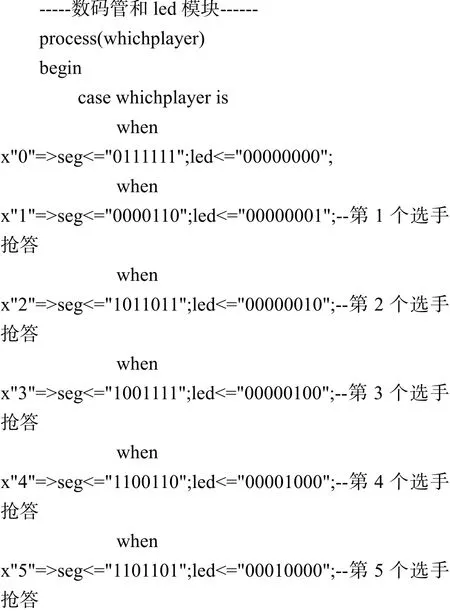

3.3 抢答器整体VHDL 代码

3.4 波形仿真

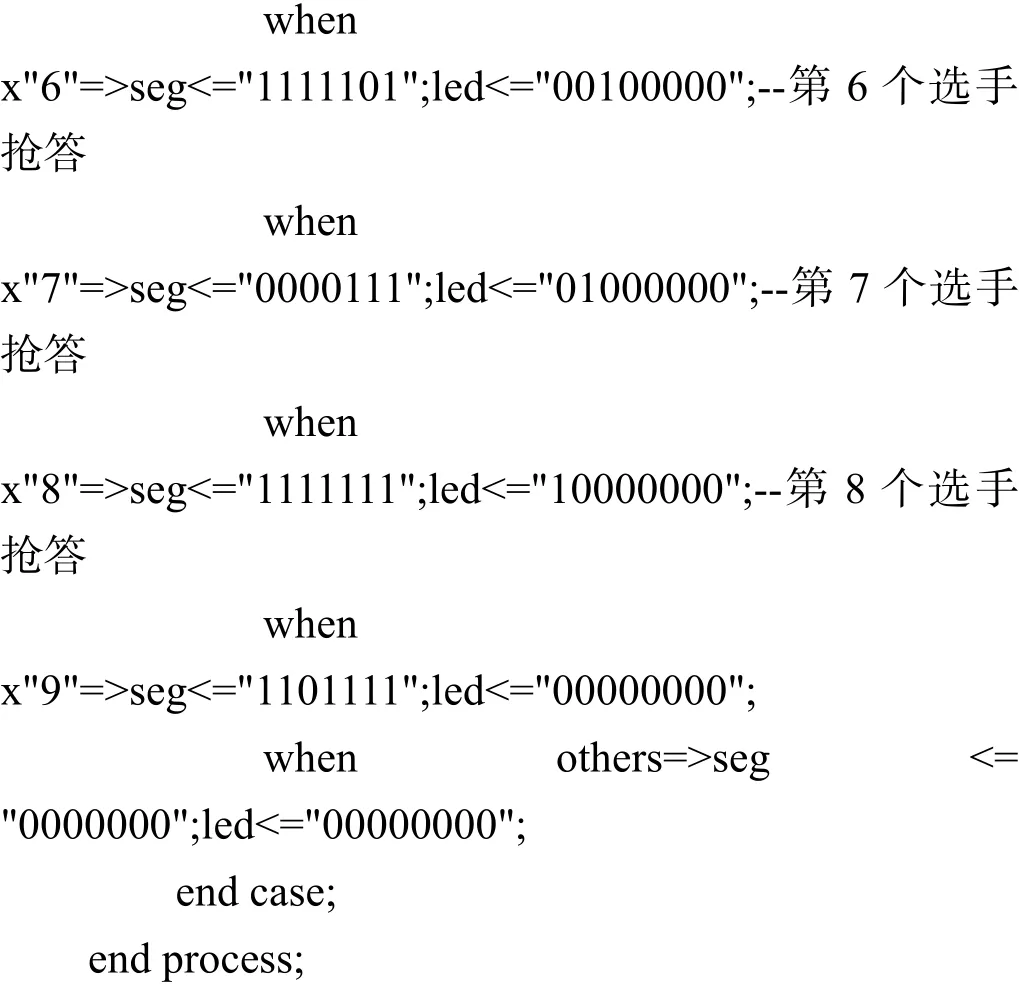

对于一次设计,波形仿真是很有必要的,它可以在下载写入开发板前找出问题。8 路抢答器波形仿真如图3 所示。

图3 8 路抢答器波形仿真图

4 结束语

本文通过集成开发环境QuartusII 16.0,使用ⅤHDL 语言设计了8 路抢答器并实现了抢答器的功能。在使用ⅤHDL 语言进行编程后,使选择器的代码简洁灵活、易于看懂,降低了设计的难度。通过这个实例可以看出,ⅤHDL 语言是自上而下进行设计的,设计方便快捷。