一种非对称欠压锁定电路设计

2022-06-14汪西虎商世广董振斌

张 媛 ,汪西虎 ,商世广 ,董振斌

(1.西安邮电大学 电子工程学院,陕西 西安 710121;2.上海电子线路智能保护工程技术研究中心,上海 201202;3.上海维安电子有限公司,上海 201202)

随着人们生活水平的不断提升,对高性能便携式电子设备的需求逐渐增加,这些便携式电子设备需要电源管理芯片具有更高的效率和可靠性,进而在提高设备性能的同时延长其使用寿命[1-2]。若芯片工作在非正常电压下,会损坏芯片,导致芯片的可靠性降低以及使用寿命减短,因此需要对电源电压进行实时监控[3]。芯片在上电启动时,电源电压通过等效电阻对电容进行充电。随着电源电压逐渐增加,达到芯片系统的工作电压时,芯片开始工作[4]。在芯片开始工作前,由于瞬态电流过大,相当于给电源电压带了一个负载,将电源电压拉低至工作电压以下,这样操作容易导致芯片在工作电压附近频繁地开启、关断。为了避免这类振荡情况的发生,对电源电压进行实施监控,引入欠压锁定(UVLO)电路实现对电源电压的监控以及芯片系统的保护[5-7],并且在电路中加入产生滞回电压的结构,避免因电压波动引起输出信号的异常翻转造成芯片损坏,进而使电源电压具备较高的可靠性。在实际设计中,一般为了提升响应速度,输出级的偏置电流较大,会导致电路功耗很高[8]。

Hiremath 等[5]采用带隙结构UVLO 实现了较低的电路复杂度。Chatterjee 等[8]采用比较器结构实现了超低功耗200 pA,但此结构仅针对超低功耗电源管理芯片。Cho 等[9]采用比较器结构,实现了较低的功耗。

针对上述问题,本文提出了一种低温漂、低功耗的UVLO 电路,其特征是阈值具有滞后性,温漂较小,并且采用0.18 μm BCD 工艺实现。本设计通过两级电压比较器的非对称性产生滞回电压,相较于带隙结构的欠压锁定电路,具有更低温漂、更低功耗的优点,满足电荷泵IC 的设计需求。

1 带隙结构UVLO

在电源管理系统中,UVLO 结构是芯片系统中的重要组成部分[9-10]。当电源管理系统打开时,电源电压从零电位开始增加。当电源电压达到特定值即上门限阈值电压(VIH)时,欠压锁定电路就会输出信号,芯片中其他模块开始工作。若缺少UVLO 电路,某些模块可能会在电源电压供电不足的情况下工作,导致电路故障或损坏[11]。因此,欠压锁定电路能够监测电源电压,确保为芯片内部各个模块提供正常的工作电压。

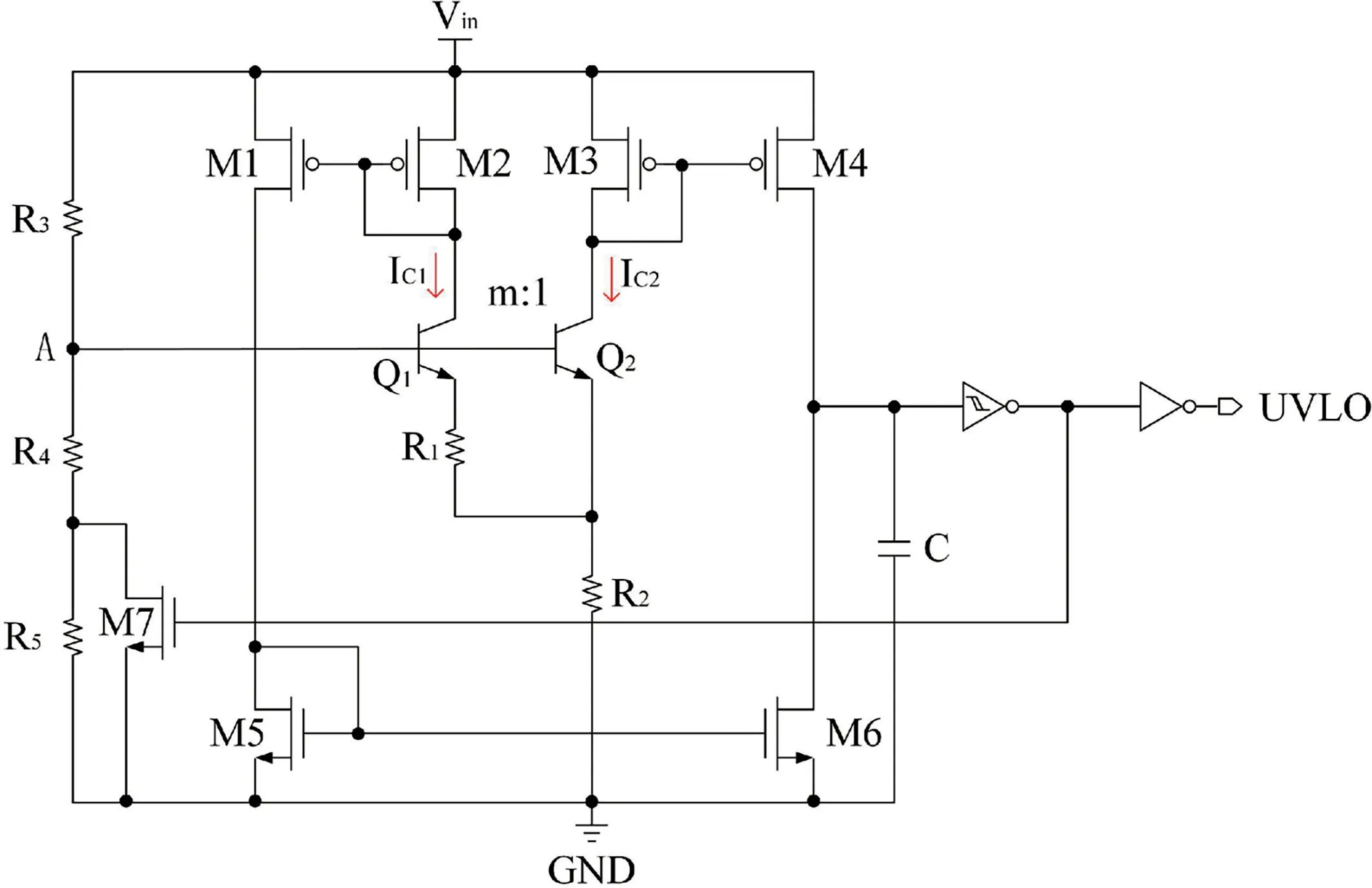

图1 展示了常规的带隙结构UVLO 电路,基准电压由两个双极性晶体管结构产生,它的基极电流由电压采样电路提供[12]。MOS 管M2、M3 为其提供有源负载,M1~M6 构成电流镜;M7、R3~R5为电压采样电路;施密特触发器以及反相器对比较器输出波形进行整形以及缓冲[13]。其中Q1和Q2的发射极面积之比为m∶1,则

图1 带隙结构欠压锁定电路Fig.1 UVLO circuit with band gap structure

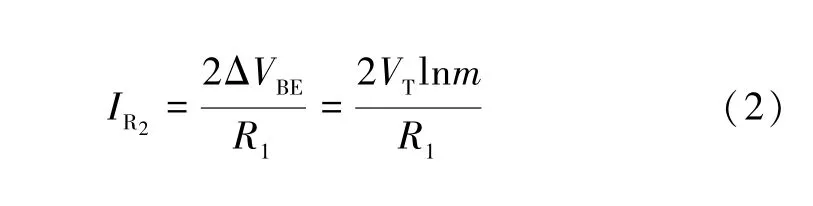

流经R2的电流为:

式中:VTlnm是两个工作在不同电流密度下的双极晶体管的基极-发射极电压的差值。

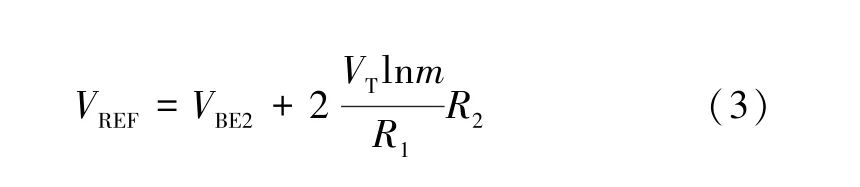

基准电压的表达式为[14]:

式中:VBE2是负温度系数电压;VT=kT/q,为正温度系数电压。二者相加之后,通过调整R1、R2的电阻比例产生一个零温度系数的基准电压[15]。

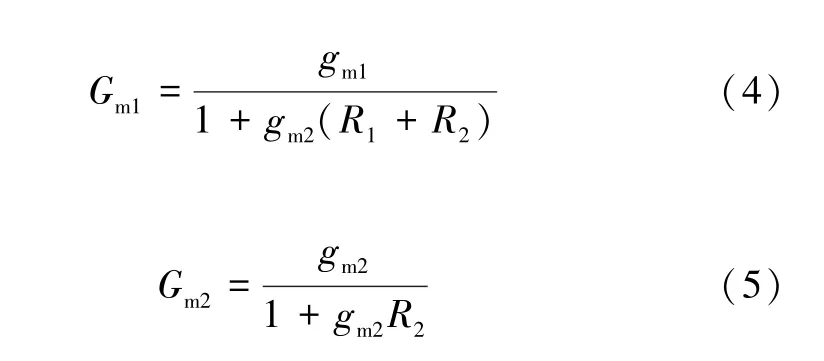

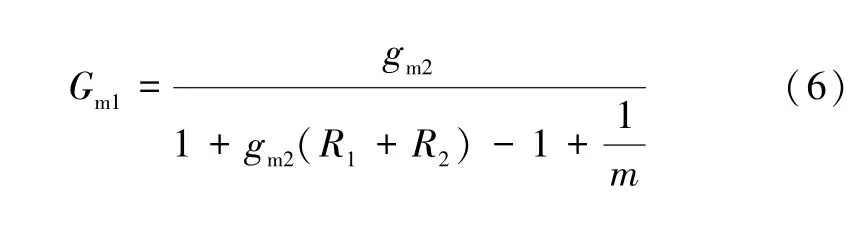

在电阻R1、R2的作用下,Q1和Q2的共射放大器的跨导分别为:

由式(4)和(5)可知:

通常gm2R2>>1,则Gm2>Gm1,因此Q1的集电极电流随采样电压的变化小于Q2的集电极电流的变化。带隙结构UVLO 是利用两个电流的变化快慢进行比较。

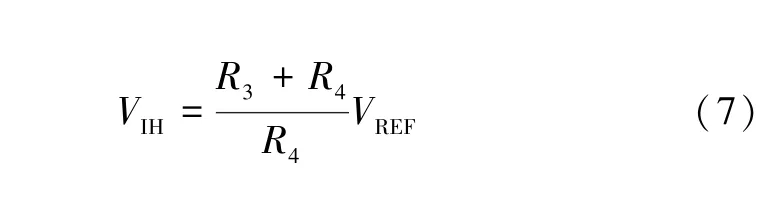

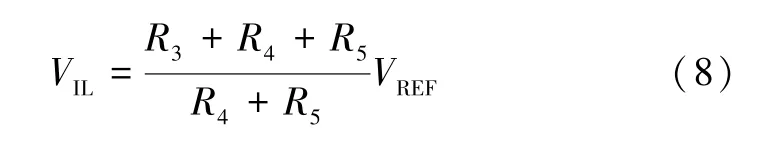

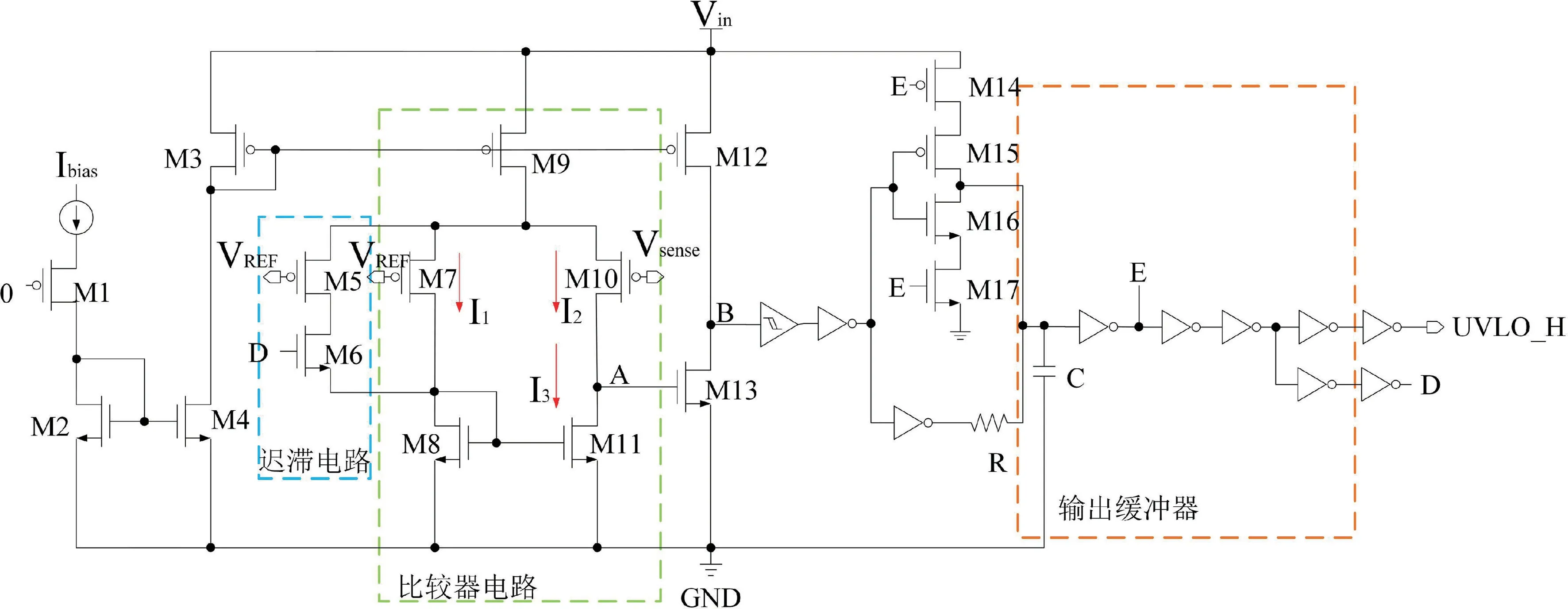

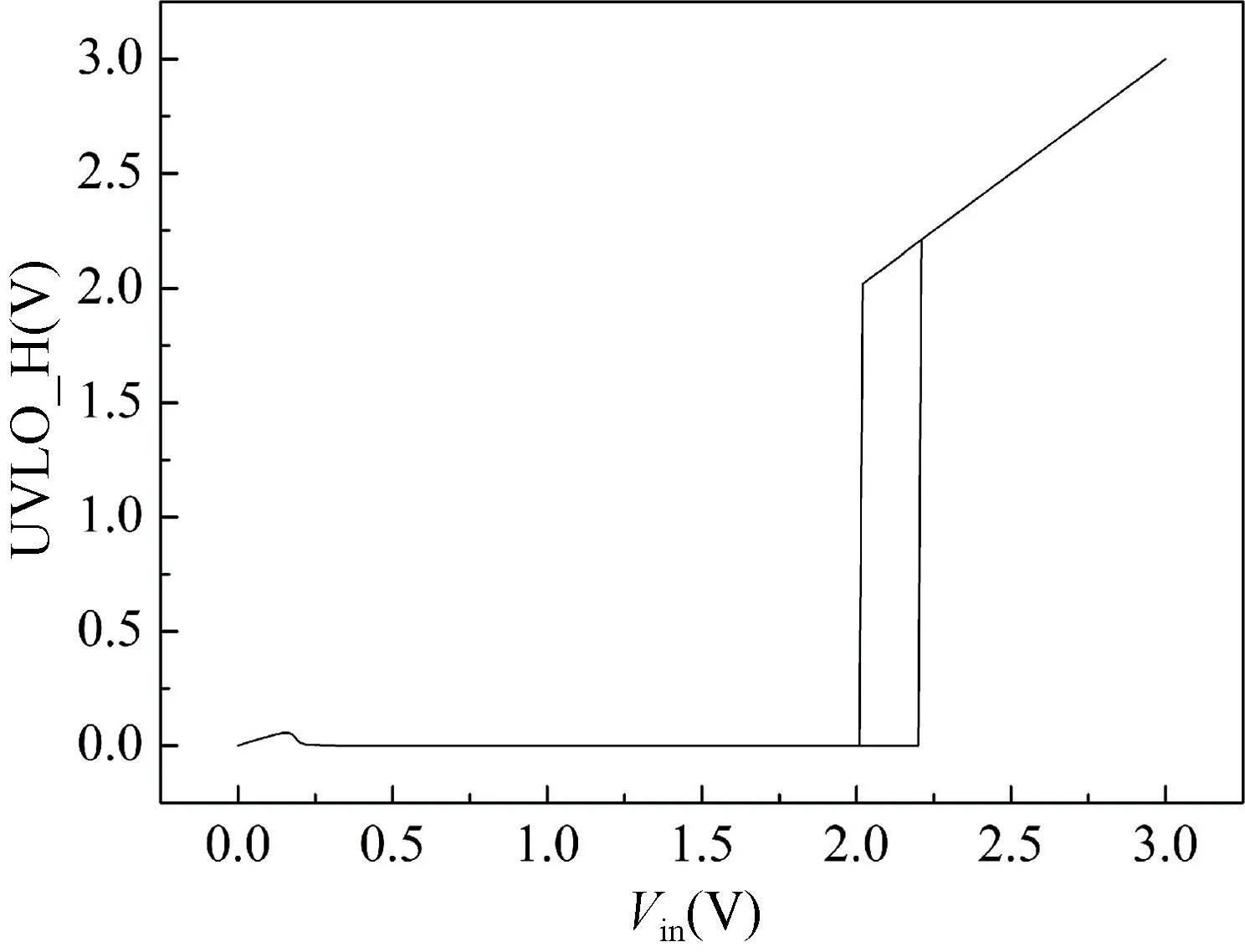

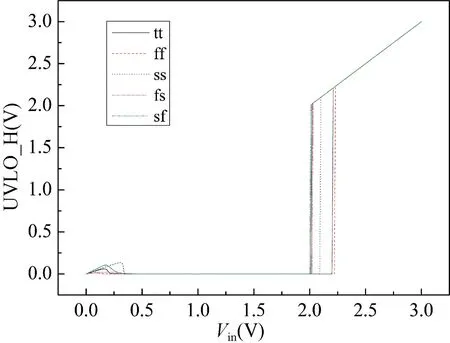

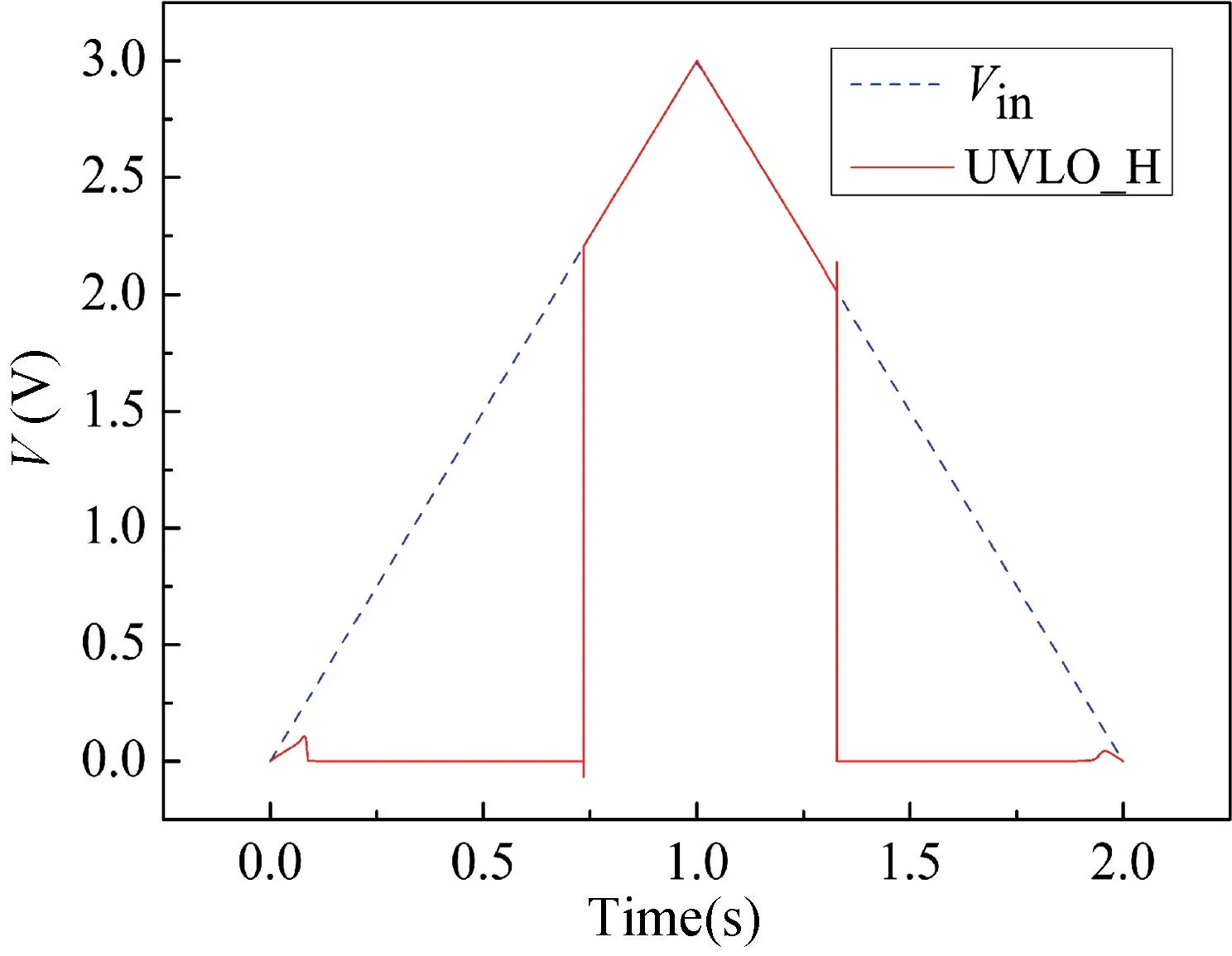

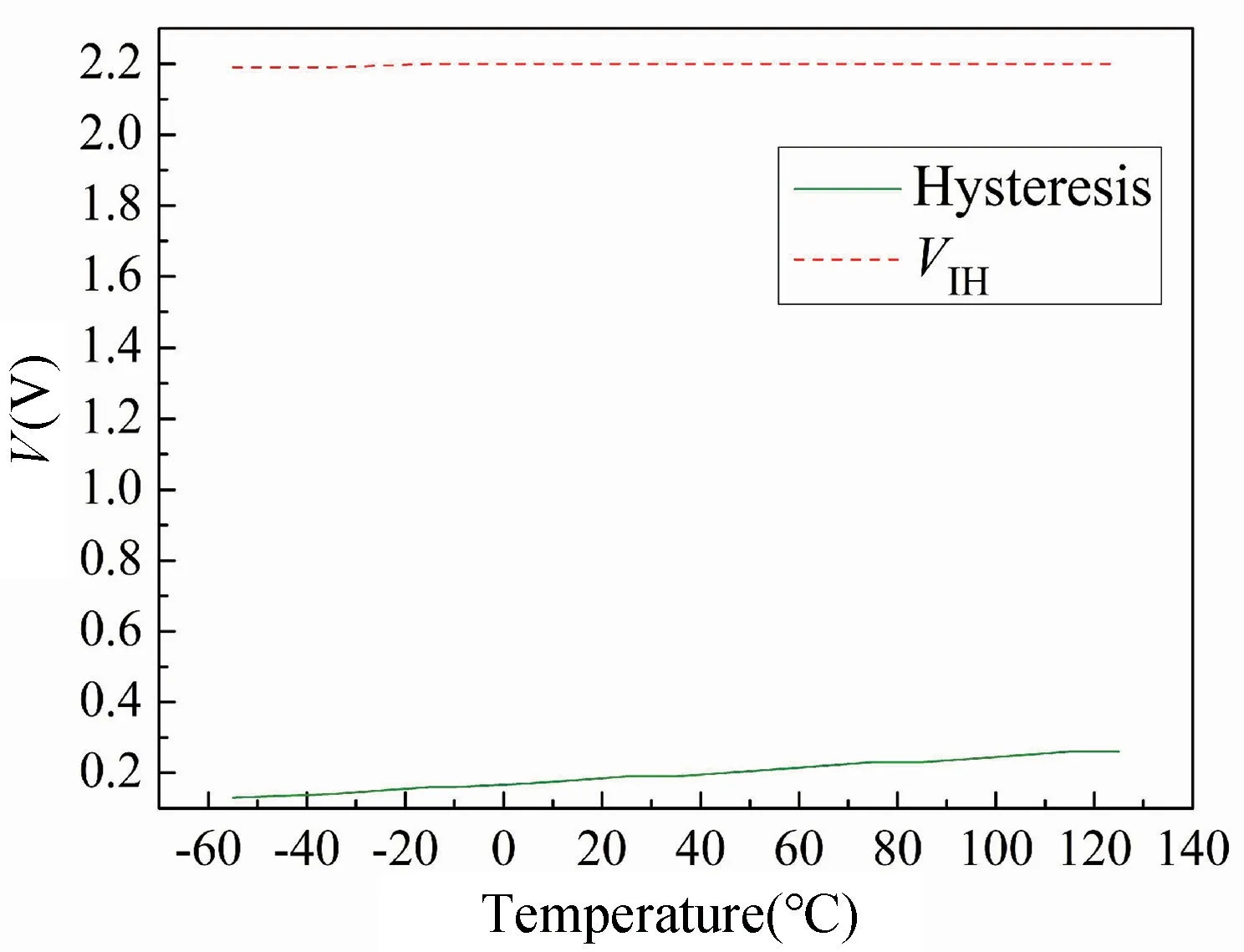

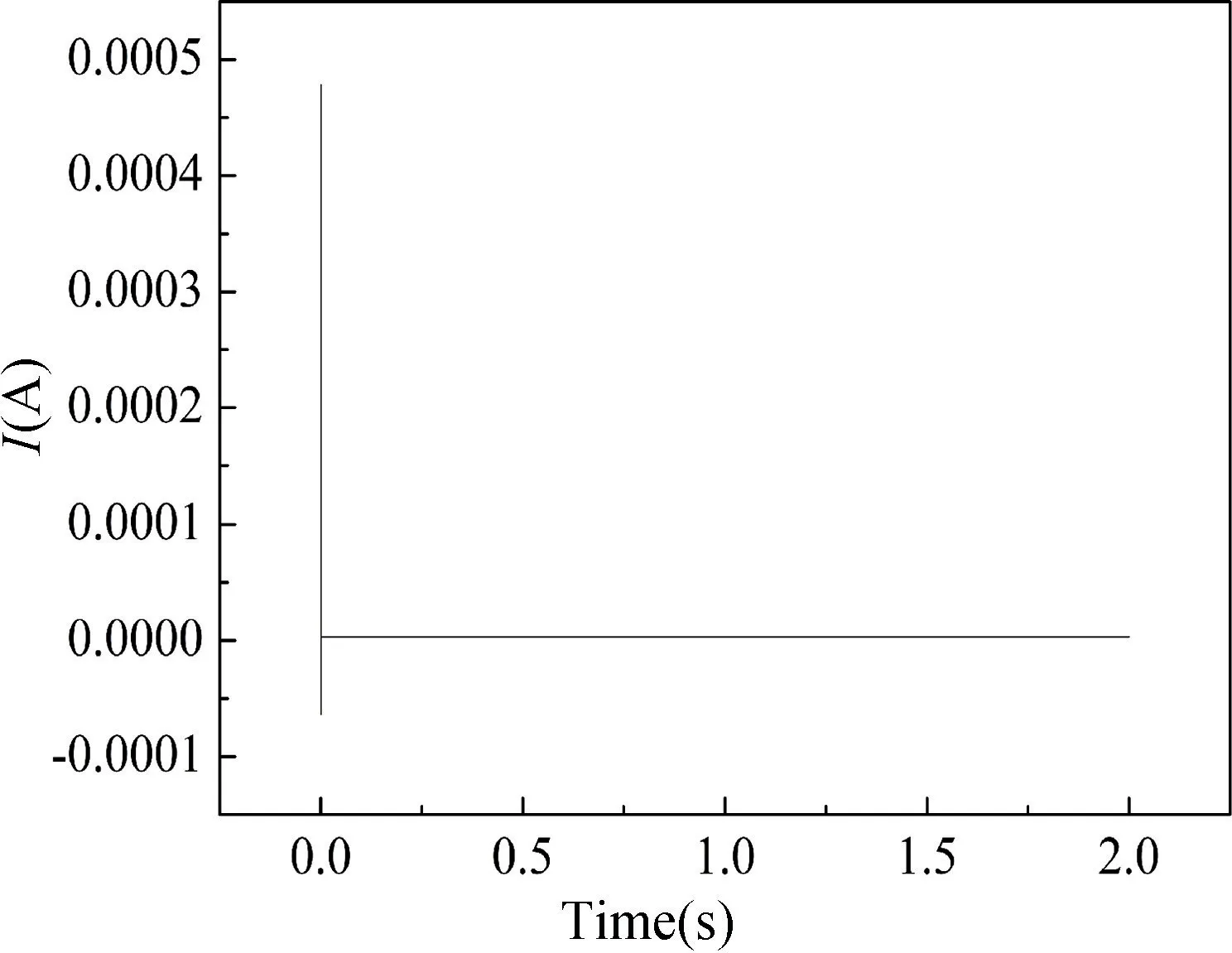

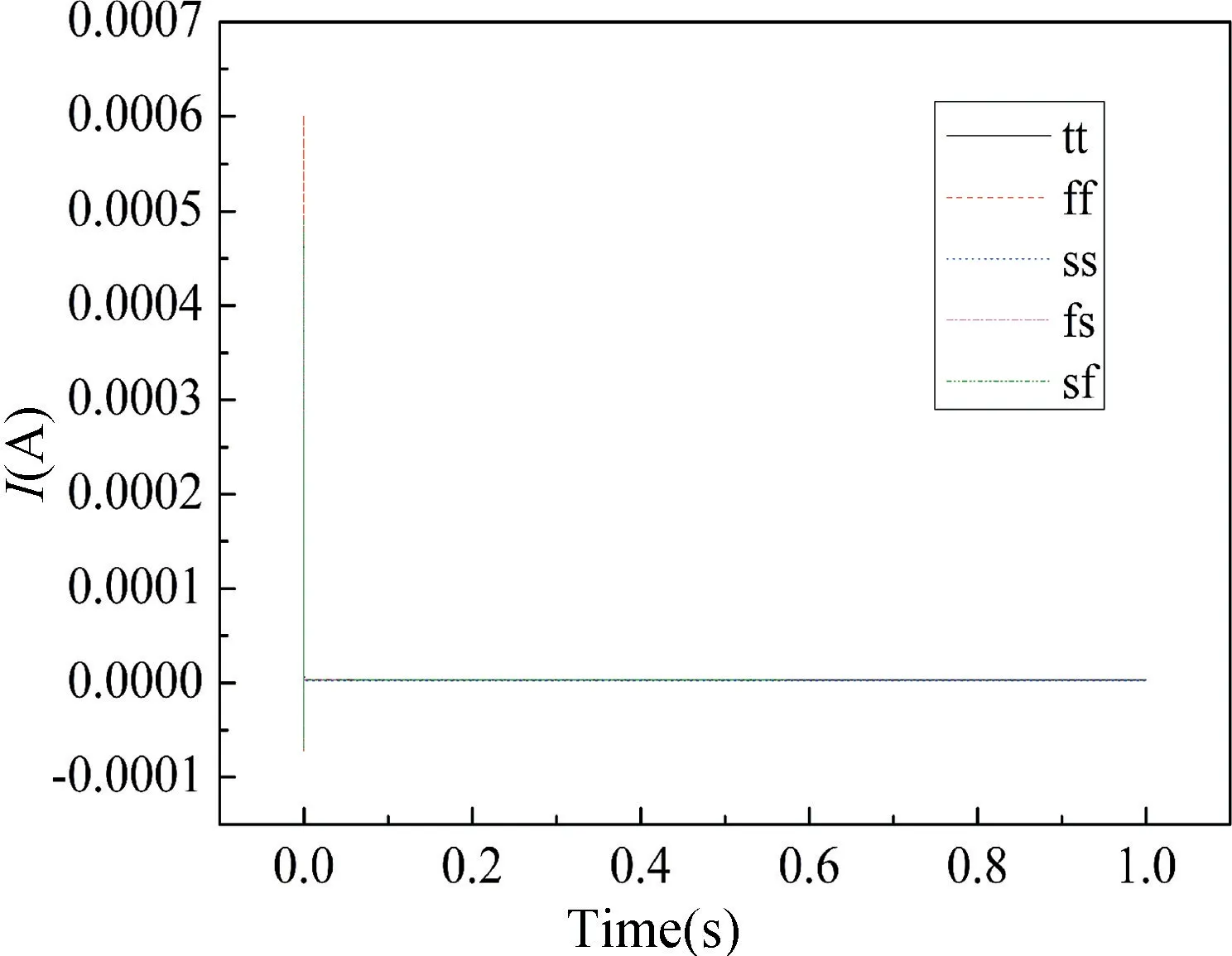

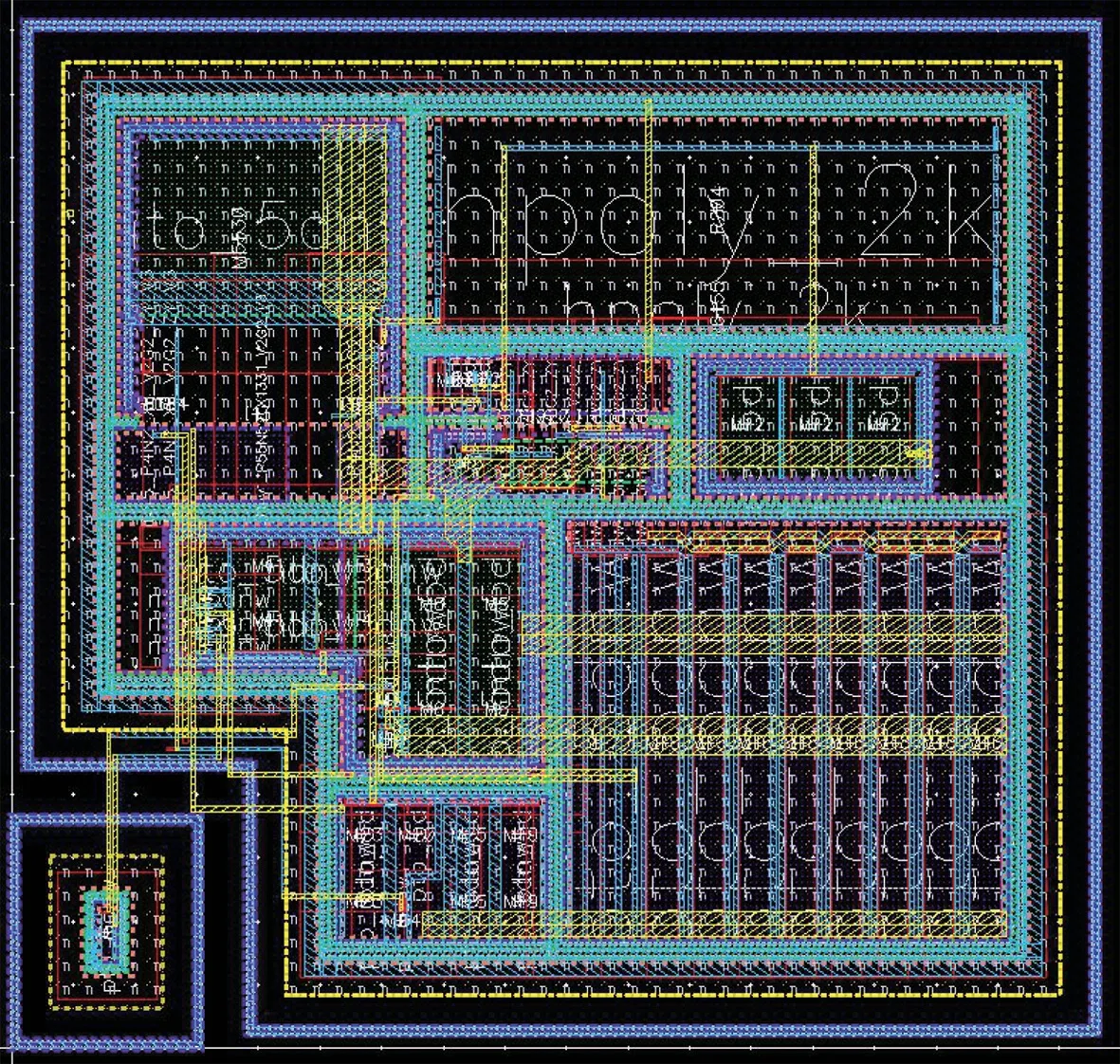

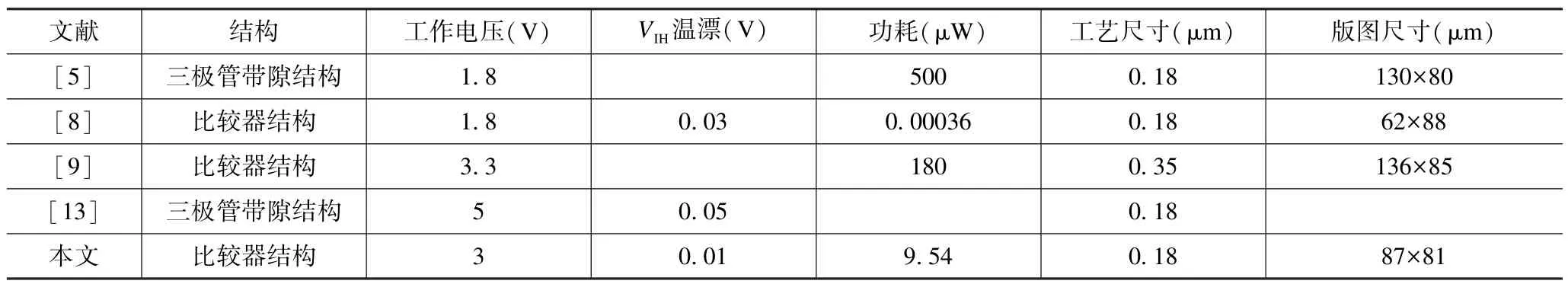

当电源电压Vin 上门限阈值电压为: 下门限阈值电压为: 式中:VREF为基准电压。根据电阻值的不同,可以通过调整上、下门限电压改变滞回电压。 带隙结构UVLO 电路利用IC1和IC2的变化快慢进行比较,通过改变电源电压在上电和掉电过程中电阻的分压比例产生滞回电压。当三极管的放大系数不够大时,门限阈值电压会偏离理想值;在温度及寄生参数的影响下,因比较器的迟滞产生漂移会导致门限阈值电压发生漂移,从而影响对电源电压的监控。 针对带隙结构UVLO 电路的缺点,本文提出了一种利用差分放大器的非对称性产生滞回电压的UVLO电路,如图2 所示。该电路包含了偏置电路、迟滞电路、电压比较器电路、输出缓冲器及防止误翻转电路。 图2 非对称欠压锁定电路Fig.2 Asymmetric UVLO circuit Ibias是由带隙基准模块提供的偏置电流,经过M2与M4、M3 与M9、M3 与M12 三组电流镜结构,为差分放大器及共源级放大器提供尾电流。电压比较器的一个输入端是带隙基准模块提供的与温度无关的基准电压VREF,另一个输入端是对电源电压经电阻分压所得的采样信号Vsense。M7~M13 为两级比较器,M5、M6 为UVLO 输出为高电平时引入的一路非对称电流,通过两边的非对称性产生滞回电压。为提高电压比较精度,使用两级比较器来提高增益,第一级为电压比较器,第二级为共源级放大器。输出缓冲器对输出的波形进行整形以及缓冲,提高电路的驱动能力。迟滞电路避免电源电压在阈值电压附近振荡,提高系统的稳定性。防止误翻转电路通过对电容C 进行充电,减小电源电压的尖峰脉冲对输出的影响。 该电路直接将电源电压的采样电压作为M10 的栅极电压,采用比较电流的方式来判断电源电压是否处在正常工作范围。接通电源时,Vin逐渐升高,电路中I1通过M8 和M11 的电流镜,将I1镜像给I3,由于M8和M11 的管子参数是一致的,根据电流镜同比例镜像关系,得I1=I3,将I3与I2进行比较。因为差分输入对管是P 管,根据饱和区漏电流公式得出,栅端电压高的其电流小,所以得出I3 当电源电压正常即Vsense>VREF时,M7 的电流小于M10 的电流,此时比较器输出端B 点为高电平,经过逻辑变换UVLO_H 输出高电平,控制其他模块正常工作。此时D 点与UVLO_H 电位相同并反馈回到M6,将其导通,电路中新加了流经M5 的支路电流,此时电路中包含两路电流,产生了非对称电流。所以当Vin下降的时候,需要降低到更低的电压才能发生输出跳变,这一点电压称之为下门限阈值电压VIL。通过改变M5 的宽长比可以调整迟滞电压。 当电源电压下降时,Vsense逐渐接近VREF,直到Vsense 当M5、M6 未导通时,M10 上的电流Ia为: 当UVLO_ H 发生翻转,M5、M6 导通后,M10上的电流Ib为: 且2Ia=Ib,可得: 本设计基于0.18 μm BCD 工艺,利用仿真平台对UVLO 电路进行仿真分析。UVLO 电路在tt 工艺角下对电源电压进行直流扫描的仿真结果如图3 所示。电路有良好的滞回电压曲线,滞回电压为0.19 V。 图3 25 ℃滞回电压仿真结果Fig.3 Simulation results of hysteresis voltage at 25 ℃ UVLO 电路在不同工艺角下滞回电压的仿真结果如图4 所示。在各工艺角的极端条件下对其仿真,结果表明滞回电压变化量为0.01 V,仿真结果证明了UVLO 的可行性与可靠性。 图4 不同工艺角下滞回电压仿真结果Fig.4 Simulation results of hysteresis voltage at different process corners 欠压锁定电路的瞬态特性如图5 所示。结果表明:当欠压锁定电路模块电源电压Vin=2.2 V 时,电路关闭,其他电路正常工作;当欠压锁定模块在Vin=2.01 V时,电路打开,其他电路关断;滞回电压为0.19 V。 图5 欠压锁定电路瞬态特性Fig.5 Transient characteristics of the UVLO circuit 滞回电压随着温度的变化如图6 所示。结果表明,在T=25 ℃时,VIH=2.2 V,VIL=2.01 V,滞回电压为0.19 V。当温度在-55~+125 ℃范围内变化时,上门限电压的最大偏移只有0.01 V,滞回电压最大偏移为0.07 V,减小了滞回电压的温漂。本设计消除了带隙结构UVLO 受双极型晶体管参数影响导致随温度偏移过大的情况。 图6 滞回电压温漂特性Fig.6 Temperature characteristic of hysteresis voltage 输入电压在3 V 时输入电流的变化如图7 所示。当输入电压为3 V 时,输出电流为3.18 μA,此时电路的功耗为9.54 μW。输入电压的工作范围为2.5~4.8 V 时,最大功耗为15.84 μW,可以通过改变M4、M11、M16 的宽长比,降低功耗至所需指标。可根据芯片系统的具体要求调节所需要的功耗指标。全工艺角下,在输入电压为3 V 时,室温下输入电流的变化如图8 所示,最大输入电流为4.0 μA,功耗为12 μW。 图7 输入电压在3 V 时输入电流的变化Fig.7 Change of input current when the input voltage is 3 V 图8 不同工艺角下输入电流的变化Fig.8 Change of input current with different process corners 欠压锁定电路的版图布局如图9 所示。占据面积约为87 μm×81 μm,金属M1~M3 用于布线。 图9 欠压锁定电路版图(87 μm×81 μm)Fig.9 Layout of the UVLO circuit(87 μm×81 μm) 该电路在结构、性能参数以及工艺上与同类文献的对比分析情况见表1,分析表明本文提出的欠压锁定电路结构在VIH的稳定性、温漂、功耗等方面都有所改善。本设计与文献[8,13]相比温漂更小;与文献[9]在相同输入电压下相比功耗更小;与文献[5]在相同工艺下相比其版图面积更小,电路结构更简单。 表1 与同类文献结果对比Tab.1 Comparison with similar literature results 本文结合电荷泵IC 的设计要求,设计出具有高集成度和低温漂特性的欠压锁定电路。基于0.18 μm BCD 工艺,电路设计满足要求。本文详细描述了电路原理,并通过仿真验证了电路的功能。该电路结构简单、易于分析,借助差分放大器的非对称性实现迟滞,结果为:上门限阈值电压为2.2 V,下门限阈值电压为2.01 V,滞回电压为0.19 V,在-55~+125 ℃以内,VIH温漂为0.01 V。芯片工作电压范围在2.5~4.8 V,静态电流在电源电压为3 V 时约为3.18 μA,功耗约为9.54 μW。综上所述,该电路可以输出欠压逻辑信号,具有良好的低温漂特性和迟滞功能以及低功耗,已成功应用于一款双通道电荷泵芯片当中。

2 电路设计

3 结果与讨论

4 结论