多通道振动信号采集系统设计

2022-05-31崔永俊

崔永俊,郭 峰

(中北大学仪器与电子学院,仪器科学与动态测试教育部重点实验室,电子测试技术国防科技重点实验室,山西太原 030051)

0 引言

振动信号测试在动态测试系统中具有重要的作用,在飞机航天器系统测试、船舶柴油机运行状态检测、大型机械设备齿轮箱轴承检测、汽车健康监测与评估等领域中均有着广泛的应用需求[1-2]。

目前,在动态测试领域采用的测试系统连线复杂、操作繁琐、排故困难、体积大、质量重、便携性差、采集精度较低。为此,设计了一种多路振动信号采集系统,实现了对微小振动信号的大动态范围、大量程同步采集,对机械设备等振动信号的采集分析有意义[3-5]。

1 系统整体设计

振动信号采集系统的总体设计如图1所示,系统由传感器电源激励模块、信号调理模块、采集传输模块以及上位机组成。系统在工作过程中,4路ICP振动传感器由激励源供电,获取被测物产生的信号,通过信号调理通道对信号进行滤波放大、偏置调节、单端转差分等处理,然后分别通过4片AD7760进行采集,由FPGA接收缓存并处理AD数据,通过以太网接口传输至上位机,由上位机进行波形显示、FFT变换以及数据存储等。上位机同时可以通过以太网传输指令实现对采样接口传输速率、AD的内部抽样率等控制。

图1 系统整体框图

2 系统硬件电路设计

2.1 ICP传感器激励源电路

本文采用ICP(integrated circuits piezoelectric)压电型加速度传感器M350B04。相比于其他传感器,ICP传感器具有信噪比高、输出精度高、信号远距离传输衰减小等优点,也更适合在恶劣环境下工作[6]。

ICP传感器在使用时需要提供稳定电流源供电,信号的输出线也同时是电流输入的供电电缆。本设计传感器工作输入电压在20~30 V,电流为2~20 mA,设计采用恒流源芯片LM134,它具备工作温度范围广的优点,适用测试场合更多,激励电流源电路图如图2所示。

图2 恒流源电路

LM134由24 V供电,根据芯片手册,当R17=10R16时,芯片输出恒流Iset≈0.134 V/R16。且考虑到该芯片输出电流会随温度有细微变化,所以放置二极管1N4148起到抑制温漂的作用。取R18=0 Ω为测试点,经测试,当R16=18 Ω,R17=180 Ω时,输出电流Iset=8 mA,满足传感器供电需求。

2.2 信号调理电路

2.2.1 偏置电压调整

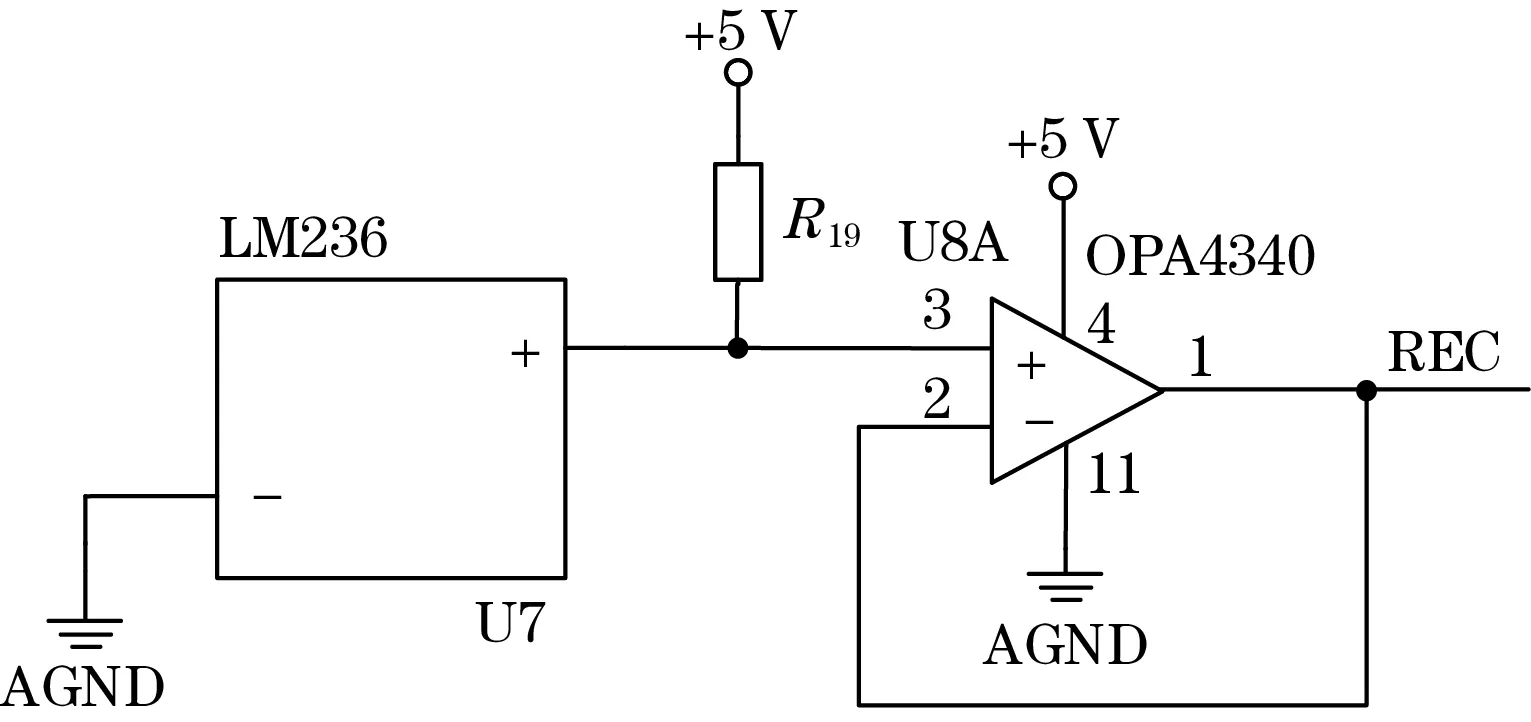

传感器输出电压为8~14 V,为了保证输出在AD的采集范围内,需要将输出电压进行偏置调理。本文采用LM236-5.0芯片提供5 V的基准电压,后经过OPA4340内置的一个运算放大器作为电源跟随实现电路缓冲和降低输出阻抗。电路图如图3所示。

图3 偏置电压提供

OPA4340运算放大芯片内置4个独立的运算放大器。在后续的偏置电压调节中,利用芯片内部放大器级联,搭成减法运算电路,将传感器信号做2次减法运算,使输出信号向下偏置10 V,经测试,当传感器处于无振动环境时,此时输出信号为0.211 V,符合ADC采集需求。

2.2.2 抗混叠低通滤波

为了防止由于采样率不足造成的系统中不同信号发生混合,本设计采用开关电容式抗混叠滤波芯片MAX291设计了抗混叠低通滤波电路[7]。MAX291需要提供时钟来驱动电路,有外接时钟或者使用内部时钟2种方式。使用内部时钟操作简单,只需在CLK引脚外接合适的电容,电容值要满足与截止频率的对应关系:

(1)

式中:Cosc为时钟引脚的外接电容,pF;fosc为截止频率的100倍,kHz。

一般机械的最大振动频率在8 kHz左右,此时设置-3 dB截止频率为10 kHz,带入式(1),计算得到此时Cosc=33 pF,抗混叠滤波电路如图4所示。

图4 抗混叠滤波电路

2.2.3 单端转差分电路

为了使ADC发挥最佳的性能,本次设计采用差分信号来驱动ADC,需要将调理信号做单端转差分处理。AD8138是低失真差分ADC驱动器,本次设计采用AD8138来实现信号单端转差分,电路图如图5所示。

图5 单端转差分电路

AD8138通过控制两路反馈电路来输出差分输出电压和共模输出电压,其中VCOM引脚可以用于调节输出电压偏置,通过调节R38、R39、R41及R42来调节正负输出增益,本次设计中输出增益为1。2.3 AD7760外围配置电路

AD7760是24位模数转换芯片,最高采样率为2.5 MSa/s,动态范围大于100 dB。常被用于高精度的微弱信号采集、振动分析等领域中[8]。AD7760外围配置电路如图6所示。

图6 AD7760外围电路

AD7760可以采用差分输入的方式采集信号,由外部提供40 MHz的采样时钟。ADC采集的电压范围与Vref脚的恒定电压有关,设计中采用ADR434串联基准电压芯片来为Vref脚提供4.096 V的基准电压,此时AD采集电压输入范围为±3.275V,是基于Vref/2即2.048 V共模电压的差分偏置电压。还需要提供额外的2.5 V和5 V电压用于ADC的调制器电源、差分放大器电源以及基准缓冲器电源等。

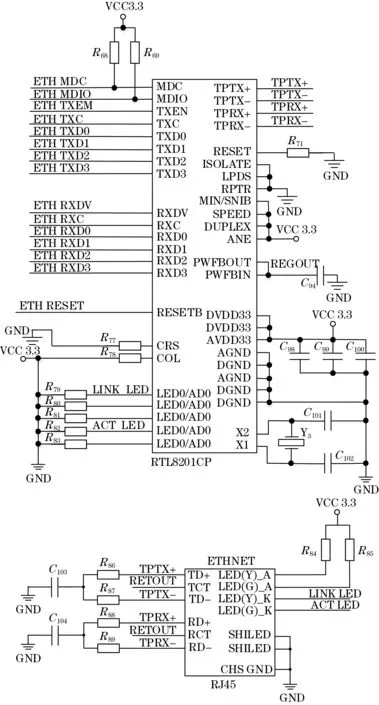

2.4 以太网接口电路

为了提高系统传输速率,也方便支持对后续采样系统的功能扩展,本设计采用以太网PHY(物理层)芯片RTL8201CP,该芯片包含MII和SNI 2种网络接口,本设计采用MII接口,可实现100 Mb/s的数据收发,满足本系统数据传输需求。以太网的物理接口常用的包括RJ45、RJ11和光纤维口等,RJ45常被用于网络接口,适用于PC端的通信。RTL8201CP以及RJ45接口的外围电路如图7所示,其中RTL8201CP需要外接1个25 MHz的晶振提供稳定的时钟源[9]。

图7 以太网芯片接口外围电路

3 系统软件设计

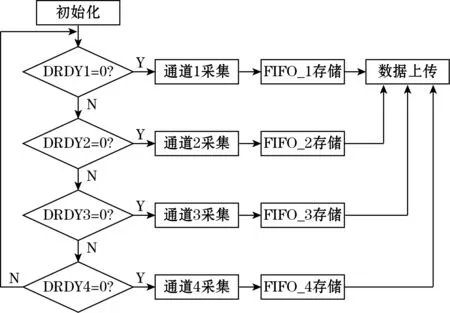

3.1 多路AD采集逻辑设计

图8 4路AD采集控制状态图

3.2 以太网接口逻辑设计

数据通过以太网的传输过程中,需要严格按照以太网包对数据进行打包处理。MAC层的以太包组成格式为:前导码+SFD+以太网帧头+IP首部+UDP首部+用户数据+FCS。其中用户数据占据18~1 472 Byte,前导码和SFD一般为固定字节,帧头包括源MAC地址和目的MAC地址,即主机从机的地址,可以通过查询得到,帧检测序列FCS用于以太网发送数据时的校验。IP首部为20 Byte,包括版本、服务类型、长度等,这里也是固定字节。理论上IP后可以直接添加用户数据,即作为TCP协议传输,在实际中由于UDP协议具有传输速度快、占用资源少等优点,更适合于硬件电路的传输应用,所以在IP首部后添加8 Byte的UDP首部,相当于IP层数据段包括了UDP首部和需要传输的数据。

太网接口芯片作为物理层可以看作是MAC层和上位机传输的媒介,为了方便调用,本设计将以太网的接收数据、发送数据以及发送数据时的校验模块作为UDP模块来打包处理。打包结构如图9所示。

图9 UDP打包模块

在发送数据时,整个以太包的发送顺序与之前所述MAC层以太包格式顺序一致。发送数据时需要有IP首部的校验,还有最终传输数据的CRC校验,CRC校验后结果为4 Byte FSC字段附在发送以太网帧格式的末尾。其中MII接口为4位有效数字,而输出帧格式保持与IP数据报格式一致,为32位数字。所以在数据发送过程中实际上实现了32位数据和4位数据的转化。数据的接收过程和发送过程大致相反,在接收过程中省去了IP首部校验和CRC校验[10]。

以太网包传输的数据每包不超过1 472 Byte,本设计中FPGA内部设置4个128×32 bit的FIFO,分别对应采集的4个通道[11]。在考虑FPGA状态机转换时,需要有设置FPGA内部FIFO并判断其空满状态。这里设FIFO_HFULL=1为存半满状态,FIFO_EMP=1为空状态,EN为使能信号。同时采集时,以通道1为例,当FIFO1_HFULL=1时,使能信号EN1拉高,数据开始打包发送,同时向FIFO1内部写入2 Byte特定字节作为下次传输帧头,用于上位机区分不同通道,传输结束后使能信号EN1拉低,等待下次半满状态再次传输。端口扫描信号scan快速循环扫描4通道的状态,当检测到某一通道FIFO为半满状态时,该通道开始传输,其余通道保持FIFO写状态。由于以太网传输速率远大于通道采集速率,所以不必考虑FIFO溢出的问题。FPGA读信号过程与写信号类似,方向相反。

3.3 上位机软件设计

LabVIEW通过拖动控件快速搭建虚拟仪器,被广泛的应用于信号的采集处理中[12]。本设计使用LabVIEW搭建上位机界面,包含采样设置、采样显示、参数输出和系统管理。采样设置可以选择AD的采样频率、采样点数和抽样率;采样显示可以显示信号的实时波形、FFT和直方图,并且可以对曲线进行放大和拖拽;参数输出包括当前最大最小值的输出电压、波形频率、动态范围以及SNR信噪比;系统管理可以保存波形图像和数据。

4 系统测试及验证

4.1 采样精度测试

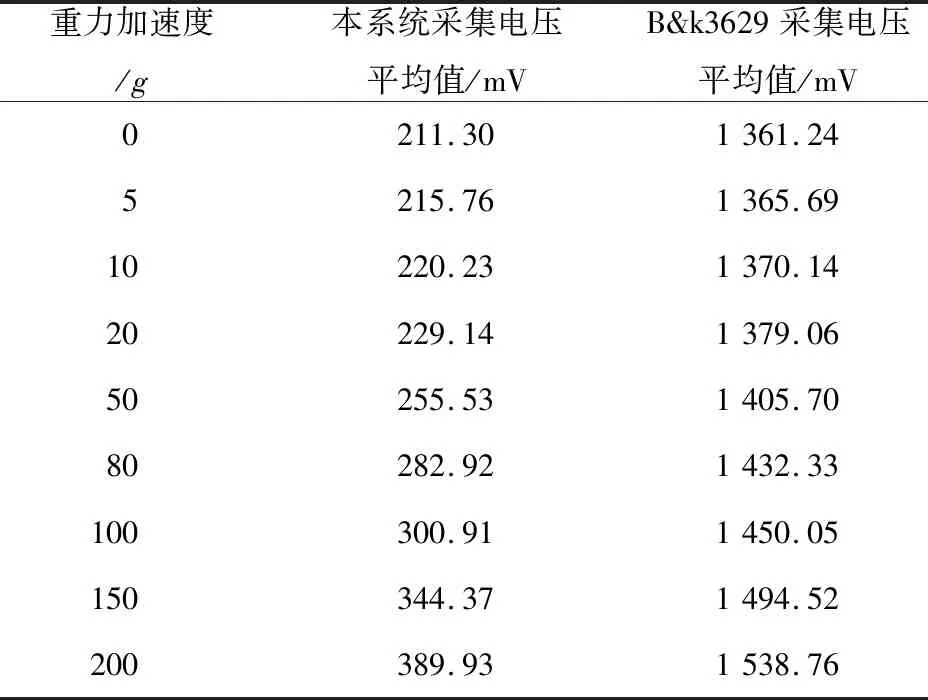

为了检测系统采样的准确度,本次测试使用R0500SL作为振动平台,受测试台振动范围限制,实验在0~200g重力加速度范围内采样多个测试点,重复3次实验,每个测量点取3次测试的平均值。并与B&k3629振动传感器校准系统的测试结果进行对比,如表1所示。

表1 本系统与B&k3629振动系统测量结果对比

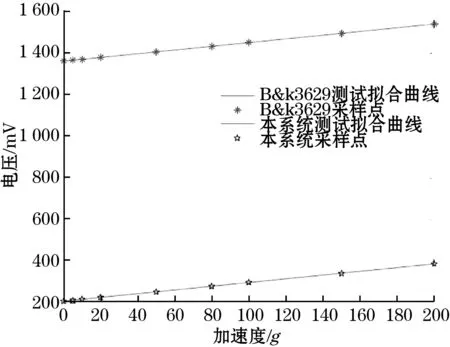

由于ICP传感器输出幅值和加速度成正比,将实验数据使用Matlab进行最小二乘法数据拟合,可得到拟合曲线如图10所示。

图10 测试结果拟合曲线

此时,本系统和B&k3629的拟合结果为一次函数,分别为:

y=0.887 8x+1 361.3

(2)

y=0.891 8x+211.29

(3)

其中式(2)为B&k3629系统的拟合结果,式(3)为本系统拟合结果。由于两系统内部调理电路偏置电压设置不同,导致拟合结果常数量不同。由式(2)、式(3)的一阶系数可以得到,本系统与B&k3629系统误差约为0.49%。加速度传感器M350B04的带内分辨率为0.02g,测量结果在传感器的误差范围内。

4.2 通道动态范围测试

系统动态范围表示为器件满量程采集的均方根与输入短路时均方根噪声之比,也可以用来表示系统可采集最大值和最小值的关系,单位为dB。动态范围越大,表示信号的可采集精度越高,动态范围通常计算公式为

(4)

式中:ARMSmax为可采集最大信号幅值,本系统中ADC的最大采集信号幅值为3.275 V;ARMSmin为可采集的最小信号幅值。

在本次测试中,将输入信号短接并接地,此时ADC读取到的数据即为信号可采集到的最小输入噪声。分别测试4个通道的动态范围,其中通道1和通道2设置采样率为78.1 kSa/s和156.3 kSa/s。通道3和通道4设置采样率为312.5 kSa/s和625 kSa/s。采集10次噪声信号并取平均值,测试结果如表2所示。

表2 动态范围测试结果

由表2可以得出4路ADC采集的动态范围都能达到95 dB以上,满足设计需求。动态范围受采样率影响,ADC采样率越高,动态范围越低。

4.3 上位机结果显示

测试中使用4个通道同时采样,通道1和通道2采集2种不同的振动信号,通道3显示直方图像,通道4显示FFT图。测试界面如图11所示。经测试上位机使用正常,达到了预期设计。

图11 上位机显示界面

5 结束语

针对目前部分振动信号采样系统在采集过程中存在的精度差、通道少等问题,设计了一种基于FPGA的高精度振动信号采集系统。通过采集处理传输等硬件电路,在上位机上显示采集结果,并与国外设备进行对比,验证了设计的正确性,对保证更加精确的采集振动信号提供参考。