基于FPGA的视频监测存储系统设计

2022-05-31刘荷花蔡江辉王晓燕刘三满

刘荷花,蔡江辉,王晓燕,刘三满

(1.太原学院计算机科学与技术系,山西太原 030032;2.太原科技大学计算机科学与技术学院,山西太原 030024;3.山西警察学院网络安全保卫系,山西太原 030032)

0 引言

在工业领域中,数据采编存储装置是关键性设备之一。随着测试数据需求量不断增大,数据流速度越来越快,在高速度、高精度、高实时性、高可靠性的要求下,对数据采编存储系统提出了新挑战[1]。以往视频记录装置设计是集成采集与存储功能于一体,体积过大,便携性不足,并且系统可靠性会因提高系统复杂性而降低,对于飞行器上需回收的存储器来说不满足使用条件,并且在采集与记录进行数据传输时,并行数据传送速度低且传送过程存在干扰等困难[2],因此,本文设计了基于FPGA的视频监测存储系统。

高速数据采集技术在车载记录仪、航空航天等领域得到广泛的应用[3]。本系统主要在高速、高过载环境下,对视频数据进行采集与存储,使视频数据完整保存。采取多种方式获得视频数据,并对回收视频数据进行分析。

1 总体设计

本文根据设计需求对数据高速采集、高速存储、高速串口传输等技术提出了新思路,介绍了各系统模块关键技术,并对装置性能进行测试。主要由采编器与存储器构成视频监测存储系统,采编器与外部输入设备进行视频数据、时钟频率、命令控制等传送,与地面设备进行命令操纵、视频下载等传送,与存储器进行视频输入输出。利用外部的4路输入信号(S1、S2、S3、S4)决定I、Q模拟视频信号进行A/D转换[4],转换后的数字量经FPGA接收并编码重组,利用高速LVDS接口,采编器与存储器进行数据、命令的传递,利用千兆以太网接口,采编器与地面设备进行视频流传导,采用RS422接口进行命令流的传输,其中命令流主要是控制数据记录装置中的Flash的操作(擦除、页编程、读取),系统总体设计如图1所示。

图1 系统总体设计

2 硬件方案设计

本文主要研究高速采集、高速传输、高速存储技术,重点介绍A/D采集技术、LVDS传输接口、千兆以太网接口、Flash储存、实时监测硬件部分设计。

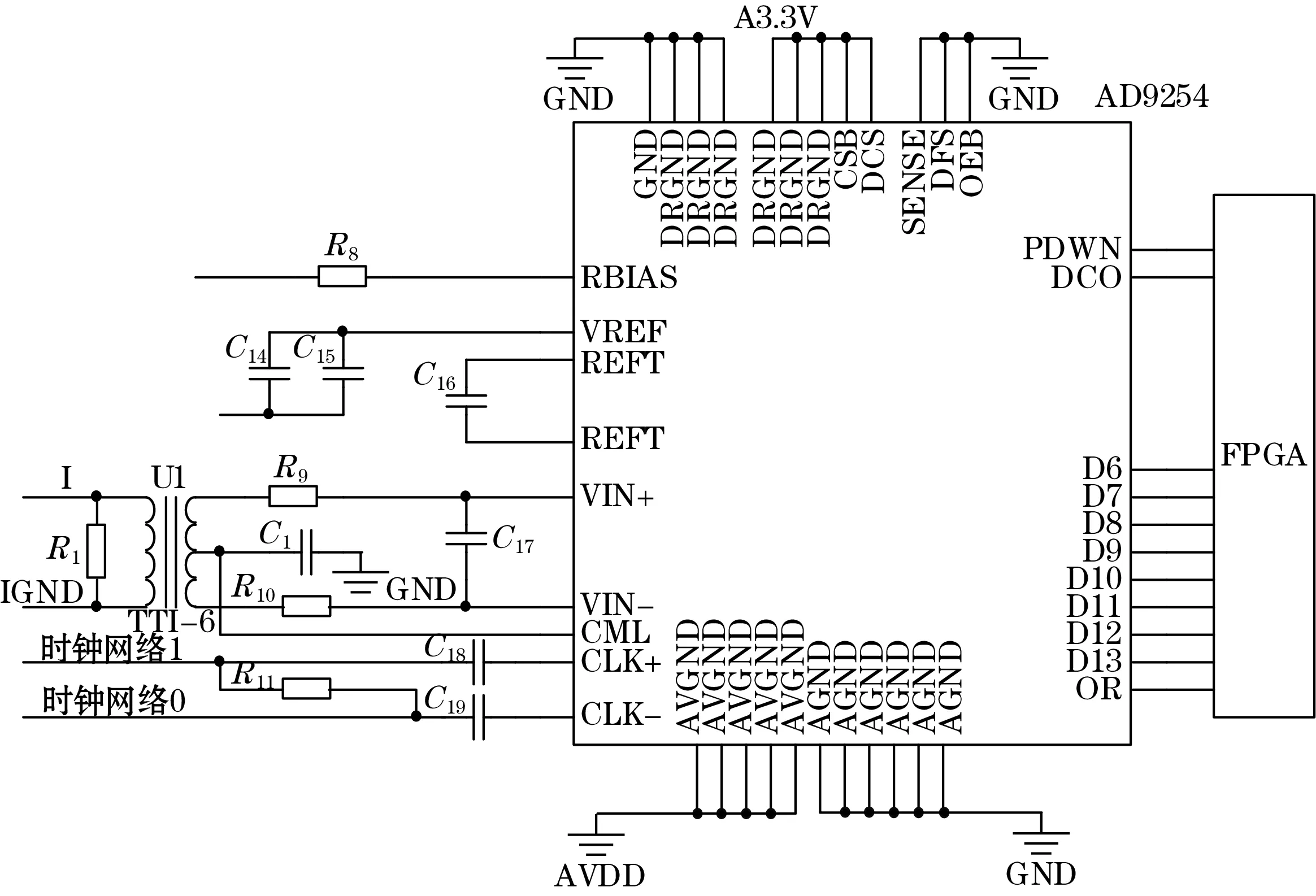

2.1 高速A/D采集电路设计

为了保证系统高可靠性与高速率,高速模数转换器选用AD9254芯片,AD9254芯片功耗低,仅为430 mW,需要为FPGA配备66 MHz的晶振,使用锁相环2倍频为132 MHz[5],为整个FPGA提供全局时钟,需要采集的I、Q视频信号峰值频率为40 MHz,I、Q视频信号重复的频率为15 kHz,据此折算出周期为66 μs[6]。根据系统的设计指标,在1个周期内,前1/2周期采集驱动,后1/2周期采集截止,1个周期内视频实际的采集量为132 MHz×30 μs×10 bit=39 600 bit;推算出有效的采集速度为75 MB/s。视频输入接口电路如图2所示。

图2 视频信号输入接口电路图

2.2 高速数据时钟信号输入接口电路设计

为防止高频信号产生干扰,输入变压器选用射频变压器T1-6T-KK81,对132 MHz高频时钟信号起到隔离作用,实用频率范畴为0.015~300 MHz[7],产生0.25 W输入功耗,对于高速前端器件来说较理想,时钟输入接口电路如图3所示。

图3 时钟输入接口电路图

2.3 高速A/D采集时序关系

在S1~S4采集的时序协作下实行视频的接收、分组和编码操作。在设计帧结构时,编码时序到数据中,与采编的数据一起记录到Flash中。在进行数据采集时,有3段时序需编入帧结构[8]:

(1)1个周期内,当拉高S1信号,在每个S1的posedge对比于S3的posedge记录Absolute时间,设置1 μs为精确度,即在每个1 μs时钟计时器加1;

(2)1个周期内,在每个S4的negedge对比于S3的posedge记录Relative时间,设置1/132 M为精确度,在每个132 MHz时钟计时器加1;

(1)前端AD采集视频数据、MAC头部、IP头部、UDP头部按照以太网帧格式依次添加并打包,形成完整有效以太网帧格式,利用GMII总线传递至物理层芯片,最后在上位机显示。其中先导码包括7个0x55、1个D5Byte,视为IP开始传输数据包标志;在本系统中,电脑端相连接的是网络接口,电脑端的MAC地址作为目标MAC地址;原MAC地址对应于系统本地的MAC地址;0x0800为IP包类型值。

由于体育旅游专业的复合属性,现有基础师资构成主要是以体育专业出身和旅游专业出身的师资为主。体育院校类和综合高校的体育院系开设体育旅游方向的专业,师资力量的构成主要是体育学教师,旅游院系则主要是旅游管理类教师,缺乏复合型的师资体系和教学队伍。进一步完善教学师资力量结构体系是体育旅游专业人才培养首先需要解决的问题。应加强体育旅游专业人才师资队伍的建设,建立专门的培养机构或者在相关高等院校开设长短期的进修班,培养复合应用型的师资队伍。

翻转课堂式教学视频有很强的针对性,其教学内容针对一个特定事物、话题来进行讨论。视频播放时间也是在学生注意力较为有效的时间内控制,把握学生注意力集中的时间,符合人类身心发展特点,更提高了学生视频学习的效率。给学生学习讨论的主动性,有探寻问题、思考问题的空间,激发学生解惑的积极性,激发其自身的潜力,运用多方面学习来解决自己遇到的疑难问题,培养了学生分析能力和解决问题的能力,效果显著。如在设计《裸子植物和被子植物》这一节的学案时,提出:松的球果是不是果实?银杏的种子叫什么?银杏有没有果实?目的是让学生在答疑解惑中得到成长,真正学到知识。

“研发这块我们还是挺给力的!”余保宁介绍,2018年,燕塘乳业设立了博士后科研工作站,成功通过国家优质乳工程验收。“全国仅有光明、三元、燕塘等十几家乳企通过了优质乳工程认证。这应该是目前全国最领先的一个标准,标志着我们国家真正从有奶喝到喝好奶!”

图4 视频数据采集的时序逻辑关系图

2.4 帧结构设计

(2)在视频数据接收过程时,接收模块利用FIFO把前端AD采集的视频进行缓存,同时对CRC校验码和IP校验和进行推算。

表1 帧结构各字节定义

2.5 高速LVDS传输硬件设计

本设计为实现千兆以太网通信功能选用RTL8211EG芯片,RTL8211EG兼容10、100、1 000 MB/s的传输速率,支持GMII/MII、RGMII、SGMII等物理接口,本系统为实现千兆以太网通信功能采用GMII接口,需要配置125 MHz为系统收发时钟,即发送数据的速度125 MB/s,1 000 Mbit/s也就是说传输数据在时钟的上升沿进行采样的速度[13],采用超5类屏蔽双绞线作为数据传输线进行8位数据传输,采用MDI[0]~MDI[3]作为4对介质无关接口,千兆以太网接口硬件部分如图8所示。

图5 LVDS发送端电路

举办了“实行最严格水资源管理制度高层论坛”、祭水大典等活动;省湖泊局、《湖北日报》推出大型系列报道“千湖新记”栏目;省水利厅、团省委、省志愿者协会开展“爱我千湖”志愿者活动,举办“爱我千湖”征文和“湖北最美湖泊”摄影作品征集等活动;全省共举办党政领导等水情教育培训70多期,参训人员8 000多人次。恩施州组建了水情教育宣讲团,编写了水情教育读本,中国水利报以整版篇幅向全国推介,为湖北省实行最严格水资源管理制度营造了良好氛围。

图6 LVDS接收端电路

2.6 存储板电路设计

为提高系统稳定性,需单独设计存储板,板上只放置单块Flash芯片和相应的配置电路,Flash选用K9WAG08U1M芯片,利用高温导线主控板与Flash芯片进行电气连接[12]。“片选信号”为CE,“完成/忙碌信号”为RB,FPGA只需控制这2个信号即可对Flash进行支配,其他接口备用即可。其中FPGA与各存储单元的接口为P1/P2,备用读数接口为P4,主要是便于测试完毕后回读数据,供分析使用。本次设计存储器采取100 MHz系统时钟,理论上每片Flash写入最高速度为50 MB/s,存储板电路设计图如图7所示。

文人直冒酸味,名士酒气熏天;文人如河边的垂柳,名士如利剑出鞘;文人是追梦者,名士是逐风的人。李白是文人中的名士,他曾立志报效国家,仗剑走天下,得意时酒是胆,可以藐视权贵;失意时,酒中透着忧伤。李白每次醉的不同,这是他的宿命。

图7 存储板电路设计图

2.7 千兆以太网接口电路设计

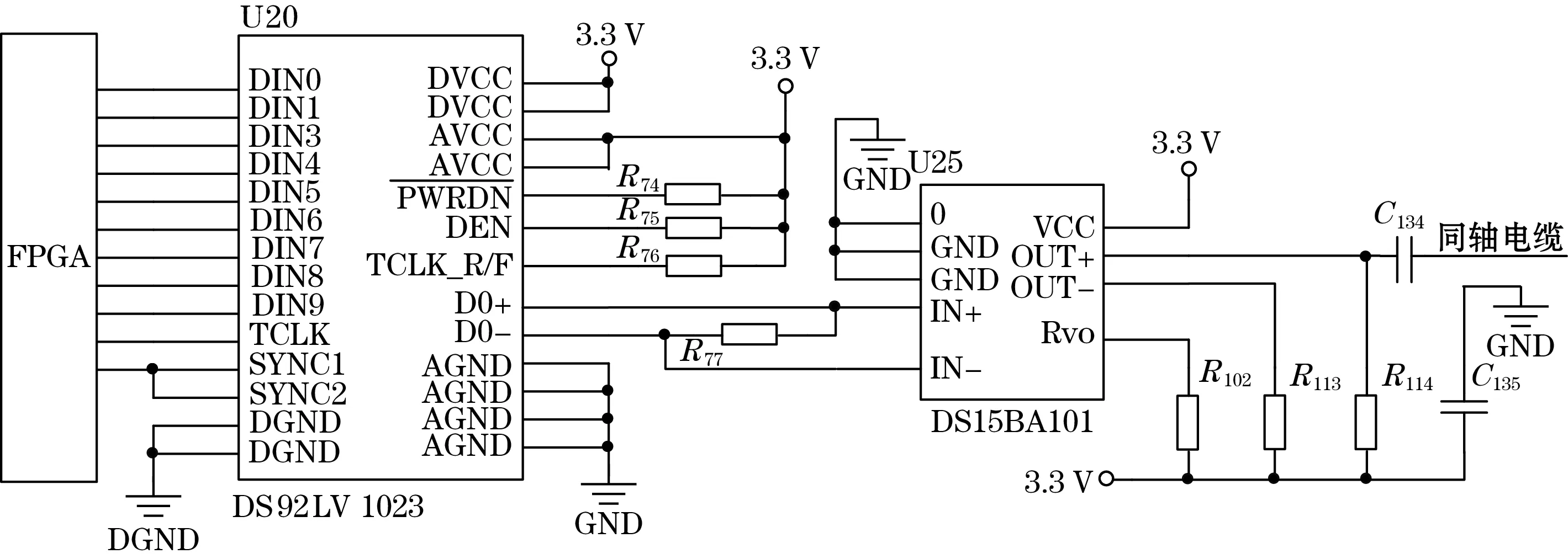

DS92LV1023串行器和DS15BA101总线驱动器构成采编设备的发送端,时钟信号TCLK、10位并行数据DIN0~DIN9经FPGA控制实行并串更换[10]。为确保串行输出处于有效状态,能够有效控制串化芯片,需要将3.3 V电源与串化器的PWRDN、DEN管脚相连,设为逻辑高电平,另用FPGA的I/O端口与SYNC1、SYNC2相连,设为逻辑低电平。为保证芯片为上升沿敏感模式,需配置高电平,将TCLK_R/F引脚连接电源+3.3 V,LVDS发送端电路如图5所示。

2.8 实时监测电路设计

为防止在异常情况下视频数据记录器连续工作对内部设备造成损坏,设计实时监测电路部分,采用AM26LV31EIDR、AM26LV32IDR作为RS422接口芯片[14],具有功耗低、成本低、支持全双工通信的优点,数据通信的峰值为10 MB/s,图9为AM26LV31EIDR、AM26LV32IDR电路设计图。

图9 AM26LV31EIDR、AM26LV32IDR电路设计图

3 FPGA实现监测数据接收逻辑的设计

为满足千兆网监测回收视频逻辑设计要求,FPGA监测系统MAC启动程序由千兆以太网数据帧的发送模块、帧接收模块、CRC校验模块组成。还需研究UDP传送可靠性、储存模块读取带宽等参数,配置4 KByte为UDP数据包的容量。图10为千兆以太网的数据帧接收流程图,接收模块主要实现2个功能:

图10 FPGA实现监测数据接收逻辑的设计

(3)1个周期内,在每个S4的negedge对比于S3的posedge记录Relative时间,设置1/132 M为精确度,在每个132 MHz时钟计时器加1。

根据任务书指标,每次实验保存视频储量为6 GB,需要时间为300 s,若以精确度为1 μs计算,则s3_count配置40位计时器;设置10 μs为S3的脉宽,若以精确度为1/132 M计算[9],则s4_fall_count配置16位计时器;设置33 μs为S4的脉宽,若以精确度为1/132 M计算,则s4_fall_count配置16位计时器,表1为帧结构各字节定义。

DS92LV1224解串器和DS15EA101总线均衡器构成存储器接收端,串行数据经过DS92LV1224解串器转发并转换成时钟信号RCLK、10位并行数据ROUT0~ROUT9,转换后的数据经过FPGA处理后在存储器上保存[11],为保证串并转换始终位于有效状况,需要用解串器的PWRDN、DEN管脚与电源+3.3 V相连,配置为高电平,为保证设备长时间处于数据接收状态,保持串并转换功能始终处于有效状态,将芯片配置为上升沿敏感模式,需要配置高电平,将TCLK_R/F连接3.3 V电源。LVDS接收端电路如图6所示。

4 系统关键技术研究

在本次设计中,为了实现高速存储数据,普通边擦边写模式不能满足要求,因此对Flash的写入模式进行合理的选择,选用2片Flash交叉双平面的编程方法,理论上实现最高速度为100 MB/s。具体操作为将视频数据流分成2支编写到Flash芯片,chip1和chip2分别为标记2片Flash;block代表Flash中的块,page代表Flash中的页。

当存储器接收波门1的4 096字节数据存入chip1中plane0的page0,然后接收波门2的数据写入chip1中plane0的page0,然后接收波门3的数据写入chip1中plane1的page0,与此同时对波门4中的数据进行操作,波门4中的数据写入chip2中的plane1的page0,在此时对chip2开始进行写入操作。同时对chip1中plane2的page0开始进行数据的写入操作,如此反复进行不间断操作。

视频数据采集的时序逻辑关系如图4所示。

当chip1、chip2所有的plane中block1的page0完成数据的编写操作,然后开始所有的plane中block1的page1进行数据的编写[15]。在2个page编写程序之间写入4个波门数据,所需时间约为4 096 Byte/

50 MB/s×4=327.68 μs。

在逻辑设计上,编写4个波门数据需要时间327.68 μs,高于200 μs(页编程典型时间),但是低于700 μs(页编程峰值时间),在编程上,由于受到视频流传递速度的影响,没有200 μs停顿,否则会因为等候时间长导致存储数据丢掉,因此在设计时没有判断R/B信号状态,直接编写数据。

采用某型号系统单机对该系统实施测试,并通过LVDS接口将视频数据发送给存储器进行保存。由系统单机产生脉冲信号,数据采集后分组编帧,帧结构见表1,每4 096个Byte为一帧,其中采集的脉冲数据为前4 084个字节,帧结构为后12个Byte。在试验过程中,利用LVDS接口,存储器对采编器传递来的视频数据,接收并进行保存,试验完成后通过计算机读取数据,图11为读取脉冲数据截图。

图11 脉冲数据截图

5 结束语

本文根据系统可行性分析以及高速视频数据的采集记录装置的关键技术设计要求,通过全方位和反复的测试,数据传输存储的误码率最高为0.1%,经多次测试,误码现象未再出现。本文设计的视频监测存储系统性能平稳、可靠、数据传递稳定满足任务要求。

步骤4 以加权SHNN-CAD为例,若pi>ε1,则将该目标回波判定为SST,其中ε1为异常程度值门限,i=i+1;

(3)模拟工况测试阻垢率实验。为了使模拟工况测试阻垢率实验不受试样腐蚀的影响,实验选取825耐腐蚀合金,在60℃、常压的条件下进行挂片实验72 h。阻垢率按式(4)计算。