一种具有噪声整形功能的2 bit/cycle SAR ADC的设计

2022-05-12陈志铭高一格张蕾王兴华

陈志铭,高一格,张蕾,王兴华

(北京理工大学 信息与电子学院, 北京 100081)

逐次逼近型模数转换器(SAR ADC)因其结构简单、易于数字化、功耗低等优点,得到了广泛的应用,但是与其他类型ADC 如快闪型、流水线型和折叠型ADC 相比,SAR ADC 的速度相对较慢,因为传统SAR ADC 需要至少N+1 次转换才能得到N位数据[1].

本文设计了一种2 bit/cycle 结构的SAR ADC,每个比较周期量化2 位数据,N/2+1 个周期即可输出N位数据,提高了SAR ADC 的转换速度. 每个比较周期内的工作原理相当于采用一个2 位的快闪型ADC,整个转换周期采用异步SAR 逻辑完成信号的逐次逼近[2].

电容DAC 阵列采用上极板采样技术和分裂(split)电容式排布结构,减少了电路所需的电容数目,缩减了电容阵列的建立时间. 电容DAC 阵列的翻转由异步SAR 逻辑直接控制,提高了ADC 的转换速度. 此外,为了进一步提高ADC 的动态性能,尤其是信噪失真比(signal to noise and distortion ratio,SNDR),本设计应用了一种噪声整形技术[3],其电路结构简单、功耗低,只需要2 bit/cycle 电路结构基础上稍作改动即可实现噪声整形功能,在一定条件下可以有效提高ADC 的性能指标.

1 2 bit/cycle SAR ADC 结构及原理

为了实现2 bit/cycle 的工作方式,本文设计的SAR ADC 采用了2 个电容DAC 阵列和3 个比较器,此外还包括采样开关、异步SAR 控制逻辑和编码电路等功能模块,系统整体结构如图1 所示.

图1 2 bit/cycle SAR ADC 架构示意图Fig. 1 2 bit/cycle SAR ADC architecture diagram

电容阵SIG_DAC 完成对输入信号Vin的采样及实现整个转换过程的逐次逼近逻辑,电容阵REF_DAC 产生每次比较所需的参考电平. 在每个比较周期中,比较器CMP2-CMP1 将SIG_DAC 得到的信号和REF_DAC 产生的2 个参考电平、额外的参考电平“0”进行比较,相当于一个内嵌的2 bit Flash ADC,每个比较周期得到2 位数字码,大大提高了SAR ADC 的转换速度.

2 bit/cycle SAR ADC 的具体量化过程如图2 所示. 在比较周期P1 中,比较器CMP2-CMP0 将通过采样周期P0 得到的输入信号VSIG[P0]分别与+1/2Vref、0、−1/2Vref进行比较,比较结果经编码电路得到最高2位数字码,同时SAR 逻辑控制电容阵SIG_DAC 完成残差处理. 高2 位数字码11、10、01、00 对应的残差电压产生方式分别为−3/4Vref、−1/4Vref、+1/4Vref、+3/4Vref,REF_DAC 产生的参考电平按每比较周期1/4 的比例缩小. 一次完整的量化过程包括1 个采样周期和4 个比较周期,共得到8 位数据.

图2 2 bit/cycle SAR ADC 量化过程Fig. 2 2 bit/cycle SAR ADC quantization process

2 2 bit/cycle SAR ADC 电路实现

2.1 SIG_DAC 和REF_DAC

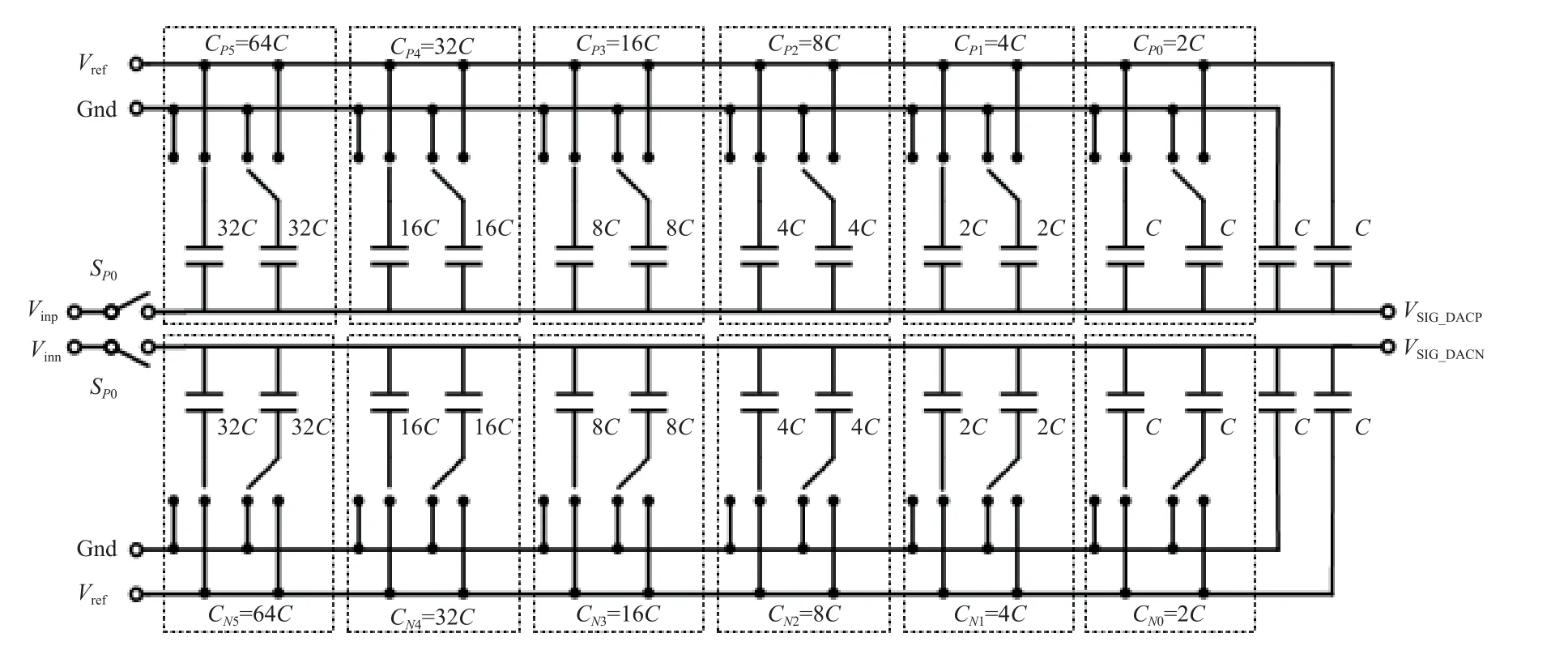

与传统的DAC 电容阵不同[4],本设计的电容阵SIG_DAC 采用上极板采样技术和分裂电容式结构,其结构如图3 所示.

上极板采样的全差分输入信号与比较器输入端直接相连,采样周期结束后,无需任何电容切换过程,比较器立刻进行最高位的比较,相较于传统的下极板采样,上极板采样技术节省了最高位电容. 以8 位SAR ADC 为例,传统的下极板采样的最高位电容为128C,而上极板采样所需最高位电容为64C,其中C为单位电容. 采用上极板采样技术,不仅使电容阵的单位电容总数减少一半,而且随着电容总值的减小,电容阵的建立时间也随之减小,提高了ADC 的工作速度.

分裂电容结构是将最低位电容之外的所有电容拆分为容值相等的2 个电容,如图3 虚线框内所示.电容上极板通过采样开关与输入信号相连,并直接连接比较器输入端,在采样阶段,电容下极板分别接Vref和Gnd,在比较阶段,SAR 逻辑根据比较器结果控制电容下极板翻转. 这种开关切换方式保证了输入信号共模电压在比较过程中保持不变,减小了比较器的动态失调电压.

图3 分裂电容结构SIG_DACFig. 3 Split capacitor structure of SIG_DAC

电容阵REF_DAC 的电路结构如图4(a)所示,是一个全差分电容DAC 阵列,输出全差分参考电压VREF_DACP和VREF_DACN. 为了得到图2 所示参考电平VREF_DAC(P-N)与VREF_DAC(N-P),其值分别为±1/2Vref、±1/8Vref、±1/32Vref和±1/128Vref,电容CP(N)5−CP(N)1的容值依次设为192C、48C、12C、3C、C. 在整个转换周期中,两个最高位电容CP5、CN5作为配平电容,下极板始终与共模电平Vcm相连,其余电容在一组互补信号Φ1−Φ4与Φ1~−Φ4~的控制下进行开关切换,图4(b)为Φ1−Φ4的示意图.

图4 REF_DAC 的电路结构及控制信号Fig. 4 Circuit structure and control signals of REF_DAC

在采样阶段,所有电容上极板通过采样开关SP0与共模电平Vcm相连,参考电压VREF_DACP=VREF_DACN=Vcm,Φ1−Φ4为高电平,控制Cp5−Cp1下极板接Gnd,Φ1~−Φ4~为低电平,控制CN5−CN1下极板接Vref. 在比较阶段,各电容在控制信号的控制下进行开关切换,依次得到4 个比较周期的参考电平Vcm±1/4Vref、Vcm±1/16Vref、Vcm±1/64Vref和Vcm±1/256Vref. 电 容 阵REF_DAC 在 整个比较周期中采用单调的开关切换方式,大大减小了电容翻转功耗,提高了工作效率.

另外,由于两个电容DAC 阵列的电容上极板均与比较器输入端直接相连,比较器输入管的寄生电容会对二者的相对精度造成影响. 为了保证SAR ADC 的量化精度,电容阵SIG_DAC 与电容阵REF_DAC 的总电容值需相等,若电容阵SIG_DAC 的单位电容为CS,REF_DAC 的单位电容为CR,那么CS=2CR.本设计中CR为5 fF,CS为10 fF.

2.2 动态比较器

本文所采用的动态比较器由预放大器和锁存器两部分构成,如图5 所示,MOS 管直接由比较时钟信号CLKC 控制,静态功耗低,适用于低功耗SAR ADC.预放大器在DAC 电容阵与锁存器之间,起到了隔离的作用,减小了比较器的回踢噪声,锁存器采用正反馈结构,比较速度快.

图5 预放大器和动态锁存比较器Fig. 5 Preamplifier and dynamic latch comparator

两组差分信号VINP、VINN和VREFP、VREFN通过预放大器的两组输入对管使输出端节点以不同的电流进行放电,将输入端之间的电压差信号转换为时间差信号. 锁存器为正反馈结构,CLKC 为低电平时,锁存器进行置位,比较器输出低电平,CLKC 为高电平时,锁存器将输入端先到达的变化沿进行锁存,随后将锁存稳定的信号输出,得到比较结果. 同时,动态比较器的两个输出信号Ci和Cib通过一个与非门产生整个SAR ADC 电路所需的异步时钟VALID. 本设计中比较器的输入比较电平为

2.3 动态寄存器和SAR 控制逻辑

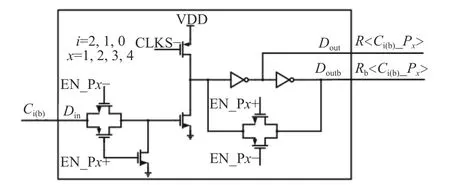

本设计采用的动态寄存器结构如图6 所示,在SAR 控制逻辑的要求下,每一个比较周期需要4 个寄存器,每个转换周期包含4 个比较周期,因此设计共需4 组16 个动态寄存器.

图6 动态寄存器Fig. 6 Dynamic register

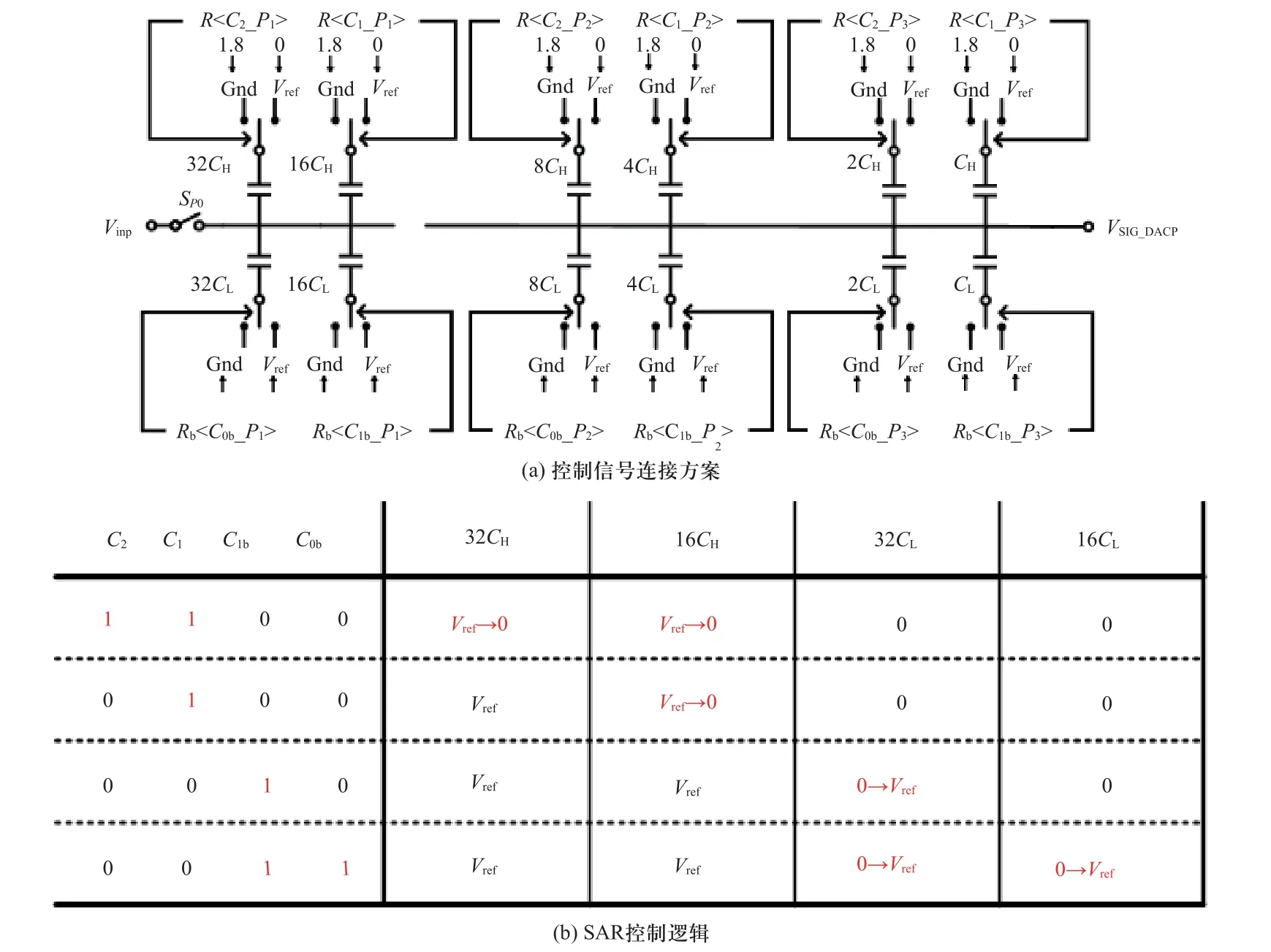

在采样阶段,动态寄存器在复位信号CLKS-的控制下进行复位,此时控制信号Dout=0,Doutb=1,控制电容阵SIG_DAC 中对应的电容下极板分别接Vref和Gnd,为第一个比较周期做准备,图7(a)所示为各控制信号与电容阵SIG_DAC 的P端电容的连接方案.在比较阶段,4 组动态寄存器在使能信号EN_Px 的控制下交替工作,每一个比较周期只需要1 组动态寄存器. 每一组动态寄存器的4 个输入依次连接比较器的4 个输出C2、C1、C1b、C0b,当输入为0 时,寄存器输出不变,当输入为1 时,Dout=1,Doutb=0,对应的电容进行翻转,SIG_DAC 进行残差处理,产生下一个周期所需的比较电平. 动态寄存器根据比较器输出结果,直接对DAC 电容阵列进行切变,图7(b)所示为P端最高2 位的SAR 控制逻辑. 这种动态寄存器交替工作模式和简单直接的SAR 控制逻辑,在提高了ADC 转换速度的同时,也保证了低功耗的特性.

图7 连接方案与SAR 控制逻辑Fig. 7 Connection scheme and SAR control logic

2.4 时钟产生电路

为了提高ADC 的转换速度,同时避免片内使用高频时钟信号,本设计采用异步时序,时钟产生电路如图8 所示.

图8 时钟产生电路Fig. 8 Clock generation circuit

当比较器作出判决,比较器的输出结果通过一个与非门将异步时钟VALID 拉至高电位,VALID 通过或非门将比较器时钟CLKC 拉至低电位,比较器进入复位状态后,VALID 重回低电位,随后将CLKC拉至高电位,比较器再次进入比较状态,进行新一轮判决. 异步时钟VALID 与比较器时钟CLKC 交替推进,每一次比较完成后立刻进入下一次比较过程,提高了ADC 的转换速度.

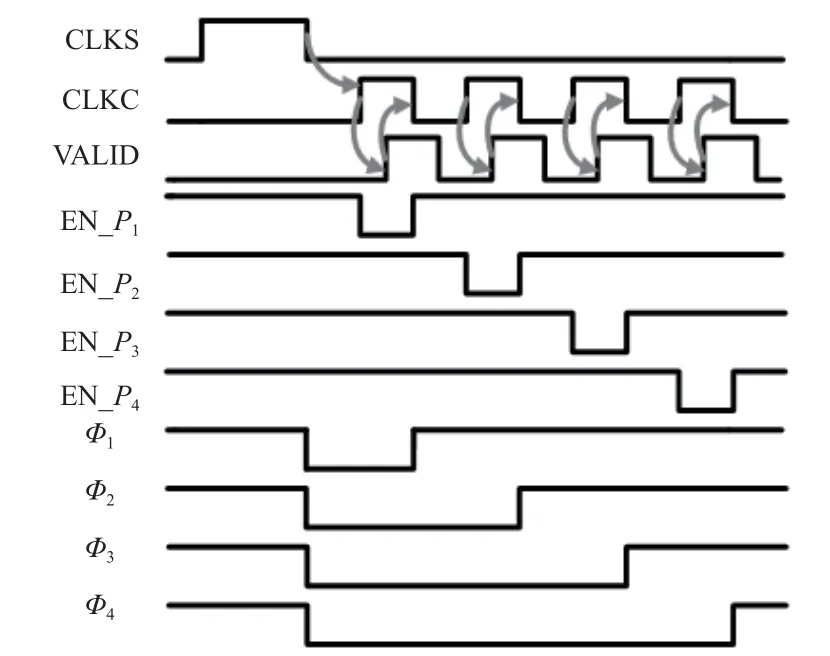

时钟产生电路对应的时序图,如图9 所示,其中Φ1−Φ4为电容阵REF_DAC 的控制信号,为比较器提供参考电平,EN_Px为SAR 控制逻辑所需的动态寄存器的使能信号.

图9 异步控制时序图Fig. 9 Asynchronous control timing diagram

3 噪声整形

本文所采用的噪声整形技术为一阶噪声整形,其工作原理是将电容阵SIG_DAC 在4 个比较周期之后的剩余电压Vres进行积分后反馈到比较器的输入端[5]. 在2 b/cycle 结构的时序中加入额外两个时钟信号Φns0与Φns1,这两个时钟信号到来之前,SAR ADC 进行2 bit/cycle 结构的常规转换,且在常规转换阶段中,没有额外的电容与Vres相连,避免了信号衰减的问题.

噪声整形的电路结构如图10 所示,图中用单端说明,电容阵与比较器之间额外加入电容C2、C3. 在Φns0期间,电容C2与DAC 电容阵相连,电容阵总电容为C1;在Φns1期间,电容C2将电荷转储至电容C3,实现了剩余电压Vres的转移,电容C3得到电压Vt并反馈到比较器的输入端. 在下一个采样信号CLKS 到来时,C2上的电荷被清除,ADC 配置回常规2 bit/cycle工作模式,直到下一个Φns0周期到来,C2将会获得新的剩余电压.

图10 噪声整形电路结构Fig. 10 Noise shaping architecture

由于加入噪声整形功能,需对比较器进行一定的改动,如图10 中右侧虚线框内所示,加入第3 对输入管,分别输入反馈电压Vtp、Vtn. 此时,比较器的输入比较电平为

本设计中采用的电容值为C1=C2=C3=128 CS,因此一阶噪声传递函数为(1−0.5 Z−1). 同时由于这种电路结构只能集成部分剩余电压Vres,造成了一定的衰减,会影响噪声整形的性能效果,因此需要通过改变相应的比较器输入对管的尺寸来提供一定补偿.

4 测试结果

基于180 nm CMOS 标准工艺,电源电压为1.8 V,采样频率为100 MS/s,输入信号共模为0.9 V,幅度为1.6 V,本文的2 bit/cycle SAR ADC 完成了仿真测试.

未加入噪声整形时2 bit/cycle ADC 的仿真结果如图11 所示,加入噪声整形后整体的仿真结果如图12 所示. 未加入噪声整形时,当输入频率为4.363 MHz时,SNDR 为46.22 dB,SFDR 为62.55 dB,有效位数为7.39 bit. 加入噪声整形后,当输入频率为4.363 MHz,过采样率(OSR)为10 时,SNDR 为57.49 dB,SFDR为66.35 dB,有效位数为9.26 bit.

图11 未加入噪声整形时的仿真结果Fig. 11 Simulation results without NS

图12 加入噪声整形后的仿真结果Fig. 12 Simulation results with NS

从以上仿真结果可知,本设计的2 bit/cycle SAR ADC 在输入频率为4.363 MHz 时,SNDR 为46.22 dB,电路精度为8 bit. 在此基础上加入噪声整形技术,当OSR 为10 时,SNDR 被提升到57.49 dB,相当于将8 bit 结构ADC 电路的精度提升了2 bit,达到10 bit.

未加入噪声整形技术时,电路的整体功耗为7.80 mW,加入噪声整形技术后,电路的整体功耗为7.98 mW,由此可见本文所采用的噪声整形结构仅以很小的功耗代价大大提高了该ADC 的有效位数.

表1 将本设计与其他已有设计的性能进行了比较. 文献[3]、文献[5]及本文的“精度/bit”指标如表中所示,括号外数据为未加噪声整形功能时ADC 的精度,括号内数据为加入噪声整形功能后ADC 的精度,说明噪声整形技术对ADC 精度的提高作用. 同时,与文献[4]和文献[6]相比,本文采用2 bit/cycle结构与噪声整形技术相结合的整体结构,使得SAR ADC 可在更低功耗或更小FOM 值下实现更高的有效位数.

表1 性能对比表Tab. 1 Performance comparison table

5 结 论

本文设计了一种2 bit/cycle 结构的8 bit、100 MS/s SAR ADC,并采用噪声整形技术提高过采样时该ADC 的分辨率. 设计使用两个DAC 电容阵列实现2 bit/cycle 量化,利用上极板采样技术和分裂电容式结构减少了电容数目,提高了ADC 的工作速度. 在保持SAR ADC 常规转换模式的基础上,为了进一步提高ADC 的动态性能,本设计新加入了噪声整形功能,电路结构简单且高效,仿真结果表明,当过采样率为10 时,SAR ADC 的精度由8 bit 提升到10 bit,ADC 的有效位数得到了显著提高.