基于FT⁃2000/4 的高速接入系统设计与实现

2022-05-12何赞园邢留洋

高 远,何赞园,邢留洋

(1.中国人民解放军战略支援部队信息工程大学,河南 郑州 450000;2.郑州大学,河南 郑州 450000)

0 引 言

网络空间已成为国家继陆、海、空、天四个疆域之后的第五疆域,自主可控是保障网络安全、信息安全的前提。接入设备作为网络基础设施,实现其自主可控对提升网络数据的安全性具有重要意义。

一般来说,国产产品和服务容易符合自主可控要求,因此实行国产替代对于达到自主可控是完全必要的。本文从实际应用出发,根据当前国产化先进电信计算架构(Advanced Telecom Computing Architecture,ATCA)平台的高速网络数据接入需求,基于天津飞腾技术有限公司发布的新一代国产高性能通用处理器FT⁃2000/4,设计实现满足需求的自主可控数据高速接入系统。该系统主要完成IP 分组域数据的接收、筛选和分发功能,提供4 路10GE 速率的数据平面通道、2 路GE 速率的控制平面通道,实现数据与控制分离。

1 FT⁃2000/4 处理器

自2001年启动国产处理器设计项目至今已有20年,国内产生了以龙芯、申威、飞腾、鲲鹏、海光、兆芯为代表的国产CPU 品牌,为构建自主可控的国产化计算平台奠定了基础。

其中,FT⁃2000/4是天津飞腾技术有限公司于2019年发布的新一代高性能通用处理器,主要面向桌面应用及高端嵌入式领域的应用。该处理器集成了4 颗自主研制 的FT663 内 核,兼 容64 位ARMv8 指 令 集,16 nm 制程,主频2.6 GHz,内置密码加速引擎,最大功耗14 W。

从目前已经发布的国产处理器产品来看,相较于龙芯和申威这类采用自主研制指令集的CPU,FT⁃2000/4处理器的ARMv8 指令集架构具有更好的软硬件生态,同时相较于兆芯这类采用x86 指令集架构的CPU,FT⁃2000/4 处理器具有更高的自主可控等级。因此,综合考虑当前的国产CPU 发展现状、性能表现、软硬件生态以及自主可控程度,选用FT⁃2000/4 处理器设计自主可控的高速接入系统。

FT⁃2000/4 处理器并未针对通信应用场景提供高速网络接口,仅提供2 个RGMII 接口。为了实现多个线路侧的数据接入网络接口,利用FT⁃2000/4丰富的PCIe 3.0通道资源,设计万兆以太网接入模块,能够提供4 路10GE 速率端口用于高速数据的接入与分发。

2 系统总体结构设计

为了符合实际应用场景的需求,系统设计基于ATCA架构,该架构是全球PCI 工业计算机制造组织(PCI Industrial Computer Manufacturers Group,PICMG)制定的新一代主流电信级模块化通信平台标准,旨在推广电信级硬件系统的开放式标准架构,能够为电信级系统解决带宽、成本和扩展维护等问题。ATCA 平台的特点是底板与底板之间采用点对点交换互连结构以实现高速数据传输。底板的连接被分成三个区域:ZONE1、ZONE2、ZONE3。ZONE1 中的连接器向底板提供电源和扩展机架管理信号;ZONE2 中的连接器提供了到Base 通道和Fabric 通道的连接,Base 接口支持10 Mb/s,100 Mb/s,1 000 Mb/s的以太网通信,Fabric接口采用高速并串行和串并行转换器(Serializer/Deserializer,SerDes)提供高达2.1 Tb/s 的带宽,支持以太网/光纤信道传输、InfiniBand 传 输、星 型 传 输、PCI Express 传 输 或 串 行Rapid I/O 传输五种协议规范;ZONE3 中的连接器是用户可定义的,通常用于将前面板连接至后部转换模块(Rear Transition Module,RTM)。

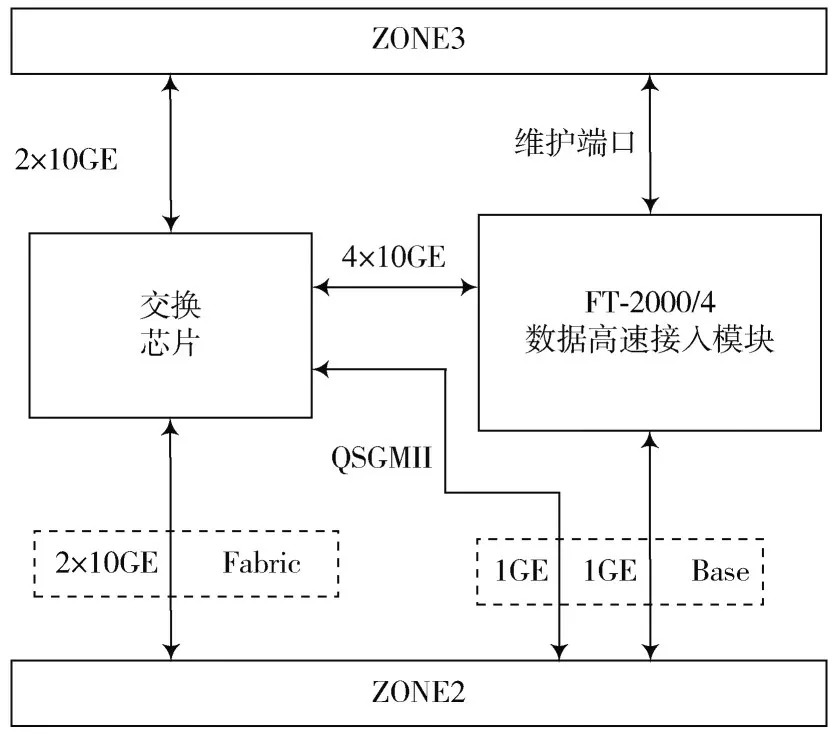

基于FT⁃2000/4 的高速接入系统网络拓扑如图1 所示,由ZONE2和ZONE3连接器、交换芯片以及FT⁃2000/4数据高速接入模块四个部分组成。遵循ATCA 规范,IP分组域的数据通过RTM 背板的2 路10GE 端口接入ATCA 底板的ZONE3 连接器。之后,数据通过系统内的交换芯片转发给FT⁃2000/4 数据高速接入模块,经过筛选后再通过交换芯片分发到ZONE2 连接器的Fabric通道。

图1 系统网络拓扑图

系统提供2 路GE 速率端口连接Base 平面,用于主控板卡实现单板的控制功能。另外,提供一个千兆的维护端口连接ZONE3 连接器,通过RTM 背板转出,方便单板内高速接入模块的直接调试维护。

2.1 交换芯片

在ATCA 底板设计时,由于走线距离过长,直接将数据高速接入模块的10GE 端口连接ZONE2 连接器的Fabric 通道会导致因信号强度不足,高速接入模块无法驱动数据在Fabric 通道进行传输,影响后续的业务处理流程。为了解决该问题,使用交换芯片控制高速链路的聚合与分发。系统中选用盛科网络自主研制的国产高性能以太网交换芯片CTC7148,能够提供1G/2.5G/5G/10G/25G/40G/50G/100G 的端口速率。这样一来,IP 分组域数据接入系统时,将其直连到交换芯片,由交换芯片控制数据在ZONE3 与FT⁃2000/4 高速接入模块之间的交互过程,再通过交换芯片与ZONE2 连接器直连,驱动高速接入模块分发的数据在Fabric通道内进行传输。

2.2 Base 控制平面设计

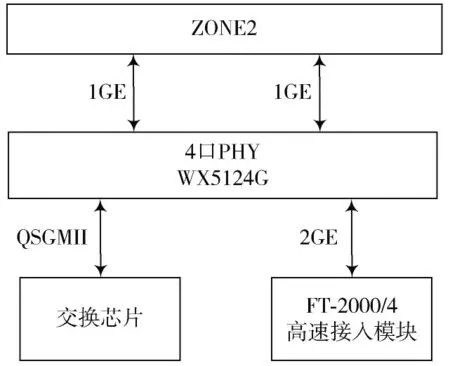

系统中控制平面设计如图2 所示,提供2 路GE 速率的端口分别用来访问控制交换芯片和FT⁃2000/4 高速接入模块。交换芯片的1 路QSGMII 接口与FT⁃2000/4 高速接入模块的2 路GE 速率接口同时连接一个4 口PHY芯片。PHY 芯片使用物芯科技自主国内设计、国内流片的4 端口千兆物理层接口芯片WX5124G,MAC 侧接口 支 持RGMII、SGMII 及QSGMII。PHY 芯 片 将2 路GE速率端口接入ZONE2 的Base 通道连接器,实现主控板卡通过Base 平面访问控制功能。

图2 Base 控制平面结构图

3 FT⁃2000/4 数据高速接入模块设计

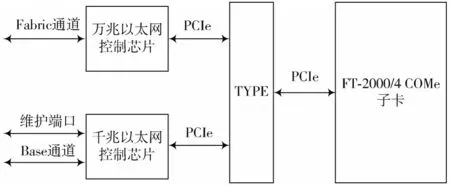

基于FT⁃2000/4 设计实现的数据高速接入模块是系统的核心模块,在上文系统的整体结构叙述中介绍了该模块的基本接口资源,其系统结构如图3 所示。该模块面向Fabric 通道的连接需要4 路10GE 速率端口,面向Base 通道连接需要2 路2GE 速率端口,然而FT⁃2000/4作为面向桌面级应用的处理器仅能提供2 个RGMII 接口,并不支持多路万兆网口的接入。因此,综合考虑FT⁃2000/4 的接口资源,本文提出一种基于PCIe 扩展总线的解决方案。

图3 FT⁃2000/4 数据高速接入模块系统框图

PCIe 是一种高速串行计算机扩展总线标准,设备与主机之间采用端到端的连接方式,具有独立的串行链路,支持任何两个端点之间的全双工通信,而且对跨多个端点的并发访问没有固有的限制。通过PCIe 总线扩展芯片的接口资源是目前大部分系统设计实现功能扩展的方式。为了实现10GE 速率的数据接入端口和多个GE 速率的控制端口,在FT⁃2000/4 数据高速接入模块中选用集成了媒体接入控制器(MAC)和物理接口收发器(PHY)的以太网控制芯片来提供系统中所需的网口资源。同时系统内采用模块化结构,基于COM Express 3.0规范,设计FT⁃2000/4 COMe 子卡,通过TYPE 连接器将FT⁃2000/4 处理器的PCIe 总线转接到以太网控制芯片。COM Express 3.0 PICMG 定义的计算机模块标准是一种高度集成的单板计算机。每个COM Express 模块都集成了CPU、内存、通用I/O 接口、USB、音频、图形(PEG)和以太网。所有I/O 信号都映射到模块底部的两个高密度薄型连接器,即TYPE 连接器。规范中共定义了8 种不同的TYPE 输出接口,每种接口提供不同种类和数量的引脚排列。考虑到系统中ATCA 底板所需转接通道类型和数量,选择TYPE 6 连接器,该连接器能够提供24 Lanes PCIe 接口、4 路SATA 接口、1 路带有集成PHY的千兆网接口、8 路USB 2.0 端口、4 路USB 3.0 端口、2 路LVDS 接 口、1 路VGA 接口、3 路DDI 接口以及2 个TX/RX 串行对,可选择一个端口作为CAN 接口,足够满足FT⁃2000/4 COMe 子卡所需映射的I/O 接口。下文将对以太网控制芯片的芯片选型、FT⁃2000/4 的PCIe 总线配置、COMe 子卡的基本结构进行阐述。

3.1 以太网控制芯片

根据自主可控的基本要求,以太网控制芯片选用北京网迅自主设计的WX1820AL 和WX1860AL4。

WX1820AL 是万兆以太网控制芯片,带有两个完全集成的万兆以太网媒体存取控制器(MAC)和SFP+端口,具有优良的噪声抗扰性,同时还支持300 m 距离光纤连接,适用于服务器和高端设备,能够将PCIe X8 集成到万兆网络中,并且对网络I/O性能进行优化。其具备两个集成PHY 的10 Gb/s SFI/KR/XAUI/SGMII 端口,支持最大9.5 KB 的巨型帧。与上位机连接使用的是一个PCIe GEN3 X8 接口,同时支持PCIe 的复位和唤醒功能。

WX1860AL4 是4 口千兆以太网控制芯片,具备4 个集成PHY 的10 Mb/s,100 Mb/s,1 000 Mb/s 自适应速率RGMII 接口,通过PCIe GEN2 X4 接口与上位机连接。

因此,利用FT⁃2000/4 COMe子卡PCIe通道连接两个WX1820AL 万兆以太网控制芯片能够满足系统设计中所需的4 路10GE 速率端口,连接一个WX1860AL4 千兆以太网控制芯片能够提供Base 控制平面所需的GE 速率端口以及1 个维护端口。

3.2 PCIe 总线配置

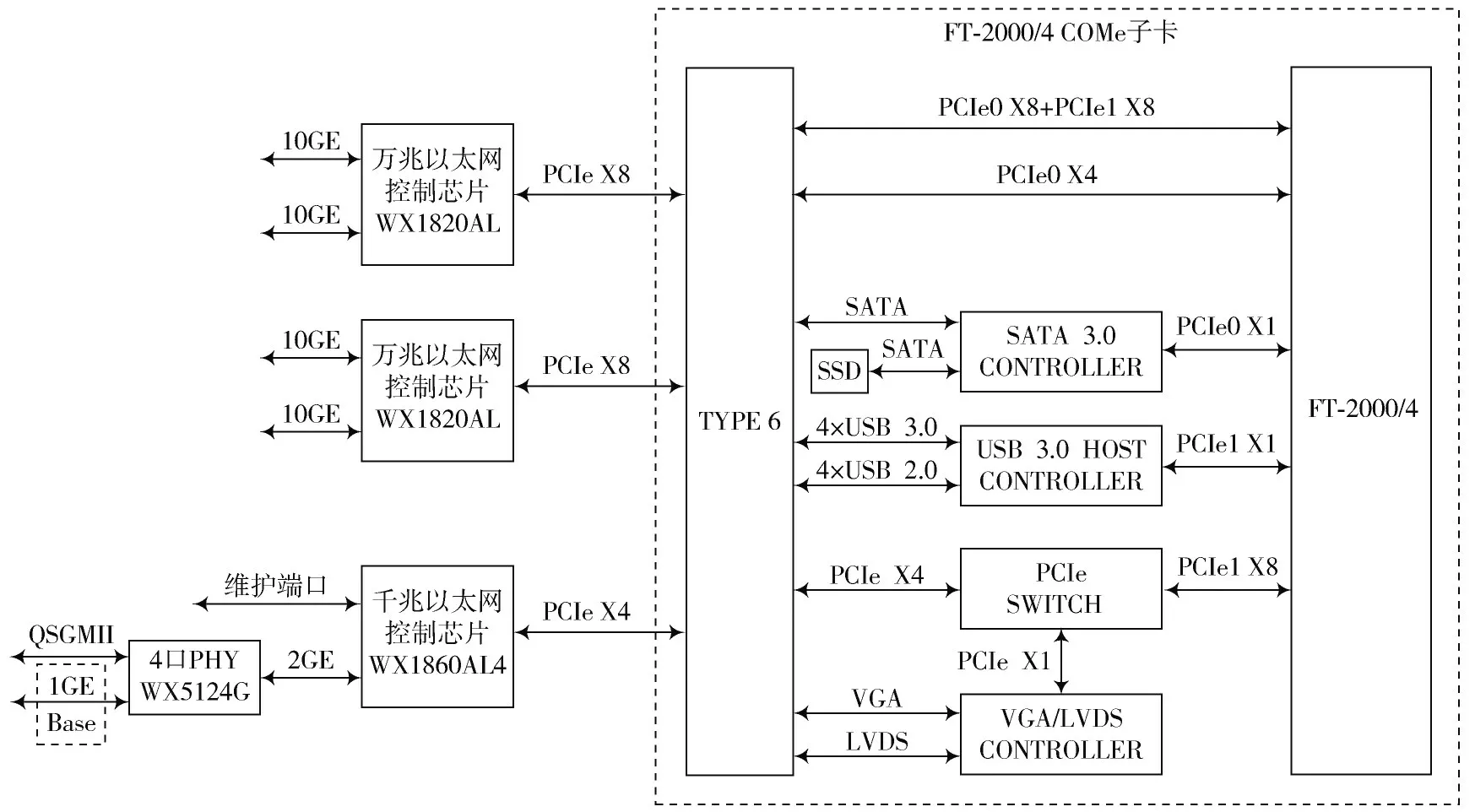

为了满足以太网控制芯片的接入需求和底板其他功能部件的实现,需要2 路PCIe X4 和2 路PCIe X8 接到TYPE6 底座上,此外还需要3 路PCIe X1 用于转换成VGA/LVDS、SATA、USB。

FT⁃2000/4 的PCIe 接口分为PEU0 和PEU1 两路接口,每路PEU 都支持PCIe 3.0 规范。其接口特性如下:

1)支持Root Complex 和End Point 两种模式,软件可配置;

2)两路PEU 共34 Lanes,每路为1 个X16 和1 个X1,其中X16 可拆分为2 个X8;

3)PEU 内部集成DMA 引擎,一读一写两个通道。

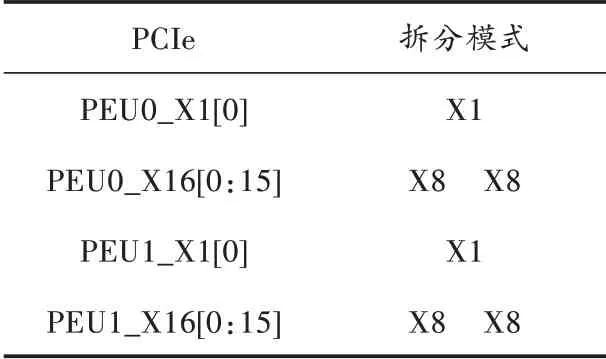

如图4所示,为了满足ACTA 底板需求,对FT⁃2000/4的2 路PCIe X16 接口进行拆分,拆分模式如表1 所示。

图4 FT⁃2000/4 PCIe 资源分配图

表1 FT⁃2000/4 PCIe 拆分模式

通过拆分,将FT⁃2000/4 的2 路PCIe X8 完全接到TYPE6 上,再将1 路PCIe X8 的4 Lanes 接到TYPE6 上作为1 路PCIe X4 使用。由于PCIe X8 不支持继续拆分成PCIe X4 和X1,因此在TYPE6 的信号适配中,选择通过PCIe桥片进行接口扩展。系统中选用89HPES16NT16G2芯片将剩余1 路PCIe X8 拆分成1 路PCIe X4 和4 路PCIe X1,其中PCIe X4 用于连接到TYPE6 上,剩余4 路PCIe X1 的1 路用于转换成VGA/LVDS,其他3 路PCIe X1 接口备用。

另外,FT⁃2000/4 提供的2 路PCIe X1 接口也设计了具体的功能实现,PEU0_X1 连接SATA 3.0 控制芯片为COMe 子卡提供一个板内的SSD 芯片用于操作系统的安装,以及1 路SATA 总线通过TYPE6 接口转接到ATCA底板的M.2 插槽用于外接大容量存储设备。PEU1_X1连接USB 3.0 控制芯片,提供4 路USB 3.0 接口和4 路USB 2.0 接口。

3.3 FT⁃2000/4 COMe 子卡

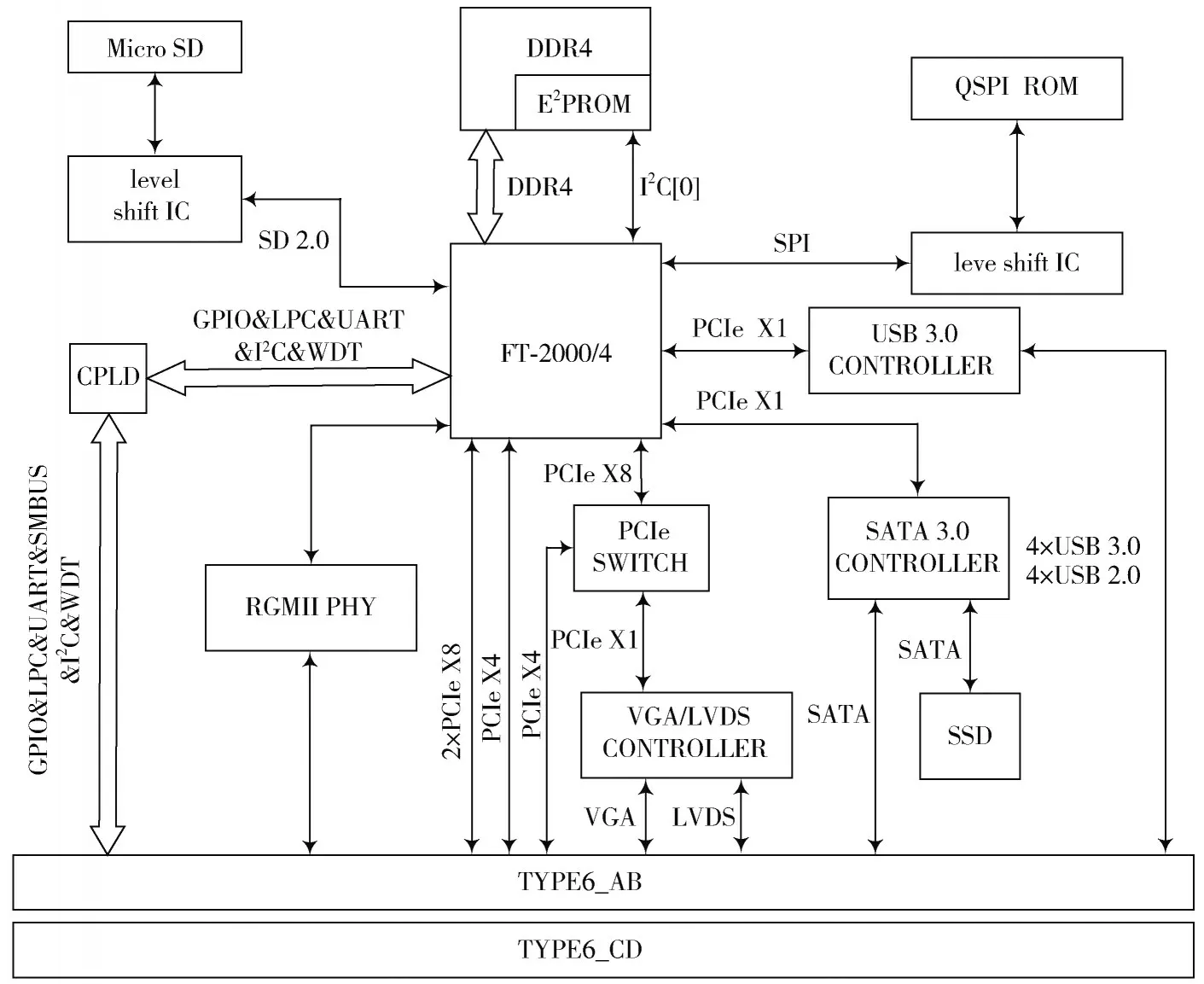

FT⁃2000/4 COMe 子卡作为一个完整的计算机系统,除了对PCIe 总线进行拆分配置外,如图5 所示,子卡内还包含DDR4 插槽、QSPI 底座、CPLD 功能模块、SD 卡插槽、RGMII网口等其他功能子模块,下面将对其中主要的DDR模块、QSPI模块、CPLD模块的设计实现进行介绍。

图5 FT⁃2000 COMe 子卡系统框图

3.3.1 DDR 模块

FT⁃2000 COMe 子卡采用小型双列直插式内存模块(Small Outline Dual In⁃line Memory Module,SODIMM)以减小内存模块的占用空间。内存条选用紫光的DDR4 内存条,型号为SCC08GS03H1F1C⁃26V。选择FT⁃2000 处理的DDR_1 内存控制器。FT⁃2000/4 的DDR4 通道最高支持3 200 Mb/s,可以通过调整FLASH 偏移地址0x000110 中的参数来调整DDR 速率。

3.3.2 QSPI 模块

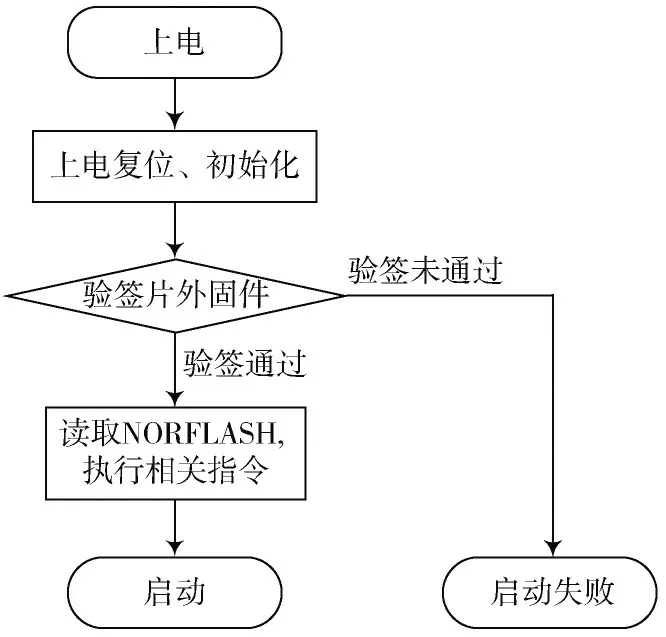

QSPI 接口兼容SPI,且作为启动加载片外固件的唯一接口。FT⁃2000 处理器的上电启动流程如图6 所示,CPU 启动后,首先通过片内可信根验签片外固件;验证签名通过后,通过QSPI接口的QSPI_CSN0片选的FLASH芯片加载固件,来执行相关指令。

图6 FT⁃2000/4 上电初始化流程图

在系统中,COMe 子卡的QSPI FLASH 模块采用QSPI SO16P127 插座的设计,便于调试过程中多次拆卸QSPI FLASH。

3.3.3 CPLD 模块

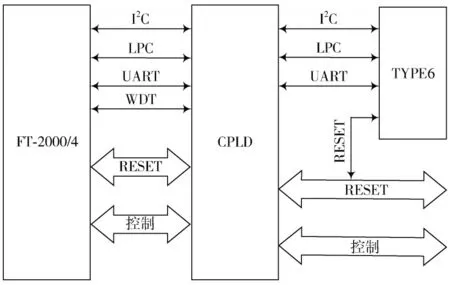

系统中选用高云GWIN⁃UV4LQ144C6 作为COMe单板的逻辑芯片,该芯片内置了User FLASH,容量为608 Kb,同时有120 个I/O 口,还板载了一颗MCU 芯片,用户可以进行视频图像处理、高速数据采集等方面的应用。如图7 所示,在FT⁃2000 COMe 子卡内其主要承担复位逻辑、电平转换、接口转换和一些控制功能。

图7 CPLD 模块框图

4 系统测试

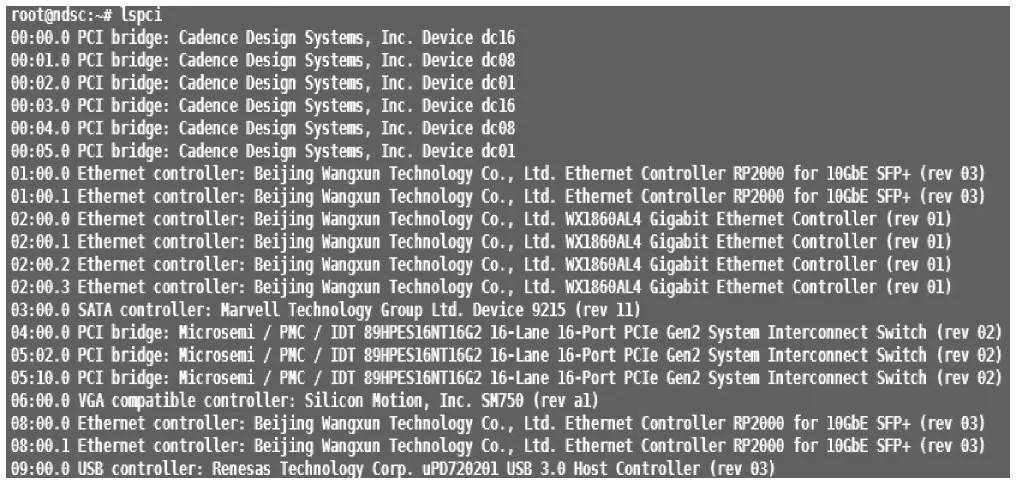

系统测试部分主要完成对系统中的万兆网口的带宽测试。操作系统选择银河麒麟操作系统,作为目前被广泛使用的国产操作系统,其对于各类国产芯片都有较好的驱动支持。测试平台选择标准14 槽ATCA 机架。上电后,FT⁃2000/4 COMe 子卡能够正常启动,通过维护端口连接子卡后查看PCIe 总线的设备连接信息,如图8所示。系统中能够看到的PCIe 设备信息包括4 路10GE速率的SFP+网口、4 路WX1860AL4 提供的GE 速率网口、SATA 3.0 控制芯片、USB 控制芯片、用于PEU1_X8接口转接的89HPES16NT16G2 PCIe 桥片以及连接该桥片的LVDS/VGA 控制芯片。

图8 PCIe 总线设备连接图

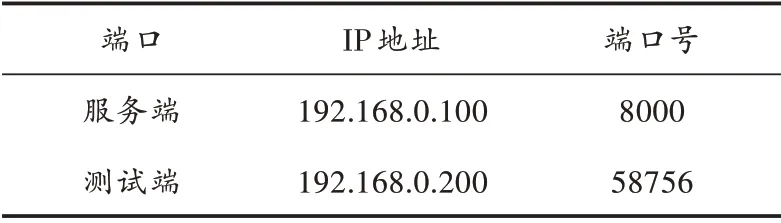

在对系统内的万兆网络端口划分VLAN 之后,使用iperf3 网络测试工具测试其中一个网口的最大带宽。使用两张同样的ATCA 单板进行测试,板卡之间的网络通过Fabric 通道连接,选择其中任意一张单板作为服务端,另外一张作为客户端,其对应关系如表2 所示。

表2 调试端口地址对照表

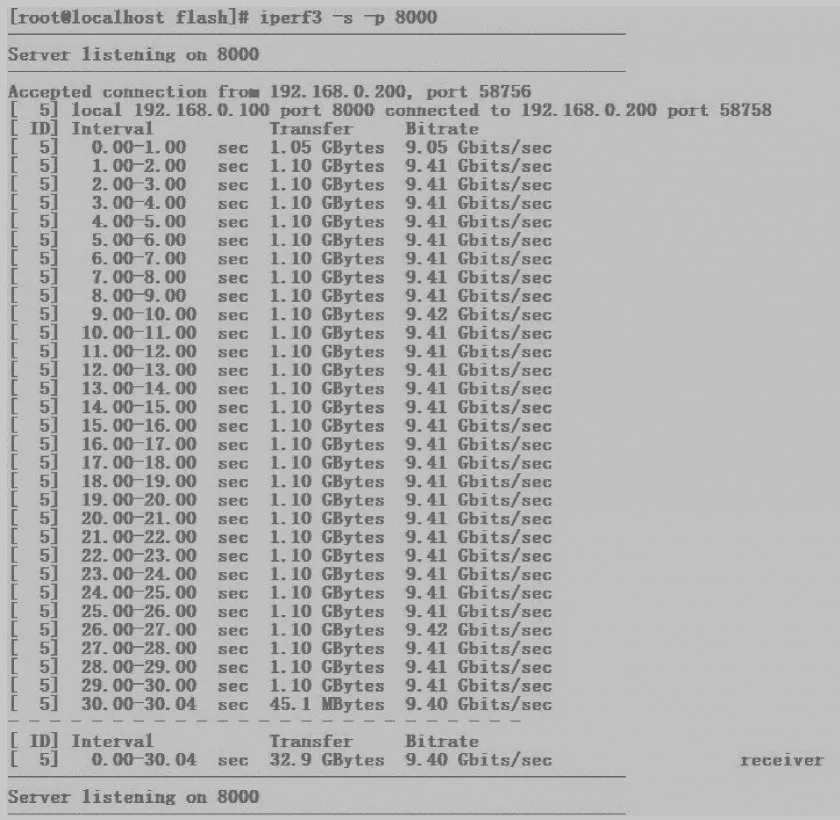

iperf3 工具提供的测试结果如图9 所示,该网口的最大带宽是9.4 Gb/s。实际测试中,由于传输距离、信号干扰、线材损耗等因素影响,实际最大带宽与理论设计的10 Gb/s 有误差属于正常情况,其他3 路10GE 速率网口在划分VLAN 之后的带宽测试结果都基本相同,不再做具体阐述。

图9 网口带宽测试结果

5 结 语

本文从自主可控的角度出发,介绍了一种基于FT⁃2000/4 的高速接入系统的设计实现。选择合适的以太网控制芯片,利用FT⁃2000/4 的PCIe 总线解决了该处理器不支持万兆网络接入的问题,扩展了应用场景。同时通过模块化的设计,使得文中基于FT⁃2000/4 设计的COMe 子卡不仅可作为通信处理机应用于通信系统中,还可支持更加丰富的应用场景。

注:本文通讯作者为何赞园。