基于Aurora的多通道高速可配置数据采集系统设计

2022-05-08祁永鑫吴爱平秦涛

祁永鑫,吴爱平*,秦涛

(1长江大学电子信息学院,荆州 434020;2北京尚微科技有限公司,北京 100089)

通过采集射频信号正交变换后的一组正交分量,可便于提取其瞬时幅度、瞬时频率和瞬时相位,由这些信息可进行波束成形、脉冲压缩等.系统多通道实时同步采集16组正交信号,采集后经过交织编码,依托高速串行协议Aurora上传至上位机,通过采集后的正交信号数据便可对射频信号展开研究分析.系统底层硬件参数封装为控制字指令由上位机直接配置,实现参数可视化,便于用户设定.在数据采集系统中采样率的确定是数据采集的首要任务,采样率设计过高会浪费带宽,增加数据处理的难度,采样率设计过低会导致频谱混叠,无法恢复原始信号[1].LMK03806器件是一款高性能、超低抖动、多速率时钟发生器,能够在频率高达2.6 GHz的条件下针对14路输出合成8个不同的频率,系统通过其为高速AD配置工作时钟实现采样率的配置,可为用户提供便利.

1 系统设计

1.1 系统简介

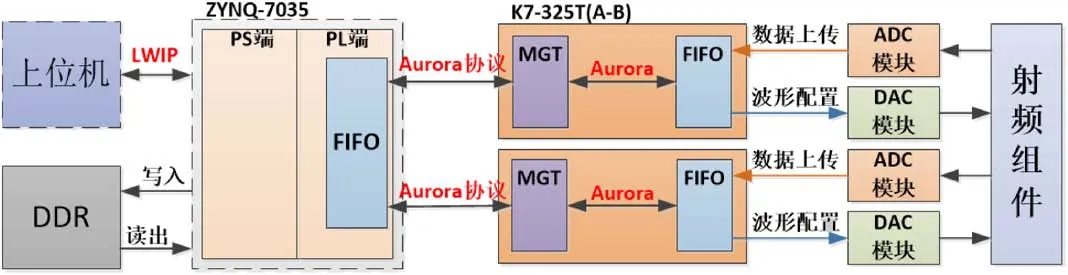

图1为系统结构框图,多通道高速可配置数据采集系统主要由米联电子ZYNQ-7000系列核心板MZ7035FA(简称Z7)、赛灵思FPGA芯片K7-325T(简称K7)、ADC模块和DAC模块组成.ADC选用ADI公司的四通道同步采样14位A/D转换器LTC-2175芯片,采样率为100 MSPS,信噪比SNR为73.1 dB,动态范围SFDR为88 dB,通过高位补零配置为16位双线道输出模式使用.DAC选用TI公司的16位DAC3484,采样率为100 MSPS,在使用过程中为对齐射频组件信号基准,DA输出端加有500 mV直流偏置.K7负责AD,DA工作状态的控制,采集数据的回传和关键信号的控制监测等,AD用于采集射频组件两正交分量信号,DA辅助采集系统产生任意波形,便于系统自检或为外围组件提供激励源.

图1 系统结构Fig.1 System structure

系统采用两块K7控制16路AD/DA信号(8组I、Q),DA部分主要用作发射波形,通过上位机下发控制字命令,配置DA内部数字振荡器NCO的频率,产生本振信号,使其与FPGA下发波形信号混频得发射波形.AD芯片通过将通道信号端子上的DA信号与AD采集信号短接作数据采集实现系统自检.多通道采集工作在采集同步脉冲信号的控制下同步进行[2].多通道采集数据通过FIFO缓存对齐,交织编码后打包,基于Aurora协议以5G/bps的速率进行数据传输.

为实现工程参数实时可控,特将底层参数全都封装于控制字模块,上位机控制字携带通道ID以广播的方式下发命令指示,底层K7解析通道ID及各模块所用控制字命令并执行相应功能,实现各模块有序工作.控制字命令的传输由上位机控制台程序基于LWIP协议与ZYNQ核心板通信.核心板通过Aurora协议实现控制字指令的下发和AD采集数据的回传[3].

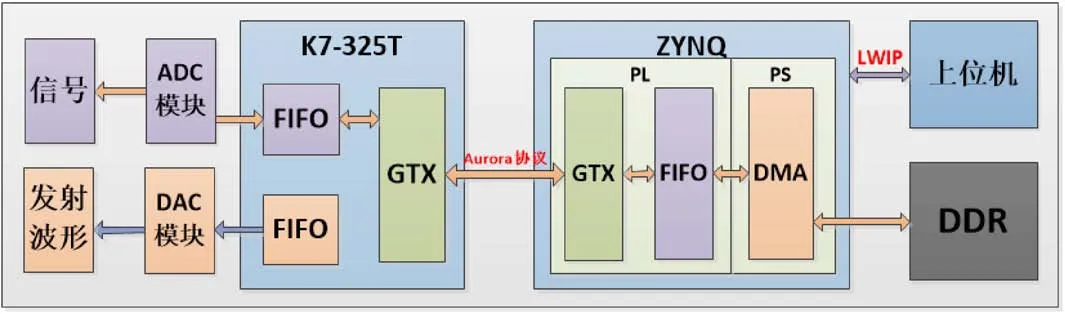

1.2 数据链路

系统数据链路如图2所示,AD模块采集信号,采集后的多通道数据经对齐、交织编码后打包缓存于深度8192,数据位宽32 bit的FIFO中.K7通过高速串行收发模块GTX将FIFO中32 bit数据按8 B/10 B编码为标准Aurora协议下40 bit数据上传至Z7.Z7芯片PL端接收数据并缓存于PL端FIFO中,而后由DMA将FIFO中数据搬运到内存DDR中通过PS端AMR核基于LWIP协议缓存采集数据.为便于系统自检,底层K7通过FIFO配置波形数据与DAC器件内部NCO产生的本振信号混频输出发射波形,为系统自检提供激励.

图2 数据链路Fig.2 Data link

AD采集信号的输入与DA发射波形的输出采用低振幅差分LVDS方式,该方式采用极低的电压摆幅高速差动传输数据,可实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等优点,适用于串行高速数据通信场合,满足设计需求.采用LVDS输出方式可减少数字噪声,简化PCB布局[4].

DA发射波形由基带信号和本振信号混频得到.K7内部波形产生模块产生波形数据缓存于FIFO中作为基带信号数据,DAC内部数字振荡器NCO通过控制字配置其本振信号频率,基带信号与本振信号混频得发射波形.由此可为射频组件提供激励源,验证其工作状态.

1.3 采集程序设计

采集程序设计思路如图3所示,为保证AD四通道数据交织编码准确,则需对AD四通道数据进行对齐操作.因此设计训练模式,通过SPI协议配置串行测试数据和AD工作状态,待单块AD四通道数据对齐再进入数据采集工作,以此保证后续交织编码准确.

图3 采集程序设计Fig.3 Acquisition program design

采集程序设计内容如下,首先通过SPI协议配置ADC器件LTC2175四通道串行数据,共计8组串行数据,配置数据由FPGA内部AD模块通过寄存器设定.若配置出错,则返回空闲状态,配置成功便进入串行解码操作.待数据串解并结束,开始对四通道并行数据进行训练,若四通道数据串转并后依然能够对齐,则表明通道数据对齐训练成功.而后进入工作模式,开始采集工作.采集后的数据经交织编码打包后通过Aurora协议上传至Z7,由Z7通过DMA搬运至内存DDR,完成采集.

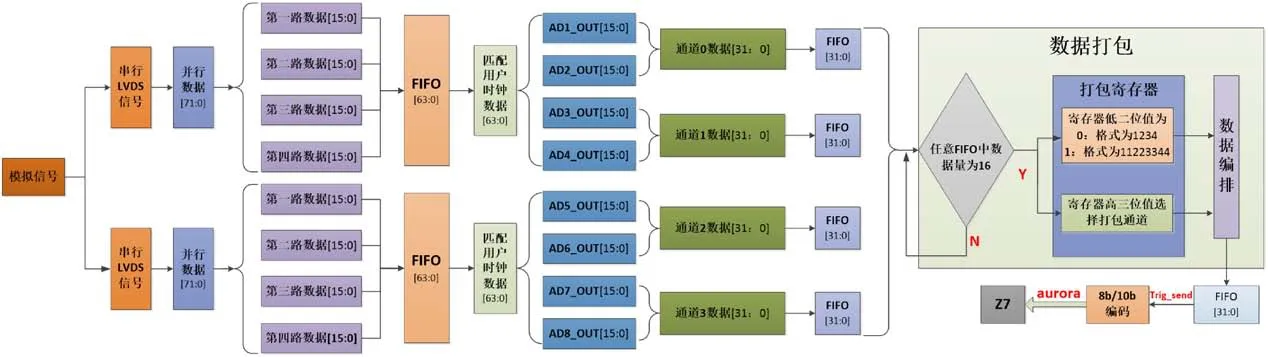

1.4 数据交织

数据交织过程为信号采集后串转并,匹配数据率,多通道数据交织编码后打包上传,具体操作如图4所示.

图4 数据交织Fig.4 Data intertwined

AD采集模拟信号输出串行数据,FPGA接收串行数据,将随数时钟差分转单端后,使串行数据转为4路16 bit并行数据[5].再经帧信号区分四路并行数据,由FIFO将同一AD采集的4路数据拼接输出64 bit数据,匹配用户时钟域,使4路数据在100 M时钟下传输,最后基于Aurora协议打包上传.

单路FPGA控制2块AD芯片,共采集8路AD数据,每两路拼接为位宽32 bit数据一起打包.拼接后的通道数据每一路过一级深度8192,位宽32 bit的FIFO缓存.当任意通道FIFO中缓存数据量达16便开始数据打包工作,打包数据的格式和打包数据通道的控制由位宽为5的寄存器设定.高三位控制打包通道的选择,低二位控制打包格式,若该寄存器低二位值为0则对应每个通道取一个数进行打包(1234),若该寄存器低二位值为1则对应每个通道连着取两个数进行打包(11223344).打包后数据缓存于深度为8192,位宽为32 bit的另一级FIFO,半满时通过送数脉冲Trig_send信号控制上传.

采集数据的上传,由高速串行收发模块GTX,在K7和Z7间基于Aurora协议进行数据的传输,通过高速串行编码8 B/10 B技术,将FIFO中32 bit数据编码至Aurora标准模块数据下40 bit数据进行传输[6].该编码方式可将线路数据对齐到字节/字,可保持良好的支流平衡,增加了数据的传输距离,有高效的错误检测机制.

两路K7采集工作在采集同步信号的控制下进行,实现16通道同步实时采集.数据通过FIFO交织,多通道数据对齐后在数据链路传输.两路K7均在100 M时钟下工作,时钟由同一个PLL锁相环产生,相位差固定.若某一通道有差异可通过延时对齐,最终实现多通道同步采集数据.

1.5 发射波形

发射波形功能的设计可辅助采集系统做自检工作,或为外部系统提供激励源[7].DA基于发射同步信号工作,多通道同步进行,发射信号可通过程序微调相位矫正,幅度系数矫正,发射延时等,实现多通道发射波形一致.波形产生原理为K7波形产生模块采用CORDIC算法生成波形数据,通过控制字指令配置DAC内部数字振荡器频率产生本振信号,二者混频得发射波形.

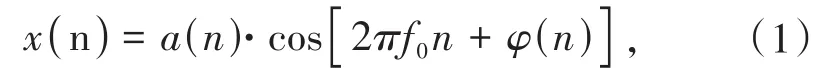

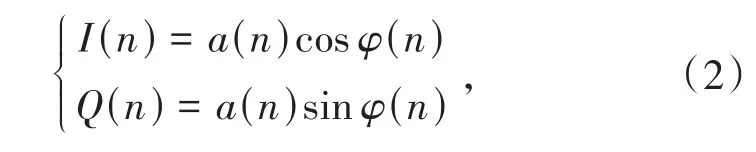

通过CORDIC算法产生一组正交信号,使其与本振信号混频可模拟射频信号x(n)的一组正交分量信号I(n)和Q(n).多通道交替输出I(n)和Q(n)信号,可为系统自检提供来源:

对x(n)进行正交变换得正交基带信号I(n)和Q(n)如式(2),由此很容易获取射频信号的三个重要特征:瞬时幅度a(n),瞬时相位φ(n),瞬时频率f(n)=

通过这两个正交分量,就可以按式(3)提取射频信号的三大特征:

瞬时频率f(n)也可以简写成式(4)(略去常数部分):

最后可化简为式(5):

从以上分析可以看出,只需采集这两个正交分量I(n)和Q(n),便可通过采集数据分析射频信号的特征,提供用户做数理分析.

发射波形环节主要为系统提供自检信号和产生外部射频设备激励源信号.其中奇数通道输出I(n),偶数通道输出Q(n),共计输出16路发射信号.系统设定采集信号为射频信号下变频为中频信号后的两个正交分量I(n)和Q(n).采集数据交织过程如图3所示,两分量信号合并为一路打包,再基于Aurora协议高速传输,最终为用户验证设计提供数据支撑.

2 系统实现

2.1 硬件电路

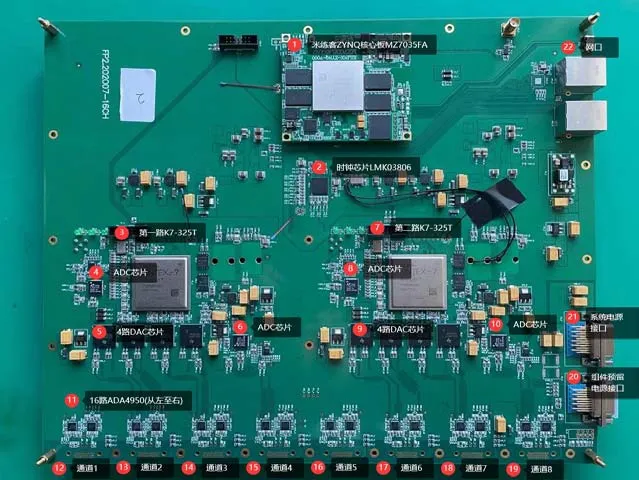

本系统采用米联客ZYNQ-XC7Z035核心板通过连接器插座固定于系统数字PCB板完成底层数据的接收工作和控制指令的下发,该架构处理器集成PS端双核ARM Cortex-A9+PL端Kintex-7架构28 nm可编程逻辑资源.PL端Kintex-7架构与底层FPGA芯片K7-325T架构一致,赛灵思公司在里面集成有高速串行收发模块GTX.ZYNQ设计架构使得它不仅拥有ASIC在能耗、性能和兼容性方面的优势,而且具有FPGA硬件可编程性的优点,便于底层FPGA参数拿到软核处理,便于操作.

系统采用一块ZYNQ核心板与两路K7通信,两路K7单独控制8路AD/DA信号.两块K7控制的AD/DA电路通过Z7下发控制字指令控制底层采集工作和波形发射工作同步进行.底层电路工作参数、状态和数据经Aurora协议上传至Z7,通过PC机操控.PCB加工经阻抗匹配,所有LVDS差分信号走线均经过蛇形线等长处理,保证了信号走线质量.

2.2 单路K7-325T

底层电路如图5所示,单路K7控制两块AD芯片LTC2175和4块DA芯片DAC3484.LTC2175为ADI公司的四通道14位A/D转换器,高位补0,配置为16位输出使用.DAC选用TI公司的四通道16位D/A转换器,采用两通道输出.单路K7控制8通道LVDS差分信号,AD/DA信号经过单端转差分放大器ADA4950输入输出,通过该器件可以在硬件调节输出信号共模偏置,若射频组件对偏置有要求可通过其实现.

图5 单路K7原理Fig.5 Single channel K7 principle

供电通过标准电源SS-33050设备提供5 V总电源.5 V电源过DC-DC稳压器件LTM4633配合LDO低压差线性稳压器件TPS74401RGW和LT1963 AEST输出为系统各部分供电.低压差稳压器件的合理使用,可降低电源纹波,确保信号中不叠加电源纹波噪声信号.

时钟由TI公司时钟发生器芯片LMK03806为各模块提供工作时钟,LMK03806器件是一款高性能、超低抖动、多速率时钟发生器,能够在频率高达2.6 GHz的条件下针对14路输出合成8个不同的频率.每个输出时钟可设定为LVDS、LVPECL或LVCMOS格式[9].能够以低成本的晶格或外部时钟生成多个时钟,可通过其配置AD采样时钟实现采样率可配置.LMK03806输入由标准20 M无源晶振提供,因项目需求设定AD,DA均采用100 M工作时钟.

2.3 程序设计

系统程序设计如图6所示,通过板载网口,基于LWIP协议在上位机控制台程序设置控制字指令,经Z7下发至底层数据采集系统,为底层各模块提供工作指示命令.底层系统采集射频组件信号,将采集数据完成多通道数据对齐,交织编码,打包后回传至Z7,存于Z7核心板内存DDR.

图6 程序框图Fig.6 Programs block diagram

控制字指令通过高速串行协议下发后,底层FPGA控制字模块解析上位机发送的控制字指令,为各模块提供指示命令,与其无关控制字指令则忽略.系统涉及控制字指令主要有对通道的控制指令,采集工作配置指令,发射波形配置指令及采集数据上传控制指令.

发射波形环节,DA模块接收到相应控制字指令,通过SPI协议方式配置DA内部数字振荡器频率产生本振信号与FPGA波形模块产生波形信号混频得发射波形,输出波形完成发射工作,发射波形模式有连续波形和预设波形两种[10].连续波形模式,若发送数据全0,为直流信号,NCO与其混频产生0频正弦信号[11].预设波形模式则主要用来设计产生用户特定需求波形.而用户所需波形信号的产生由标准模块算法CORDIC实现,该算法是一个比较全能的算法,其逐级迭代的原理,适用于硬件实现,产生所需波形信号.

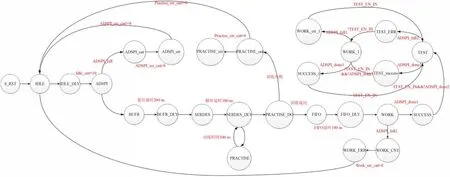

采集工作通过AD模块接收其控制字指令,在SPI协议下配置AD进行信号的采集工作,采集数据经打包缓存上传输出[12].AD工作状态机如图7所示,开机先对AD进行SPI配置各项工作参数,配置成功后延时200µs,通过不断采集配置的测试数据对AD各通道进行数据对齐训练,训练成功后进入工作模式.为保证采集工作进行一定时间后AD依然正常工作,后续工作状态通过不断测试,与正常模式交互工作.采集后的LVDS差分信号,经差分转单端,数据串转并,再经FIFO,匹配用户时钟域,完成采集工作[13].

图7 AD工作状态机Fig.7 AD working state machine

16路采集和发射工作的同步进行由两块K7控制,单块K7分别控制2块AD芯片和4块DA芯片负责8路信号的发射采集工作.多通道信号经AD采集后过通道FIFO对多路数据进行打包,数据在同一时钟下交织编码.打包工作为每次从选中通道取一个数据进行,以确保拿到同一时刻各通道数据,对齐数据.系统工作时钟与AD和DA工作时钟均为100 MHz.

多通道采集和发射工作可同步开启,通过AD采集脉冲和DA发射脉冲控制AD/DA有序工作[2].若多通道发射信号由于通道特性导致的信号不一致,程序预留有通道校准参数,可通过实测通道一致性情况,利用控制字固定通道各参数值,微调发射波形幅度,相位,延迟等参数,实现多通道一致性调节.在系统使用前,可依据实际硬件测试情况完成不同硬件的参数设置,保证多通道一致性.

系统通过上位机下发的系统同步脉冲信号产生各模块同步脉冲信号,如驻留清零脉冲,控制字生效脉冲,发射脉冲,本振封闭脉冲,采集脉冲和送数脉冲使系统有序工作[14].各脉冲起始位置,脉宽延展可由上位机配置.采集结果由回波送数脉冲控制,分别将系统通道噪声与信号数据上传,为射频组件性能分析提供数据支撑[15].

3 系统测试

3.1 硬件实物

系统设计硬件如图8所示,Z7通过连接器插座固定于数字PCB板,两路K7电路布局一致,16路AD/DA信号布线经过蛇形线等长处理,使得多通道中频信号传输时延尽可能一致.数据传输、通道一致性,同步发射信号等基于此数字板测试.

图8 硬件实物Fig.8 Physical hardware

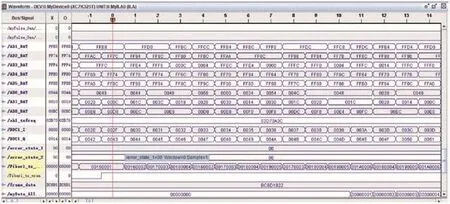

3.2 数据测试

为保证采集数据经Aurora协议准确上传数据至Z7,通过K7发送顺序数模拟打包数据.图9为K7发送顺序数经ISE仿真工具Chipscope实时抓取结果,图10为Z7端接收Aurora数据经Vivado仿真工具ILA抓取结果.由图可知,当数据有效信号rx_tvalid_i为1时接收到的数据rx_data_i刚好与ISE抓取上传前的数据Fiber_tx_data完全一致.实际数据上传的准确性通过连续抓取每一个上传的数据比对所得,经验证数据上传准确无误.

图9 ISE数据抓取Fig.9 ISE data scraping

图10 Vivado数据抓取Fig.10 Vivado data scraping

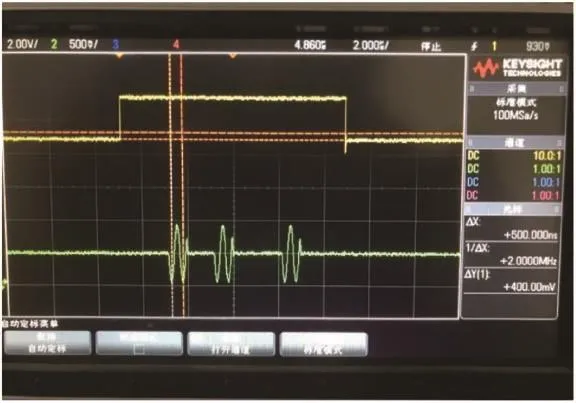

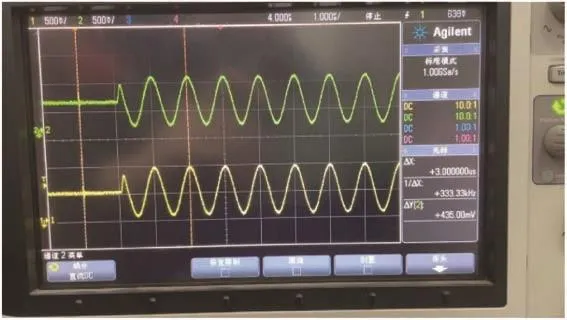

3.3 发射波形测试

用户发射波形如图11、12所示,发射波形可通过控制字配置底层参数由K7波形产生模块实现任意波形,如正弦波或方波.具体波形样式可通过上位机控制台程序修改参数获得,为便于对发射波形控制,系统设定随波控制信号,如图11上方波形所示.通过一个高展宽脉冲信号,对发射波形进行逻辑控制,可便于用户控制发射波形的输出.

图11 发射信号为正弦波Fig.11 Transmit signal sine wave

图12 发射信号为方波Fig.12 Transmit signal square wave

系统多通道发射信号同步测试,通过固定通道4第一路发射端口为基准,不断用示波器表笔测试比对其余15路发射信号得以验证.若实测发射波形延迟不一致,可通过程序打拍使多路发射信号同步工作,结果如图13所示.

图13 同步波形Fig.13 Synchronized waveform

3.4 一致性测试

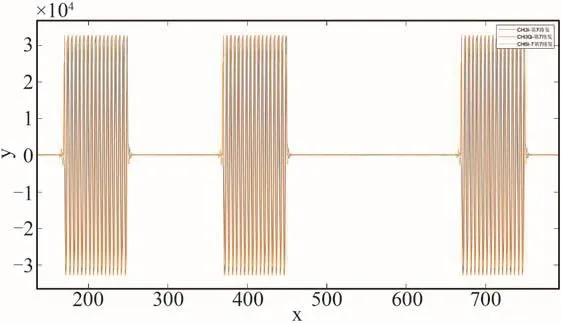

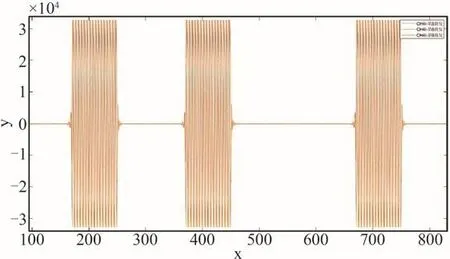

多通道一致性通过测试发射一致性和采集一致性得以验证[16].测试通过固定某一发射通道作基准,其余通道采用自闭环的方式与固定通道连接,通过其他路采集固定发射通道数据,将采集后的数据以TXT文本格式在MATLAB处理绘图,对比各个通道间数据,验证得系统通道采集基本一致.发射一致性通过固定采集通道,由同一采集通道采集不同发射通道数据验证,通过MATLAB绘图结果可知多通道一致性功能基本实现.

如图14所示,固定第7路发射波形,通过发射20 M正弦波分别采用两块FPGA控制的不同通道采集通道第7路发射的信号,最终由回采数据绘图验证得多通道发射一致性.

图14 发射一致性Fig.14 Launch consistency

如图15所示,固定通道第7路,即通道4第I路采集两块FPGA控制的不同通道发射的20 M正弦波信号,最终由回采数据绘图验证得通道采集一致性.

图15 采集一致性Fig.15 Sampling consistency

4 结语

本文设计基于Aurora的多通道高速可配置数据采集系统,实现采样率的灵活配置,多通道具有一致性,数据高速传输无误,系统各环节有序工作,系统底层参数可视化操作,可灵活修改参数便于测试任务的进行.系统通过采集射频信号的两正交分量,准确高速传输至上位机,便于用户直接通过射频信号基础的三个属性,瞬时频率、瞬时相位和瞬时幅度进行相关信号处理.