一种具有恒定转换速率的低压输出电路*

2022-04-27黄少卿陈海涛

顾 明,常 红,黄少卿,陈海涛

(1.中科芯集成电路有限公司,江苏无锡 214072;2.扬州大学物理科学与技术学院,江苏扬州 225600)

1 引言

随着集成电路工艺尺寸的缩小,芯片内部的时钟频率增大,数据传输速度也越来越快,为了保证数据传输的信号完整性,对信号上升时间和下降时间的要求也越来越严格[1-4]。以eUSB2.0(Embedded Universal Serial Bus 2.0)为例,在Low Speed和Full Speed模式下,输出波形的上升和下降时间必须保证在2~6 ns,意味着输出驱动电路转化速率(Slew Rate,SR)的设计应尽量与工艺、电源电压和温度(Process,Voltage and Temperature,PVT)弱相关[5-6]。工艺尺寸缩小的同时也导致芯片的工作电压越来越低,虽然目前CPU的工作电压已经低于1.2 V,但是众多通信协议里的标准电平远远高于CPU工作电压,比如USB2.0的标准电平为3.3 V,远远高于CPU电平。为了保证外界和CPU间的良好通讯,设计一种具有恒定转换速率的低电压输出电路就变得尤为重要。

目前对输出波形如何获得稳定的SR已有许多设计方案。其中一类方案是对输出阻抗进行PVT补偿,大体上分为模拟补偿[7]和数字补偿[7-8]两种方式。模拟补偿的基本工作原理就是通过采集与输出阻抗相关的信号,利用运放与设定的值进行比较,最后反馈调节输出MOS管Gate电压从而调节输出阻抗,以达到补偿效果。而数字补偿与模拟补偿类似,它将运放改成比较器,通过控制输出MOS的个数从而调节输出阻抗,来达到补偿效果。MALKOV等人对PVT补偿方案的研究做了系统总结[9]。第二类方案是引入反馈电容和恒流源,SHIN等人引入反馈电容后发现,反馈使得输出的SR参数只与电流大小和反馈电容有关,而与其他因素无关[10],从而大大减小了PVT和负载对SR的影响,提升了输出的稳定性。

本文在SHIN等人提出引入反馈电容电路的基础上做了进一步的改进,提出了一种在混合电压下工作并且能够提供稳定的SR输出波形的电路结构。

2 电路设计与分析

传统输出电路结构如图1所示,通过调控预驱动电路输出沿口的快慢,调节最后驱动电路输出的上升时间和下降时间以调节SR,也可以通过调控输出阻抗的大小来对SR进行调节。传统输出电路的优点是电路结构简单,缺点是对PVT和输出负载较为敏感,环境的变化会使上升时间和下降时间的变化范围大。

图1 传统输出电路

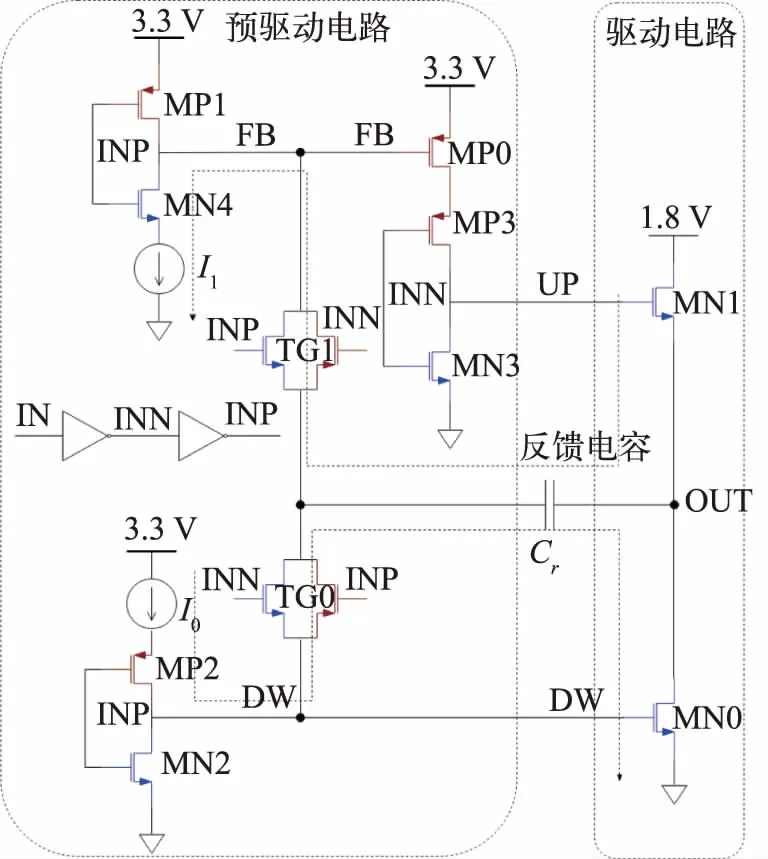

本文提出的一种新型输出电路结构如图2所示,电路包括预驱动电路、反馈电容和驱动电路3个部分。

图2 新型输出电路结构

当输入IN从高电平跳变到低电平时,IN经过两级反相器分别产生INN和INP信号,所以INN会从低电平跳变到高电平,INP会从高电平跳变到低电平。此时传输门TG0打开,TG1关闭。对于MN1的预驱动电路来说,MP3关闭,MN3打开,节点UP的电平等于GND,MN1关闭。对于MN0的预驱动电路来说,MP2打开,MN2关闭。电流源I0给MN0的栅极电容充电,节点DW的电平将从0 V开始上升。当DW达到MN0的开启电压VTN时,MN0开启并处于饱和区,流过MN0的电流增大,输出节点OUT电平开始下降,流过反馈电容的电流开始增加。当流过反馈电容的电流等于电流源I0的电流时,节点DW电压稳定在固定电平,使得MN0的灌电流等于电容的电流,此时输出节点OUT电压以恒定的转换速率下降。根据电容的电流-电压公式可得到:

随着输出节点OUT电平的下降,MN0将会进入线性区,此时节点DW电压脱离固定电平继续上升,反馈电容CR上的电流减小,输出OUT缓慢降低至GND。

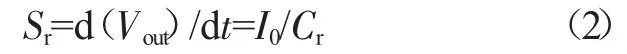

假设下降波形的过渡阶段可以忽略不记,输出的下降波形的转换速率Sr为:

设下降时间定义为输出波形从0.8Vcc下降到0.2 Vcc所需的时间Tf,可以推导出下降时间为:

由此可见,下降波形的转换速率Sr和下降时间Tf只与电流源的电流大小I0和反馈电容值Cr有关。

同理当输入IN从低电平跳变到高电平时,INN会从高电平跳变到低电平,INP会从低电平跳变到高电平。传输门TG0关闭,传输门TG1打开。对于MN0的预驱动电路来说,MP2关闭,MN2打开,节点DW的电平等于GND,所以MN0关闭。对于MN1的预驱动电路来说,MP3打开,MN3关闭,同时MP1关闭,MN4打开。在电流漏I1的作用下,节点FB的电平将从3.3 V开始下降。当FB下降到(3.3-VTP)时,MP0打开,UP电平开始上升,因为共漏极放大器中的输入和输出为同相信号,所以OUT电平跟随UP开始上升(在输出缓冲器中MN1和负载构成了共漏极放大器结构,而OUT和UP分别是共漏极放大器中的输出和输入信号),最终流过反馈电容的电流开始增加。当流过反馈电容的电流等于电流漏I1的电流时,FB将会保持在固定的电平,使得MP0相当于一个电流源对UP节点进行充电,因此节点UP的电平将以恒定的转换速率上升,而OUT跟随UP信号变化,从而OUT也将以恒定的转换速率上升。因此根据电容的电流-电压公式可得:

假设上升波形的过渡阶段可以忽略不记,上升波形的Sr为:

假设上升时间定义为输出波形从0.2Vcc上升到0.8Vcc所需的时间Tr,上升时间为:

由此可见,上升波形的转换速率Sr只与电流漏的电流大小I1和反馈电容值Cr有关。

通过上面对电路的分析发现,输出波形不管是上升波形还是下降波形,其转换速率仅仅与反馈电容和流过的电流有关,与其他因素无关,大大地减少了环境因素和负载变化对输出的影响。

3 仿真与讨论

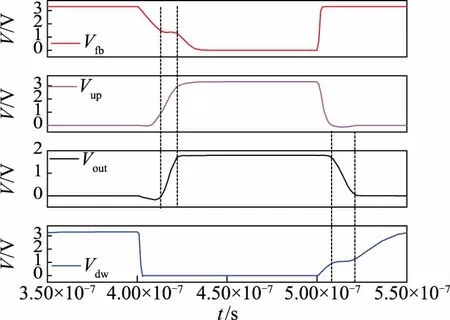

电路关键节点的Hspice仿真波形如图3所示,从图中发现当输出节点OUT处于下降沿口时,此时DW节点的电压处于相对稳定的值,MN0相当于电流漏,输出节点OUT从高电平向低电平线性下降,所以下降过程中其SR为固定值。当输出波形处于上升沿口时,FB节点的电压处于相对稳定的值,MP0相当于电流源,节点UP从低到高线性上升,输出节点OUT跟随着UP节点线性上升,所以上升过程中其SR也为固定值。由此可见仿真结果与电路分析相吻合。

图3 关键节点的Hspice仿真波形

负载从20 pF变化到80 pF的Hspice仿真波形如图4所示,从图中看到,当负载变化时,传统电路输出波形的上升时间和下降时间发生了明显变化,而本文提出的电路的上升时间和下降时间基本上不会随着负载的变化而变化。

图4 不同负载情况下的Hspice仿真波形

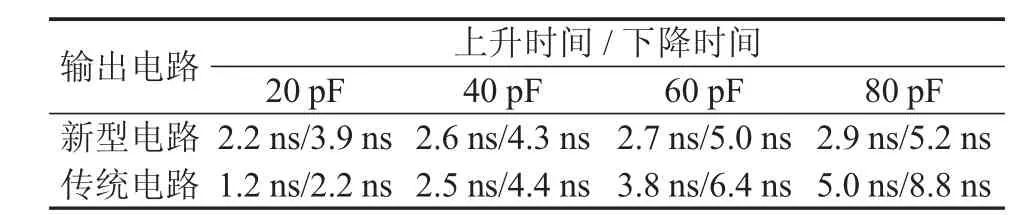

负载变化对输出上升/下降时间的影响如表1所示。负载从20 pF到80 pF变化时,传统电路的上升时间变化了3.8 ns,变化率为316.7%,而新型电路的上升时间仅变化了0.6 ns,变化率为27.3%。对于下降时间,传统电路变化了6.4 ns,变化率为290.9%,而新型电路的下降时间仅变化了1.3 ns,变化率为33.3%。

表1 不同负载情况下的上升时间/下降时间

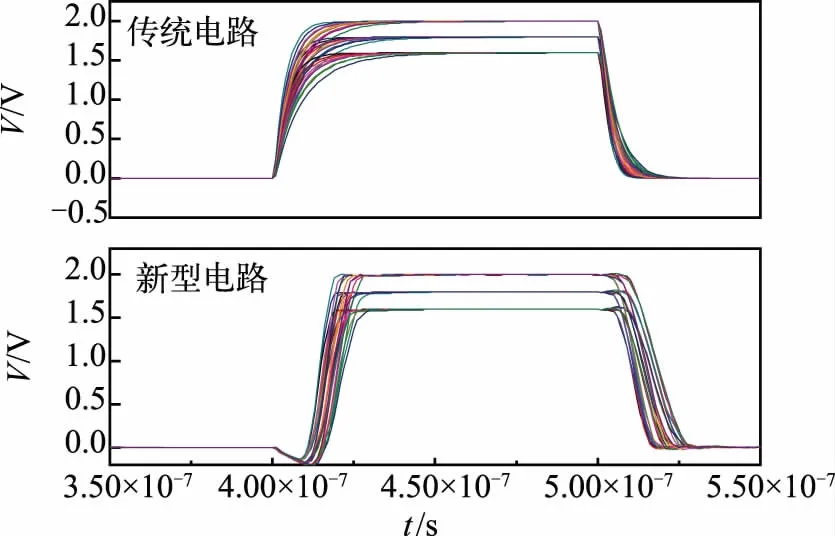

不同PVT的Hpice仿真波形如图5所示。从图中可见,不同PVT情况下,传统电路输出波形沿口的变化要远远大于新型电路输出波形沿口的变化。

图5 不同PVT情况下的Hspice仿真波形

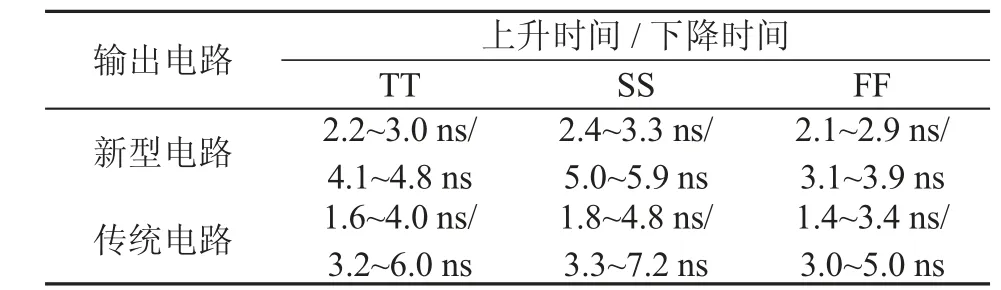

PVT变化对输出上升/下降时间的影响如表2所示。TT工艺角(NMOS-Typical Corner&PMOS-Typical Corner)下,传统电路的上升时间和下降时间分别变化了2.4 ns和2.8 ns,而新型电路的上升时间和下降时间仅变化了0.8 ns和0.7 ns。SS工艺角(NMOS-Slow Corner&PMOS-Slow Corner)下,传统电路的上升时间和下降时间分别变化了3.0 ns和3.9 ns,而新型电路的上升时间和下降时间仅变化了0.8 ns和0.7 ns。FF工艺角(NMOS-Fast Corner&PMOS-Fast Corner)下,传统电路的上升时间和下降时间分别变化了2.0 ns和2.0 ns,而新型电路的上升时间和下降时间仅变化了0.8 ns和0.8 ns。在不同PVT情况下,新型输出缓冲器的上升时间和下降时间变化率分别为54.5%和68.3%,而传统电路的上升时间和下降时间变化率分别为200%和131.3%,所以新型输出缓冲器在不同PVT条件下的性能优于传统电路。

表2 不同PVT情况下的上升时间/下降时间变化

4 结论

通过Hspice的仿真结果可以得到,本文所提出的输出缓冲器电路结构实现了3.3 V电平转1.8 V电平的低压输出。在不同的PVT情况下,输出的上升时间和下降时间仅仅变化了1.2 ns和2.8 ns;在不同负载的情况下,上升时间和下降时间仅仅变化了0.6 ns和1.3 ns。输出波形沿口的变化完全满足USB和eUSB接口的规格书内容要求,本文为接口驱动电路的设计提供了一个重要参考实例。