一种低成本短距无线收发机基带电路的设计

2022-04-12任兴福

任兴福,林 伟

(福州大学 物理与信息工程学院,福建 福州 350108)

0 引言

随着现代科技的不断发展,人们的生活正朝着信息化和智能化的方向不断迈进。在这种大时代背景下,物联网这一新兴产业应运而生[1]。物联网的应用涉及多个领域,其中大部分应用基于短距离无线通信技术实现[2]。许多应用场合往往不需要很高的通信速率,但在成本和功耗上却有着比较严格的要求。因此,满足物联网通信需求的低速率、低成本、低功耗的无线收发机也就越来越成为众多公司和学者研究的热点。

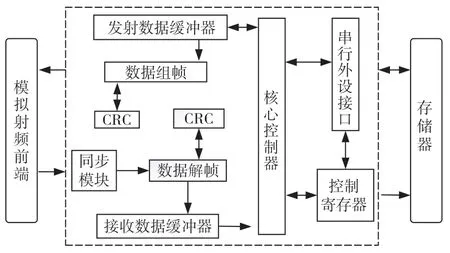

低功耗短距无线收发机可分为模拟射频前端、基带控制器以及存储器三部分[3]。其中,数字基带控制电路作为无线收发机的核心控制模块,首先需要对射频前端接收到的信号进行处理,其次根据接收到的指令对存储器进行读、写等操作,最后将处理完毕的数据回写到射频前端。数字基带控制器在在整个系统中起到控制中枢作用,不仅要完成对数据帧的处理,还要负责整个芯片工作状态的控制,其设计实现对无线收发芯片的整体性能有着十分重要的影响,因此对其进行研究具有深远的现实意义和较大的实用价值。鉴于此,本文设计了一种具有高速率、低功耗的基带控制电路,提出了一种灵活的数据帧结构格式,并对其一次性的收发操作进行了仿真验证。

1 基带处理电路整体框架

基带控制器是无线收发芯片的核心控制部分,主要分成组帧和解帧两大功能体系。

组帧电路的主要功能有:

(1)按照协议的要求,对存储器分别进行正确的读和写操作;

(2)对处理完的数据进行组帧操作,完成循环冗余校验码(Cyclic Redundancy Check,CRC)校验;

(3)回送给射频模拟前端进行调制发射。

解帧电路的主要功能有:

(1)与前一级的模拟射频前端良好对接,对解调后的信号进行位同步操作;

(2)对解调出来的数据进行解帧操作,依次解出数据帧包含的各字段信息并进行CRC 校验,确认数据传输和解调的正确性;

(3)依次将有效信息加载到数据缓冲器中,等待主机的读写。

基带处理电路的整体框架结构如图1 所示,虚线框中部分为基带处理电路,按照功能划分主要包括数据组帧模块、数据解帧模块、核心控制模块以及总线控制模块4 个部分。

图1 基带处理电路整体框架

2 主要模块设计

2.1 总线控制模块

总线控制模块采用经典的4 线串行外设接口(Serial Peripheral Interface,SPI)形式。SPI 总线是一种高速、全双工同步的通信总线,采用主从方式工作,共有4 个接口,分别为CSN、SCK、MOSI、MISO。外部微控制器根据串口协议,可以通过该接口对基带处理电路内的发射、接收数据缓冲器和配置寄存器进行读写操作。当CSN 信号为低时,通过MOSI 接口先输入8 bit 的控制命令,执行相应的读写操作,紧接着输入相应的数据信号。同时,可通过查看MISO 接口的返回值,判断数据缓冲器内的空、满状态等基带处理电路的内部情况。采用此总线电路命令解析的方式,相比于使用高频率系统时钟进行频繁的读写操作减少了时钟翻转的频率,相应地降低了系统的功耗。

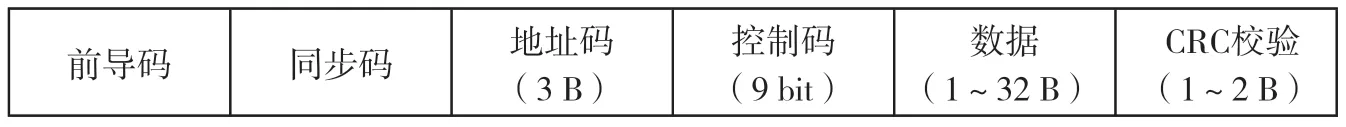

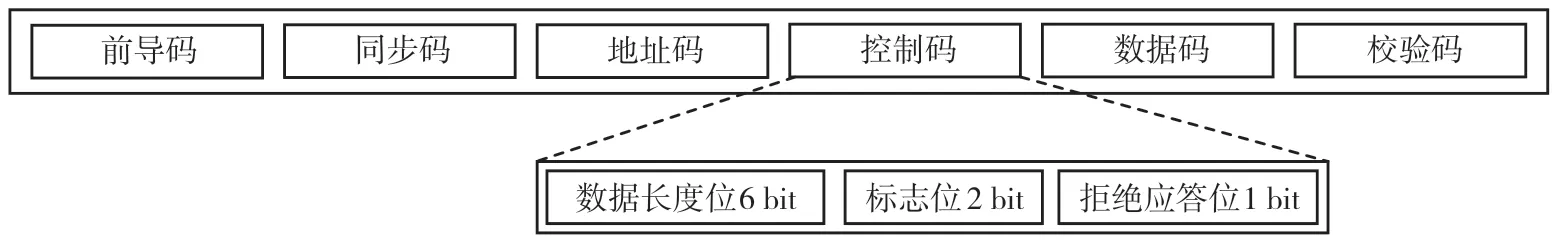

2.2 组帧模块

在通信系统中,收发双方需要按照一定的通信协议进行数据的传输。无论有线还是无线通信方式,确定一种合适的数据帧格式都十分重要,这将直接影响到数据收发的可靠性[4]。本设计提出一种灵活的数据帧结构,其组成部分包括前导码、同步码、地址码、控制码、有效数据位以及CRC 校验位,如图2所示。

图2 数据帧结构图

前导码由可变长度的“0”“1”交替码串组成。同步码选用7 位的巴克码“1110010”,接在前导码“0”“1”交替的码串之后,用于捕捉信息码元的起始信息。巴克码拥有尖锐单峰的自相关特性,误码率低,便于后续解帧电路的准确判决。控制字段如图3 所示,由3 部分构成,分别是数据长度位、标志位以及拒绝应答位。

图3 控制位组成

动态数据通信使得双方不必约定具体的数据长度,只要先读取控制字段中的数据长度位即可获知有效数据的长度。标志位由2 bit 数据组成,每次发射新数据包时,标志位都加1,即相邻的2 个数据包的标志位不同,用此方式判断是否为重复的数据包。校验码选择循环冗余校验(CRC)码,可以用来校验或者检测数据在传输完成后可能出现的错误。在同步码输出有效的同时,CRC编码模块开始工作,对串行输入的有效数据进行编码。本设计选用8 位和16 位两种CRC 码校验方式,由核心控制寄存器位命令控制。CRC-8 码生成的多项式为:

CRC-16 码生成的多项式为:

式中:x的最高幂次对应二进制数的最高位。

2.3 解帧模块

接收端从模拟射频前端接收到经解调的数据后,要对接收到的数据帧进行同步、解析判断等操作,主要分成位同步时钟提取电路、解码模块两部分。

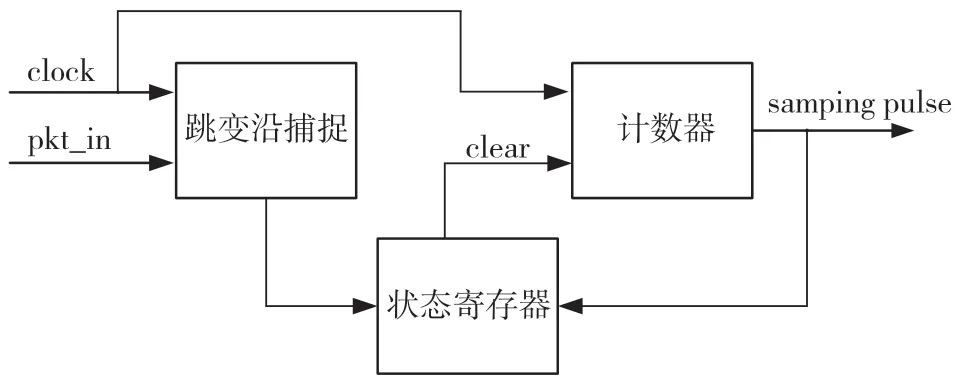

2.3.1 位同步时钟提取电路

本文设计采用一种结构相对简单、同步建立时间短的位同步时钟提取电路。利用系统时钟捕捉射频前端输入信号的跳变沿,以此调整产生新的基准相位。利用计数器输出一个采样位置在信号中间的采样脉冲信号[5]。同步器的结构如图4 所示。其中pkt_in 是输入系统的串行信号,clock 是频率为串行信号码元速率2N倍的时钟信号(其中N为大于2 的正整数),pulse_out 是位同步时钟。计数器分为模N-2 和2N两种计数模式,当跳变沿捕捉到数据跳变时,计数器进行模为N-2 的计数,并且产生采样脉冲;当数据边沿没有发生跳变时,每计数2N个时钟周期后产生一个采样脉冲。通过这种方式可以调整产生新的基准相位,并且在信号中间输出一个采样脉冲信号。后面模块使用该同步器产生的采样脉冲作为时钟,相比于使用高频系统时钟降低了功耗。

图4 同步器结构

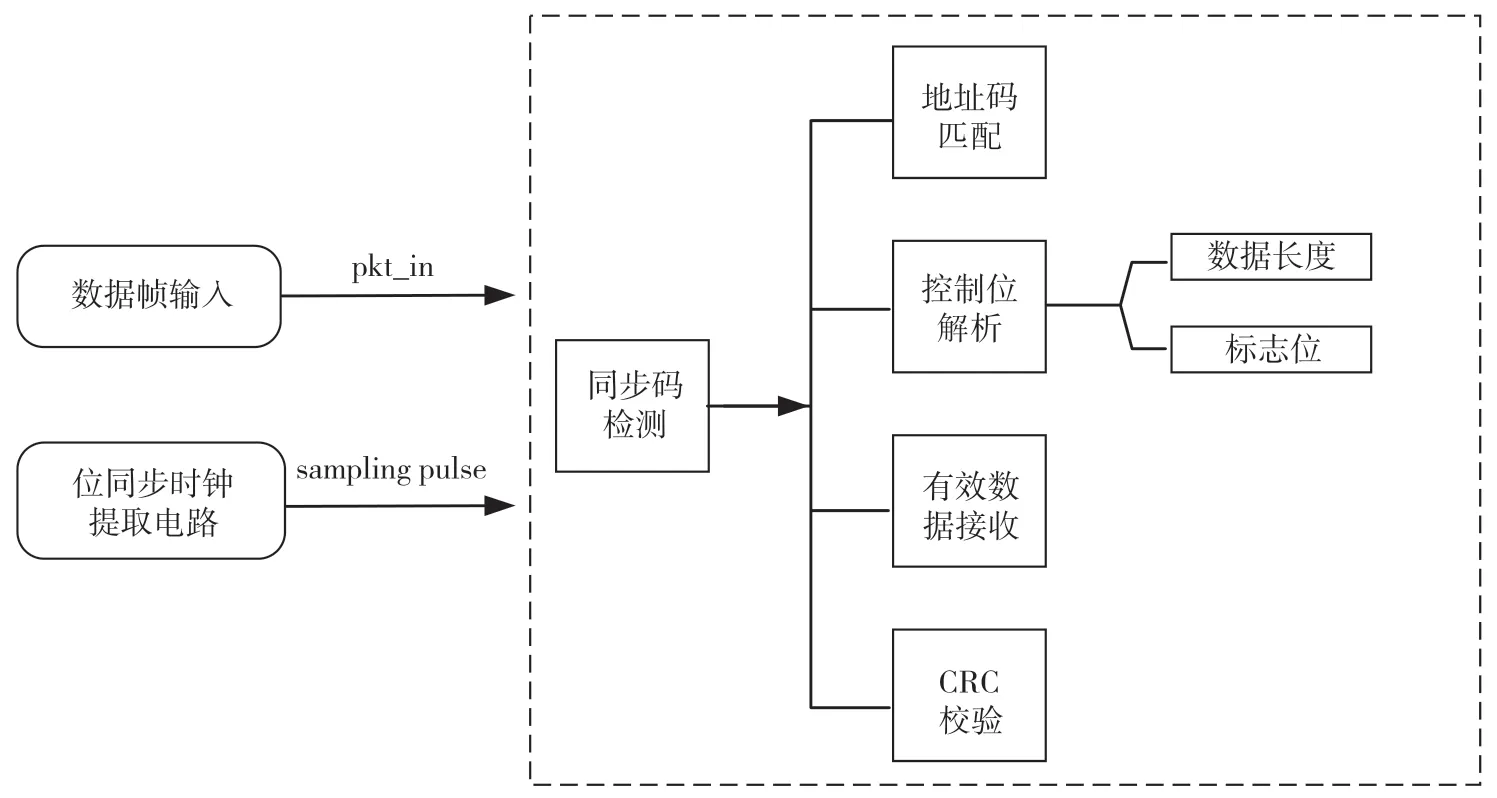

2.3.2 解码模块

解码模块从模拟射频前端接收到数据帧,按照通信协议,对接收到的数据帧进行类似流水线方式的解帧操作。解帧操作如图5 所示,先进行同步码的检测,接着同时进行地址码匹配、控制位解析、CRC 解码校验等操作。其中,对控制位的解析操作包括对数据长度位和标志位的解析操作,提前获知数据位的字节长度,有助于微控制单元(Micro Controller Unit,MCU)在较少的时钟周期内完成对数据的读取,可以极大地降低功耗。若上述过程中任一环节出现错误﹐则立刻停止后续操作,并重新开始对下一数据包进行同步检测。这种方法可以极大地提高数据处理的效率。

图5 解帧模块框图

2.4 核心控制模块

核心控制模块是基带处理电路的控制中心,控制整体电路在不同的工作状态间进行切换,以协调各功能模块间的工作。整体电路可以分成掉电、待机﹑接收准备、接收、发射准备、发射6 个工作状态。在不同的工作模式下各功能模块的工作状态存在差异,不需要运行的模块将被关闭,这样通过不同工作模式的设置可实现系统的功耗管理,以达到有效降低功耗的目的。核心处理模块主要通过状态机进行设计实现,如整体电路处于待机状态时,为方便与外部MCU 通信,只需SPI 模块工作即可,关闭其余模块,这样能显著减小电路的峰值功耗。

3 仿真与验证

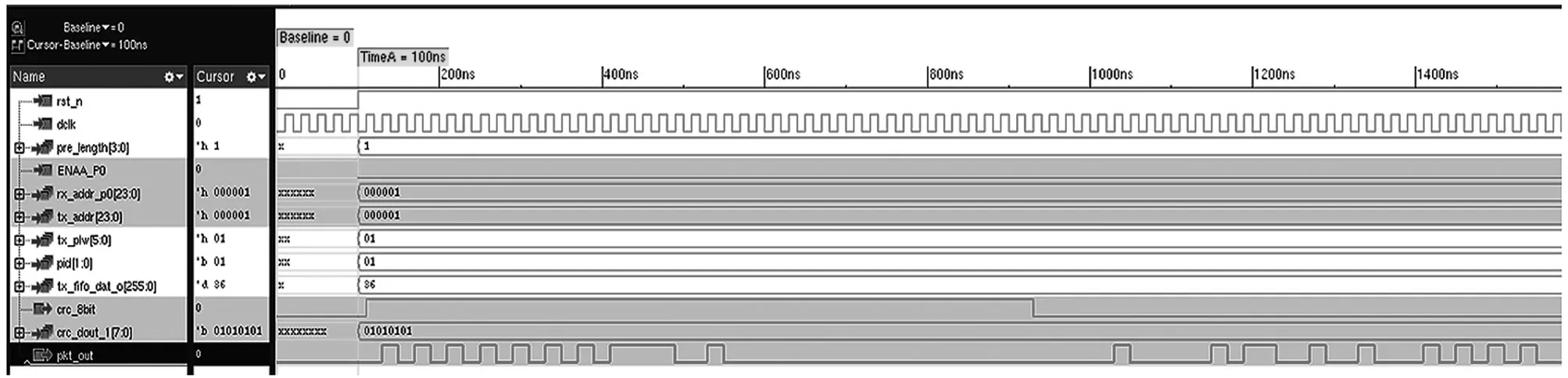

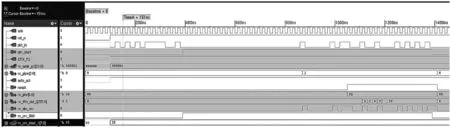

本设计用Verilog HDL 语言编程实现,并在Cadence 公司发布的INCISIV 软件下实现,运用其中的NC-Verilog 工具实现仿真验证。发射验证如图6 所示,完成了一次发射的组帧验证,前导码由“0”“1”交替的字符串组成,后接巴克码“1110010”,之后是地址码,有效数据为256’d36,数据长度为1 Byte,标志位pid 为2’d01,CRC 校验选用CRC-8。此时输出为pkt_out,数据帧按照之前的参数信息完成了组帧发射。接收验证如图7 所示,完成了一次接收的解帧验证,检验到正确的巴克码时产生同步信号pkt_start,电路依次完成对地址码、数据长度、有效数据的接收操作。

图6 发射验证

图7 接收验证

4 结语

本文设计了一种具有高速率、低功耗的基带控制电路,同时提出了一种灵活的数据帧结构,依照设计的数据帧结构对基带控制电路分别进行了组帧发射和解帧接收的仿真验证。结果显示,设计的基带控制电路可以基于提出的数据帧结构很好地完成发射、接收操作,对低成本短距无线收发机的实现有着重要意义。