基于STM32F407的FPGA 动态加载设计*

2022-04-11赖川,邓蕾,张显

赖 川,邓 蕾,张 显

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引言

因现代民用电子装备更新换代快、复杂度高,故民用电子测试系统面临着测试种类多、多技术高交叉性以及技术更新迭代加快等新挑战。传统的装备测试系统很难兼顾高效率测试和低成本测试,不具备能够根据被测装备测试需求的变化而进行调整的灵活性,且可扩展性差[1]。

近年来,现场可编程门阵列(Field-Programmable Gate Array,FPGA)行业发展快速,门数量的增加和生产工艺的进步使FPGA 走到了技术的前沿,现如今在硬件设计中FPGA 起到了至关重要的作用。类型多样、功能强大的FPGA 器件、丰富的知识产权(Intellectual Property,IP)以及友好的设计开发工具给硬件设计提供了非常大的便利[2],在各种民用电子测试系统中得到了广泛的应用,而如何对测试系统中的FPGA 程序实现快速更换,从而满足被测装备的多样化测试需求,成为新的挑战。

为实现低成本的FPGA 程序更换,本文设计了一套基于STM32F407的FPGA 动态加载系统,该系统采用32 位闪存微控制器STM32F407 和FPGA 芯片XC7K325T。本文详细阐述了系统的软硬件实现,最后通过系统调试和测试分析论证了该系统的可行性、有效性,并且证明了该系统具有很高的工程应用价值。

1 系统总体方案

该系统主要由32 位闪存微控制器微控制单元(Microcontroller Unit,MCU)、FPGA 芯片、以太网物理层接口(Physical Layer,PHY)芯片、模拟开关切换芯片、SPI Flash 芯片和PC 机组成。以太网PHY 芯片与PC 机之间通过以太网接口连接,以太网PHY 芯片与MCU 之间通过简化媒体独立接口(Reduced Media Independent Interface,RMII)方式直接连接,MCU 可直接通过调用10 Mbit/s 或100 Mbit/s的以太网介质访问控制层(Media Access Control,MAC)控制器与PC 机之间进行网络通信。PC 机上安装上位机加载软件,通过以太网与MCU进行数据通信。

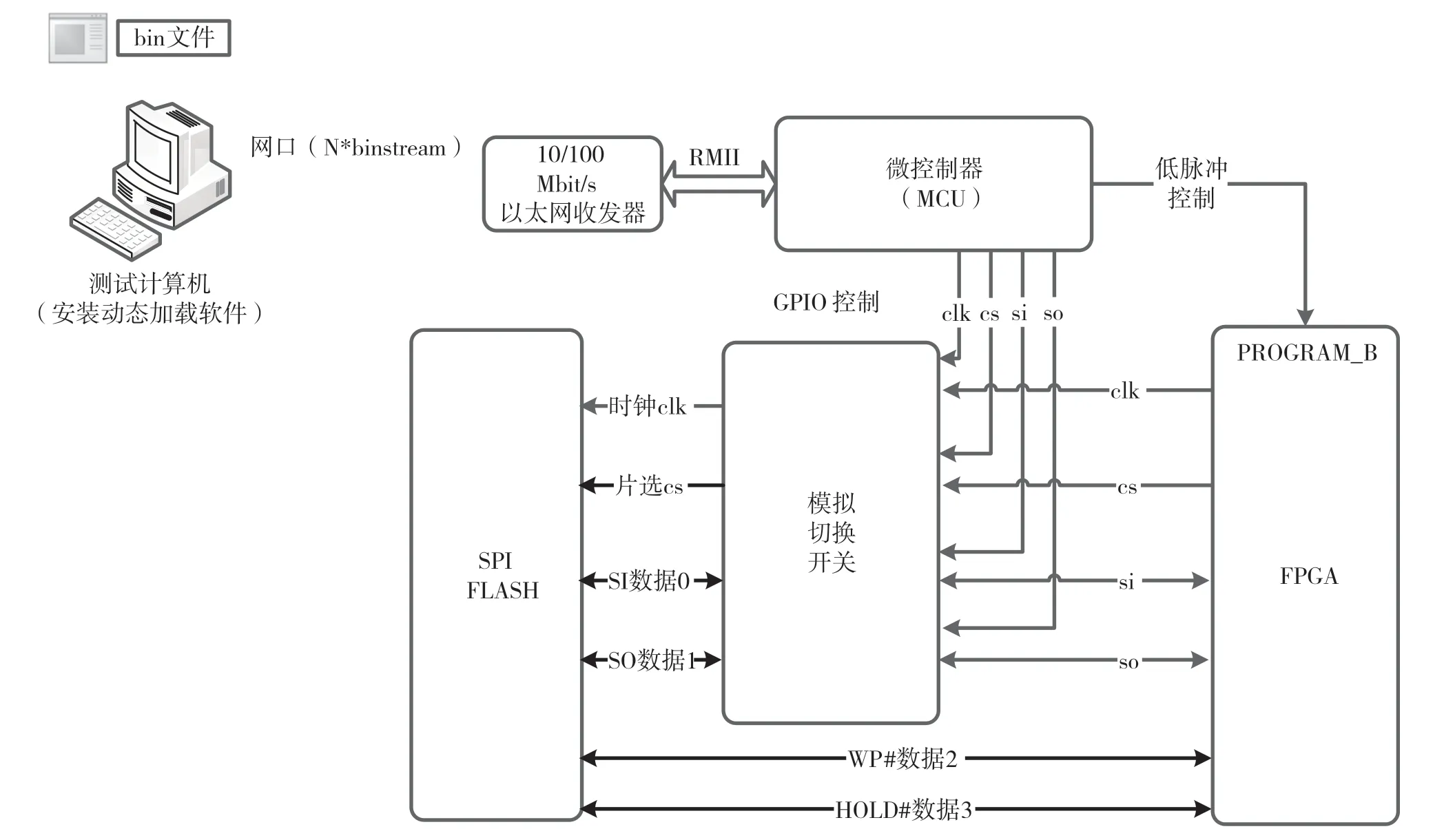

为了验证系统的可行性和有效性,系统的测试方案是在确保硬件连接正常的前提下,在上位机加载软件上通过以太网发送不同的二进制(binary,bin)文件,MCU 将接收到的bin 文件按照相应的地址写入SPI Flash 中,写入完毕后,再产生低脉冲信号送入FPGA 芯片的PROGRAM_B 管脚上,实现其硬复位,并观察FPGA 程序是否能够正常启动,基于这一测试来分析系统设计的有效性。基于STM32F407的FPGA 动态加载的系统总体设计如图1 所示。

图1 系统设计

2 系统硬件设计

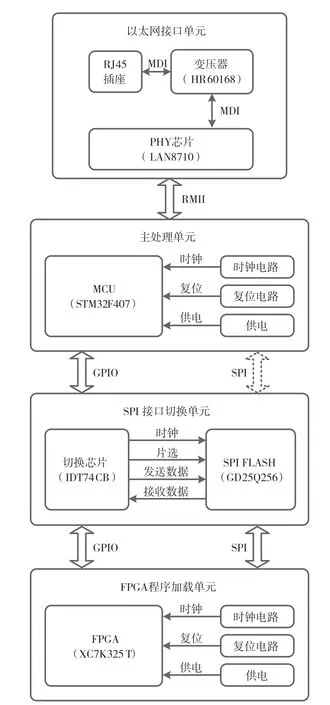

本文设计的动态加载系统基于STM32F407 为主处理单元,完成对FPGA 程序加载的控制。动态加载系统主要由主处理单元、以太网接口单元、SPI 接口切换单元和FPGA 程序加载单元组成,其硬件组成如图2 所示。

图2 系统硬件组成

以太网接口单元中变压器与PHY 芯片之间以介质相关接口(Medium Dependent Interface,MDI)进行连接,将上位机发送的网络数据通过变压器和PHY 芯片转换成简化媒体独立接口(Reduced Media Independent Interface,RMII)接入MCU 主处理芯片,通过MCU 程序处理实现以太网数据的收发。主处理单元通过MCU 芯片的SPI 接口和通用输入/输出端口(General Purpose Input Output,GPIO)完成对切换芯片的控制和SPI Flash的读写操作;SPI Flash写入完毕后,切换SPI 接口管脚到FPGA,并控制FPGA 重新加载程序。

2.1 主处理单元

主处理单元是动态加载系统的核心部分,负责网络数据收发、bin 文件传输协议的解析和封装、复用管脚的配置、SPI 接口切换和FPGA 程序加载状态的控制。

主处理单元选用意法半导体公司的单片机最小系统STM32F407,该器件支持通过以太网收发数据,具有数据传输速率快、效率高,集成度高、配置灵活、可扩展等特点,能适应各种不同客户需求,工作时钟可高达168 MHz,尤其是内部集成了高精度时钟源及电压调节功能,以及硬件实现增强型SPI 串行接口,因此设计时可直接使用[3];该器件主要包括供电电路、串行调试(Serial Wire Debug,SWD)电路、时钟电路和复位电路的设计。系统供电电压设为3.3 V,外部晶振选用8 MHz 和32.768 kHz。该芯片能较好地满足整体的技术指标要求,并具备较强的升级扩展性。其主要特性如下:

(1)集成了专用于浮点运算的处理器(Float Point Unit,FPU)和数字信号处理(Digital Signal Processing,DSP)指令,并具有192 KB的内部静态随机存取存储器(Static Random-Access Memory,SRAM)和1 024 KB的Flash;

(2)包含2 个32 位定时器、2 个直接存储器访问(Direct Memory Access,DMA)控制器、3 个串行外设接口(Serial Peripheral Interface,SPI)、3个集成电路总线(Inter-Integrated Circuit,IIC)、6 个串口、2 个控制器局域网络(Controller Area Network,CAN)、3 个12 位模拟数字转换器(Analog To Digital Converter,ADC)、2 个12 位数字模拟转换器(Digital to Analog Converter,DAC)、1 个安全数字输入输出卡(Secure Digital Input and Output,SDIO)接口、1 个可变静态存储控制器(Flexible Static Memory Controller,FSMC)接口、1个数字摄像头接口(Digital camera interface,DCMI)以及112 个通用输入和输出(Input/Output,IO)接口等[4];

(3)它还带有一个10/100 Mbit/s的以太网MAC 控制器,支持以太网通信[5]。

2.2 以太网接口单元

以太网接口单元用于上位机与STM32F407 芯片之间以太网数据交互物理层通道的建立。本设计选用SMSC 公司的LAN8710A 作为以太网物理层的交互芯片。LAN8710A 是一款低功耗的10/100 Mbit/s物理层收发器,全面支持IEEE802.3—2005《物理层和数据链路层的有线以太网》标准,此外,可支持通过RMII 接口与以太网MAC 进行通信。在本设计中与STM32F407的RMII 总线连接,实现100 Mbit/s 网络全双工通信。LAN8710A的外围接口电路如图3 所示。

图3 LAN8710A 外围接口电路

PHY 芯片LAN8710A 右侧为变压器和RJ45 插座,主处理单元调用内部的MAC 控制器通过RMII接口完成与PHY 芯片的底层通信;XTAL1 为PHY芯片工作时钟,采用50 MHz的有源晶振;该50 MHz时钟与MCU 芯片的RMII 接口为同一时钟源;PHY芯片地址配置为000,与MCU 程序中的PHY 地址保持一致;LAN8710A 采用2 位位宽收发数据,采样时钟为50 MHz,完成100 MHz 速率的适配。

2.3 SPI 接口切换单元

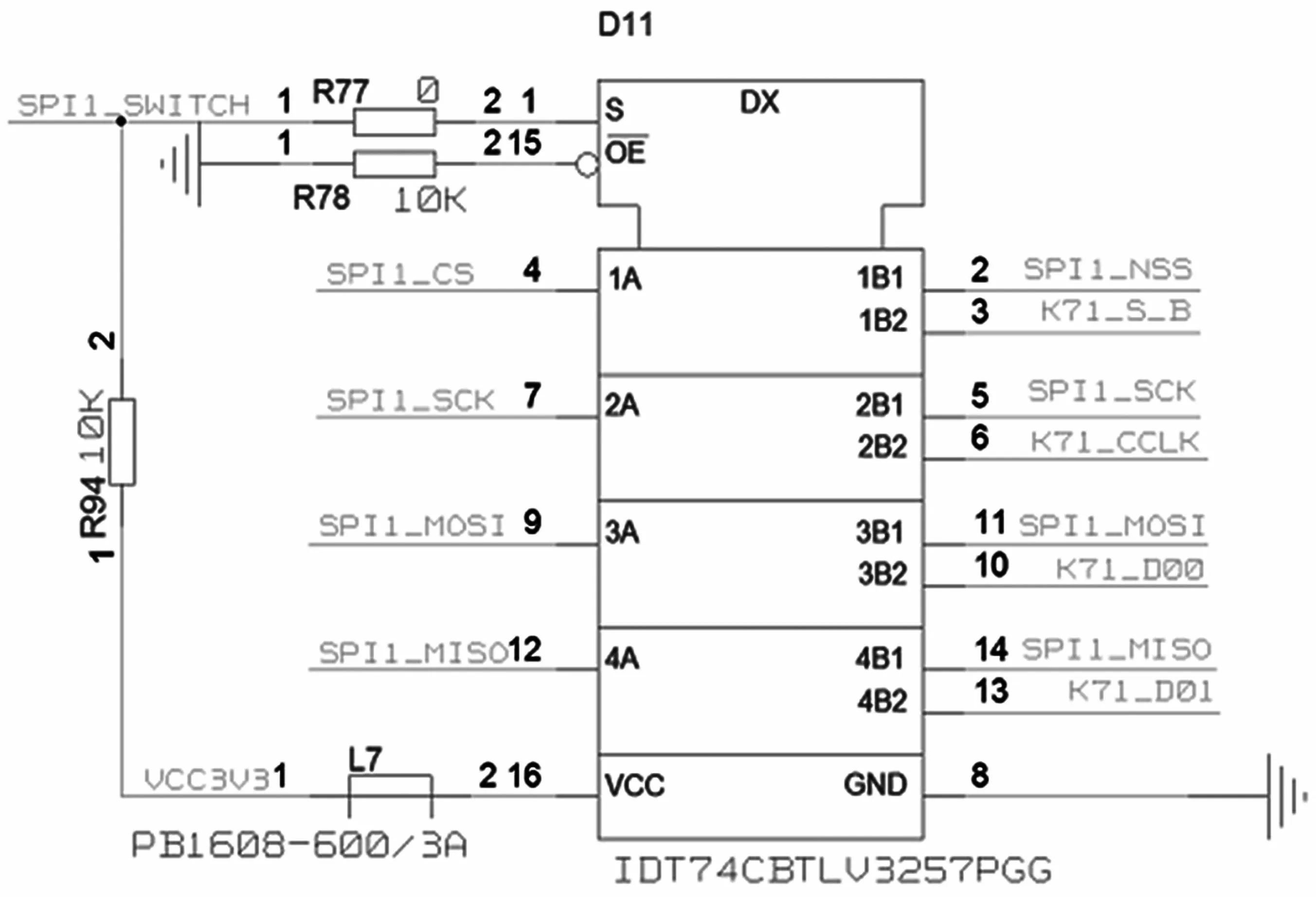

SPI 接口切换单元由主处理单元的MCU 芯片通过GPIO 管脚控制模拟开关切换芯片IDT74CBTLV3257PGG的状态,使SPI Flash 芯 片GD25Q256DYIG 分别与STM32F407的SPI接口、FPGA的程序加载接口连接。SPI 接口切换单元的连接如图4 所示。

图4 SPI 接口切换单元连接

SPI 接口切换单元默认状态为SPI 接口与FPGA的程序加载接口连接,是为了保证FPGA 上电第一时间就能进行程序的加载,此外,只有当主处理单元在接收到上位机动态加载软件的网络数据包后,并符合通信协议要求,才将SPI Flash的接口切换过来,然后调用其内部的SPI 接口完成文件的读写操作。当文件写入完毕后,主处理单元会将SPI 接口切换到FPGA,使其能够正常工作。

2.4 FPGA 程序加载单元

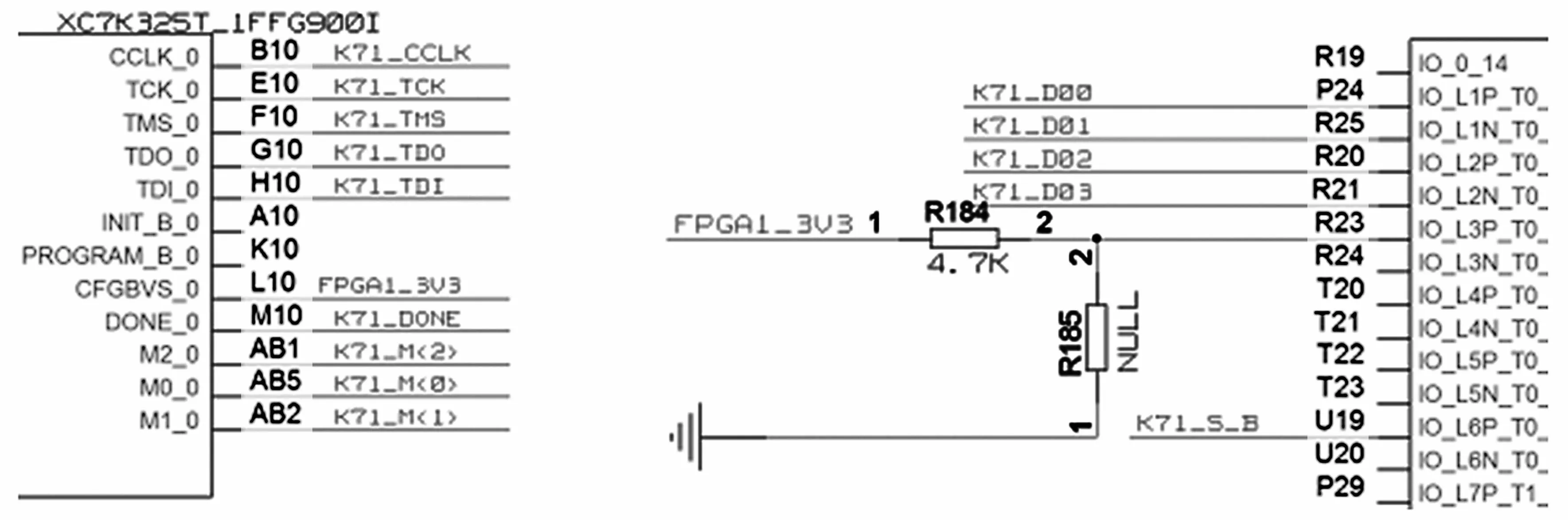

FPGA 程序加载单元选用Xilinx 公司7 系列芯片XC7K325T,它拥有丰富的资源,包含478 000个逻辑单元、34 MB的块随机存储器(Random Access Memory,RAM)以及500 用户的IO 口,最大工作频率为640 MHz;其程序加载如图5 所示。

图5 FPGA 程序加载

FPGA 芯片的加载模式配置为001,即MASTER SPI 主动读取模式。上电后,由FPGA 配置BANK主动从SPI FLAHS 中读取相应的程序,进行程序的加载。本文设计的读取方式为SPI X4 模式,使用到片选、时钟和4 位数据线。

3 系统软件设计

动态加载系统的软件包括上位机动态加载软件(安装运行于Windows 操作系统),还包括运行于STM32F407 芯片内的MCU 嵌入式软件。

3.1 上位机动态加载软件

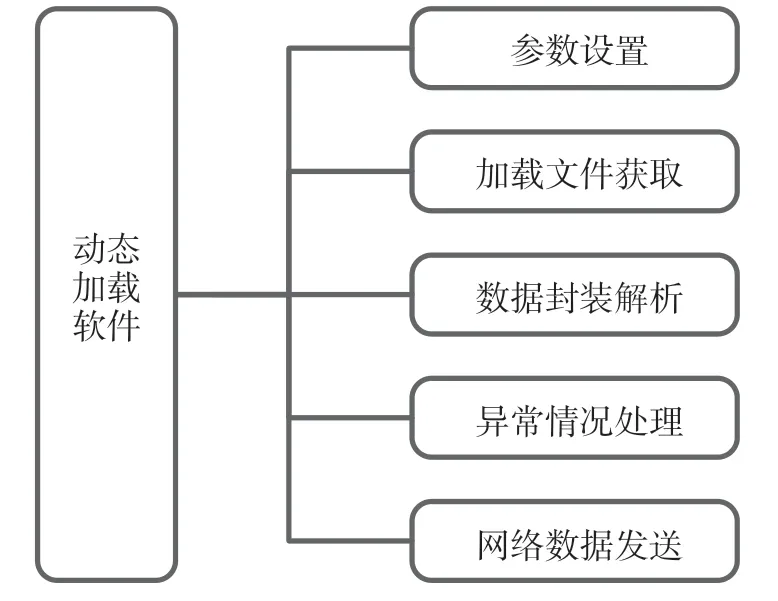

上位机动态加载软件采用模块化分层的框架体系。各层间耦合性较小,便于独立开发和验证测试。上位机加载软件基于Visual Studio 2015 平台进行开发设计,按功能划分为参数设置模块、加载文件获取模块、数据封装解析模块、异常情况处理模块和网络数据发送模块等。具体的模块划分如图6所示。

图6 测试环境

3.1.1 参数设置模块

参数设置模块主要用于设置底层硬件的IP 地址、源端端口号和目的端端口号,设置的参数用于用户数据报协议(User Datagram Protocol,UDP)报文网络数据发送,IP 地址、源目的端口号可根据实际情况进行相应的修改,如图7 所示。

图7 参数设置界面

3.1.2 加载文件获取模块

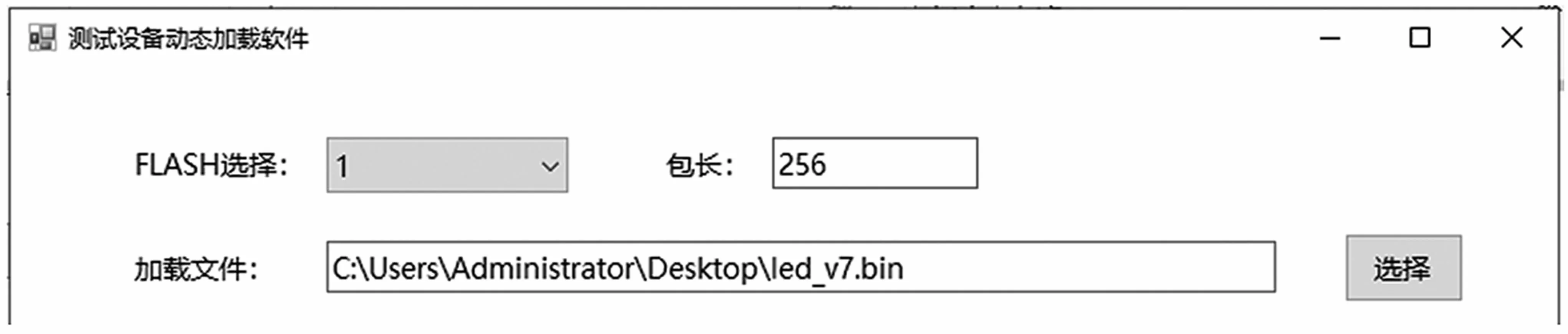

加载文件获取模块主要完成bin 文件的载入,包长设置确定每一包数据的长度,如图8 所示。

图8 加载文件获取界面

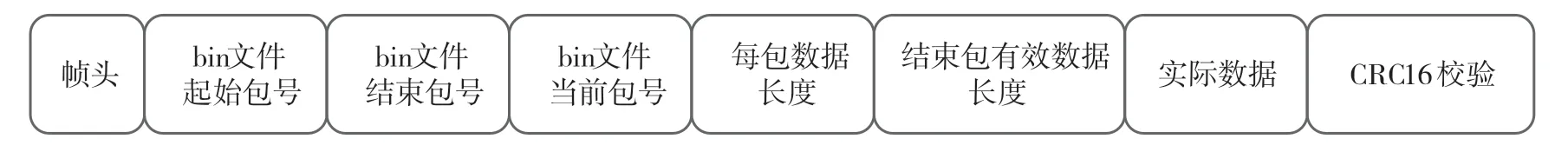

3.1.3 数据封装解析模块

数据封装解析模块是软件设计的关键和重点,按照数据传输协议帧格式,对获取的bin 文件进行分包处理,与加载文件获取界面上设置的包长共同计算出结束包号,在数据传输过程中,实时记录当前包号,进行封装和处理,再运用CRC16 校验保证发送数据的正确性。数据传输协议帧格式如图9 所示。

图9 数据传输协议帧格式

数据封装解析模块接收到底层硬件返回的数据后,先判定其帧头和CRC16 校验是否正确,正确即代表数据有效,之后按照数据传输协议进行数据解析,解析正确则给出正确应答,解析错误则给出错误应答。

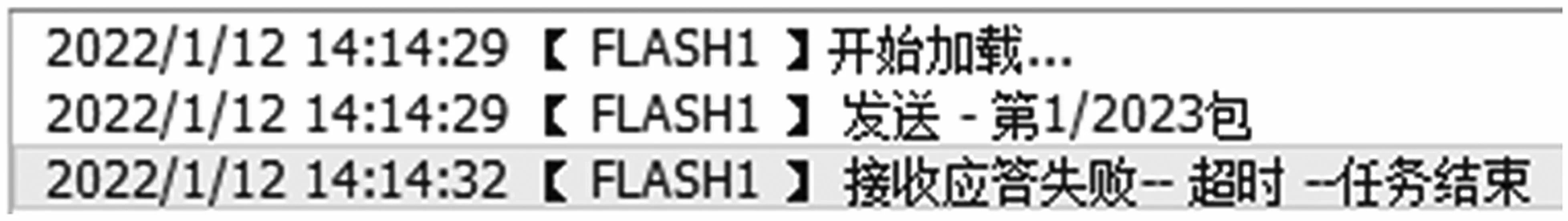

3.1.4 异常情况处理模块

异常情况处理模块对接收到的底层硬件网络数据包进行解析,判断其是否为有效数据。如果为有效数据,则继续按照数据传输协议格式封包发送数据;如果为无效数据,则按协议格式重发当前数据包,若重传3 次后仍然收到无效数据,则表示接收应答失败,此次加载任务结束。超时应答如图10所示。

图10 超时应答

3.1.5 网络数据发送

网络数据发送模块调用Visual Studio 2015 自带的UDP 控件,将IP 地址、源/目的端口和数据传输净荷按照UDP 协议报文格式发送给底层硬件进行处理。

3.2 MCU 嵌入式软件

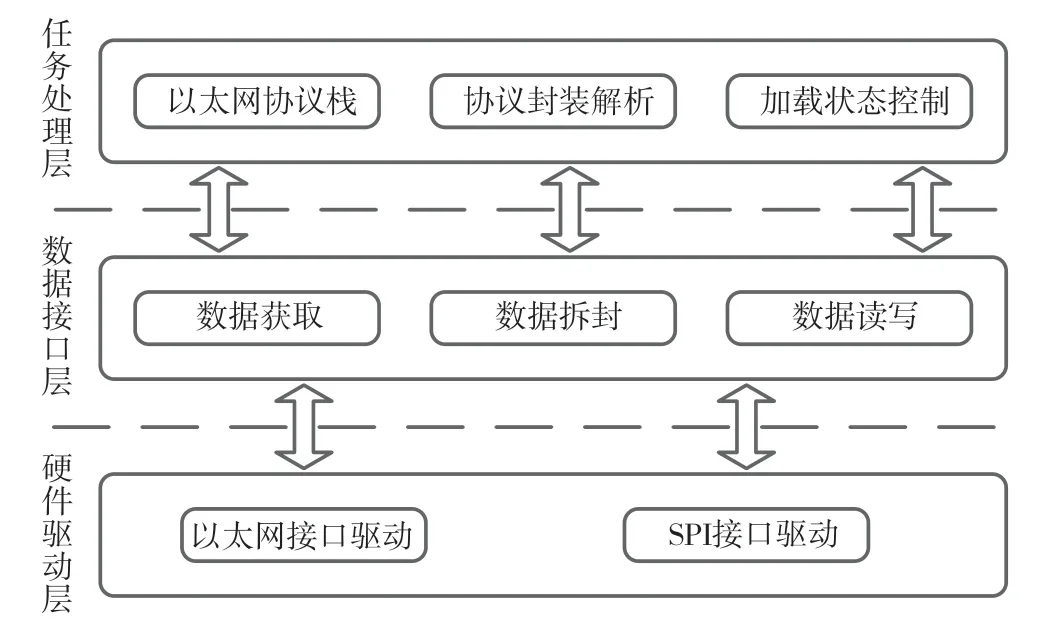

MCU 嵌入式软件的开发基于Keil5 平台,设计主要分为任务处理层、数据接口层和硬件驱动层3个部分,嵌入式软件架构如图11 所示。任务处理层主要完成以太网协议栈的调用、协议封装解析和加载状态控制,是软件设计的关键和重点。数据接口层主要处理bin 文件数据包的获取、拆封和读写。硬件驱动层主要完成各类硬件接口的驱动实现,主要包含以太网接口和SPI 接口。

图11 嵌入式软件架构

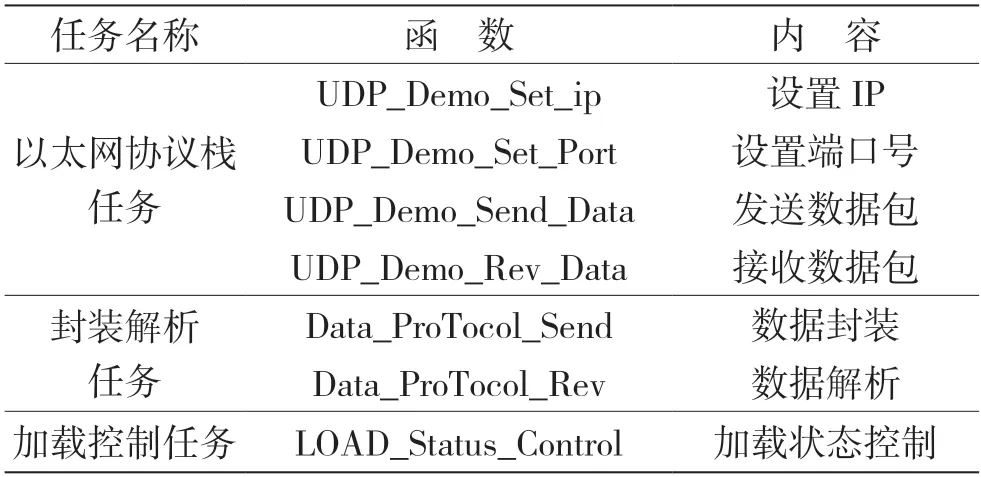

3.2.1 任务处理层

任务处理层作为嵌入式软件的核心部分,通过数据接口层与硬件驱动层完成数据交互。不同的任务程序实现不同的功能,每个任务程序之间相互协作。嵌入式软件的任务列表,如表1 所示。

表1 嵌入式软件任务

以太网协议栈任务主要完成以太网UDP 协议的解析和封装。协议封装解析任务对传输数据帧净荷部分进行解析和封装,加载状态控制任务监控网络数据包的接收状态,并根据读写SPI Flash的状态来进行相应的控制。

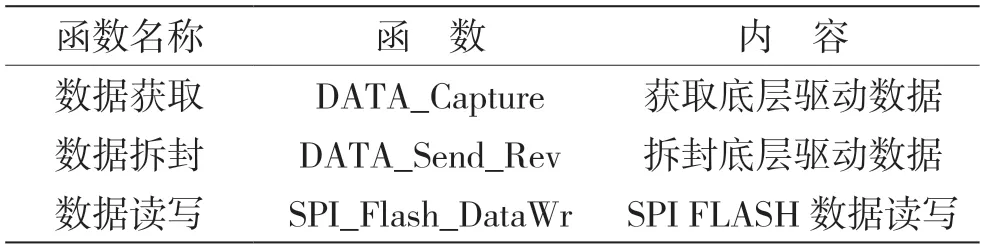

3.2.2 数据接口层

数据接口层是对硬件驱动层获取的数据进行相应的拆封,并传递给任务处理层内的相关任务。数据接口层的函数如表2 所示。

表2 数据接口层函数

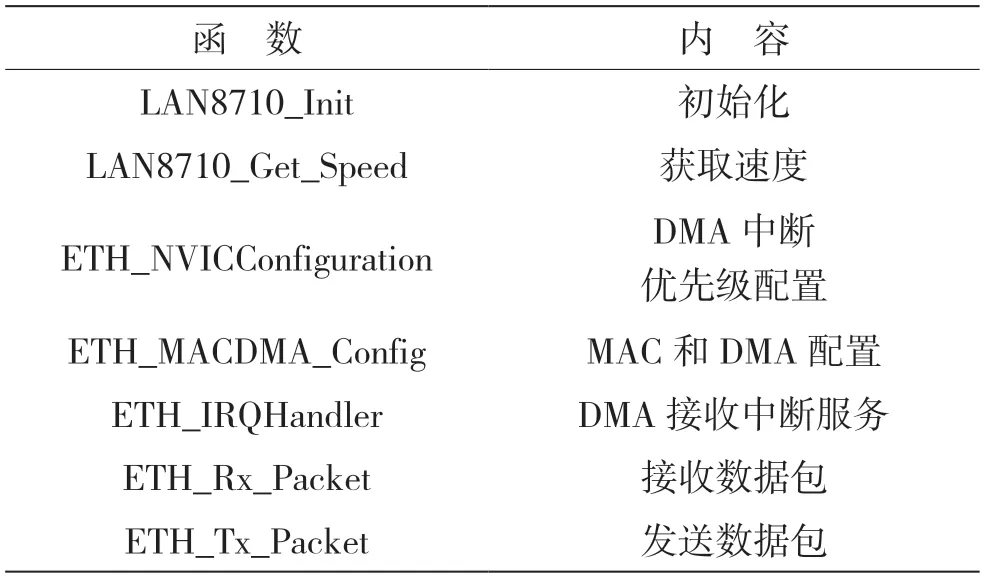

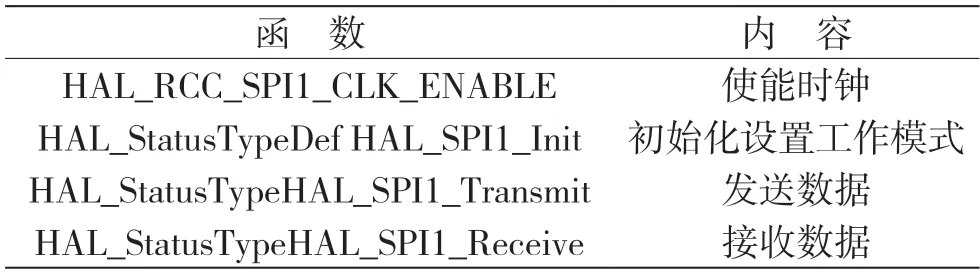

3.2.3 硬件驱动层

硬件驱动层主要与底层硬件建立数据交互通道,包括初始化、中断操作、参数配置和数据传输。在本设计中,包括以太网接口驱动和SPI 接口驱动。其中以太网驱动函数如表3 所示,SPI 驱动函数如表4 所示。

表3 以太网驱动函数

表4 SPI 驱动函数

4 系统测试与分析

完成动态加载系统软硬件设计后,需要对本系统的硬件和软件进行调试。系统上电前,检查硬件的各个部分是否有短路,连接是否正确,确保硬件连接正确无误的情况下,通过Keil5 和Visual Studio2015 开发平台对系统软件进行测试。软件测试前,MCU 嵌入式软件在Keil5 上完成编译,编译成功后通过SLINK 仿真器下载到单片机STM32F407内,然后在Visual Studio 2015 上完成动态加载软件的编译,确保编译正确后,运行动态加载软件程序,查看单片机接收和发送信号是否正常,并观察动态加载软件的运行是否正常。

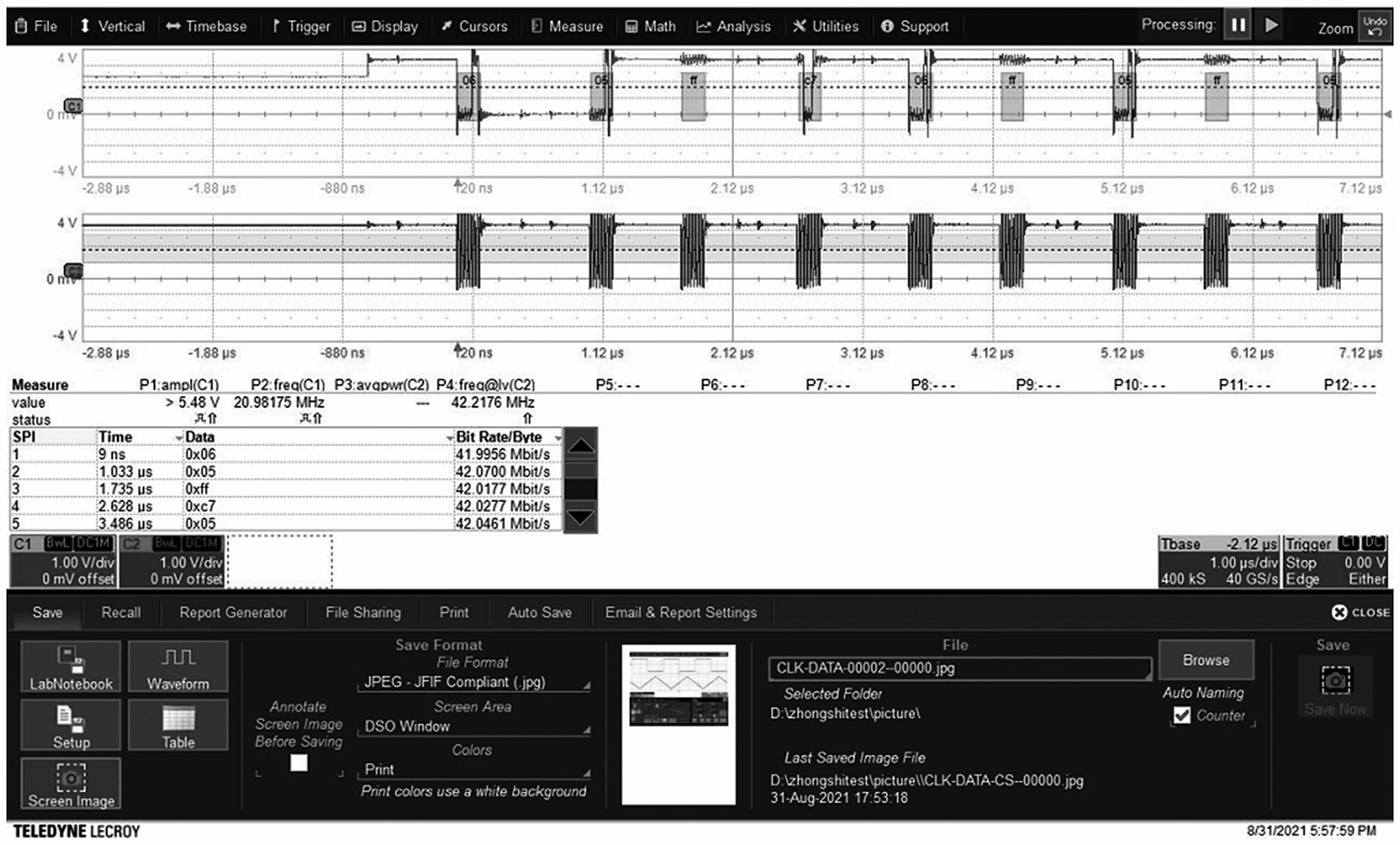

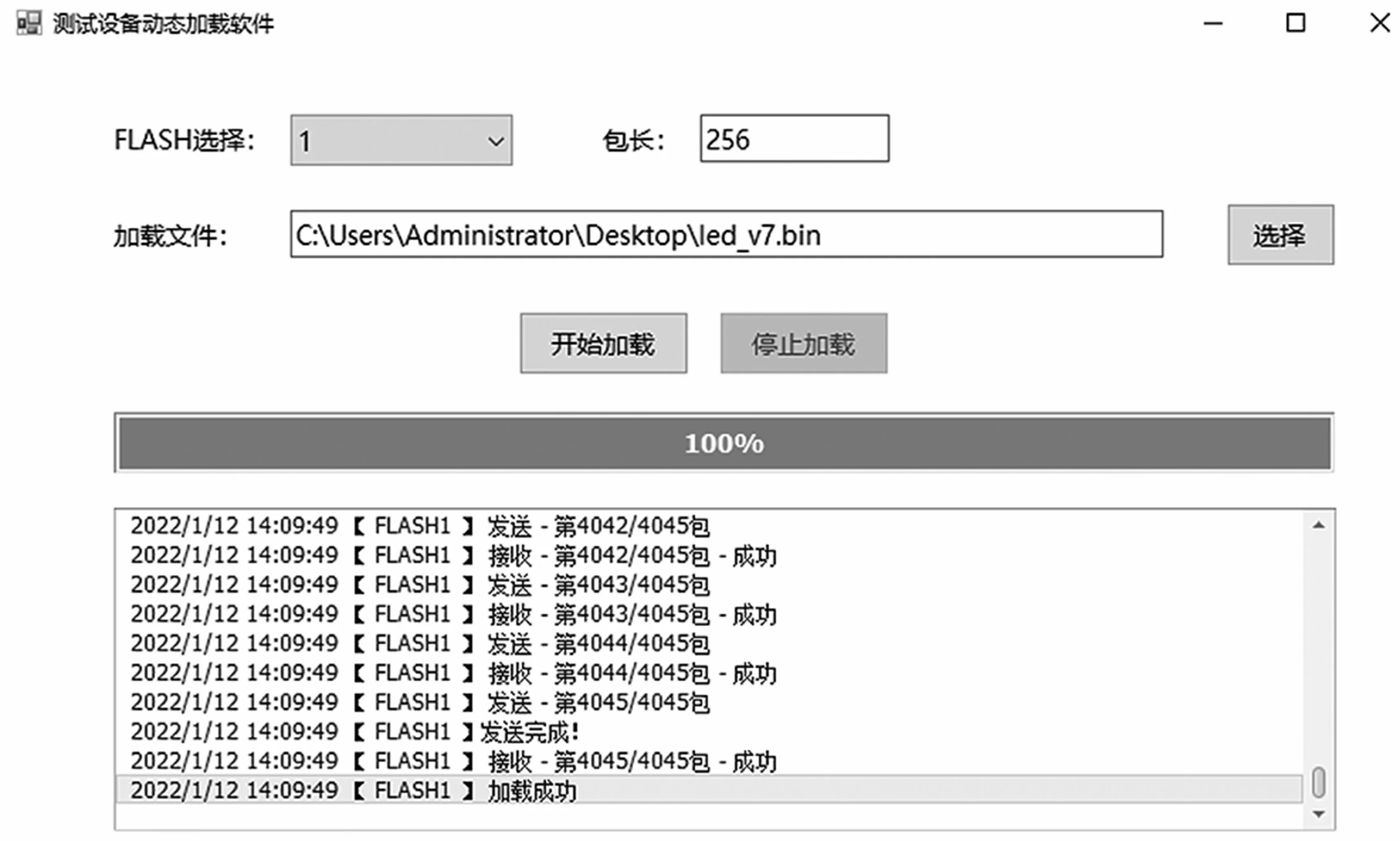

为测试系统的动态加载功能,在动态加载软件中加载由Vivado 事先编译生成好的bin 文件,测试动态加载软件和MCU 嵌入式软件是否工作正常。在测试过程中,通过示波器抓取SPI 接口数据,如图12 所示,bin 文件的加载过程如图13 所示。

图12 SPI 接口读写波形

图13 bin 文件加载过程

从图12 中可以看出,MCU 嵌入式软件能够对SPI 接口进行正常的读写,读写时钟为42 Mbit/s。从图13 中可以看出,动态加载软件的bin 文件加载过程能够与MCU 嵌入式软件之间进行正确的数据交互。加载不同的bin 文件后,FPGA 芯片均能从SPI Flash 中加载程序,并运行正常。

5 结语

本文针对民用电子测试系统FPGA 程序快速更换问题,提出了一种基于STM32F407的FPGA 动态加载设计方法,给出了系统总体设计方案,并对系统内的软硬件设计进行了详细的阐述,最后,给出了系统测试方法。本文方法在保证设计要求和可行性的同时,实现了SPI FLASH的快速高效读取,降低单片机开发难度,缩短了开发周期。同时,该设计方法使系统结构变得更简明,并具有很好的移植性,值得其他民用电子测试系统借鉴。