基于ANSYS 的挠性基板叠装互联组件热分析

2022-04-01赵鲁燕农红密

李 鹏,赵鲁燕,农红密

(桂林电子科技大学 海洋工程学院,广西 北海 536000)

集成电路技术飞速发展使得电子产品朝轻、薄、短、小方向不断革新,三维组装技术的出现更有利于提高组装密度和功能集成度。三维组装技术主要包含芯片级挠性叠装组装和刚性板级立体组装技术两类[1]。较之传统多芯片叠装技术,刚性板级立体组装技术发展相对滞后,板间采用的导线或插槽连接导致基板厚度增大及接口性能大大受限[2]。采用挠性多层基板经卷曲折叠形成立体组件后进行灌封固化可有效降低组件高度,提升电子产品的电气连接可靠性。

目前,国内外已有学者针对挠性基板互联结构进行了热-结构可靠性方面的诸多研究。聂国健等[1]针对挠性光电互联结构进行焊点热应力仿真分析,热循环条件下可保证光电传输的稳定性。李根宝等[3]进行了多芯片PCB 组件热布局数值分析,探讨了基板参数设定对芯片布局优化效果的影响规律。崔昊杨等[4]进行了多电子元件及芯片组布局热分析,研究表明元件不同布局将导致电路组件温度差异,合理布置元件可显著降低组件热应力。Kim 等[5]研究得到了挠性基板互联结构在热-机械载荷作用下保证信号稳定输出的方法。Kuo 等[6]研究了三维堆叠挠性基板热疲劳可靠性,给出了元件布局对产品热疲劳可靠性的影响。

相关研究结果表明,芯片布局状态是影响挠性基板叠装组件热可靠性的主要因素,有必要进一步探讨芯片布局对组件热可靠性的影响。本文以挠性基板叠装互联结构热分析为目标,基于ANSYS 软件对挠性基板叠装组件的稳态热性能进行研究,在不同芯片布局条件及灌封材料条件下进行稳态热传导对比分析,得到了挠性组件最佳芯片平面布局方案,给出了组件内部芯片温度最优条件对应的结构参数。

1 叠装组件有限元建模

挠性基板叠装互联组件层数多、发热芯片多、布局密度大且整体灌封。组件中存在大量有源及无源器件,组件工作时消耗的电能绝大部分转换为热能[1]。

基于实际工况,确保仿真分析精度前提下针对研究对象提出合理简化的仿真模型,只考虑组件中功率较大发热器件,忽略发热较少的器件。主要发热器件包括位于各层的10 个芯片和1 个稳压管,元器件组装挠性基板并经回流焊接。为简化分析,用模塑封材料来代替整个芯片,不考虑组件引脚及焊料影响,印制电路板采用统一的基板材料。

1.1 有限元模型建立

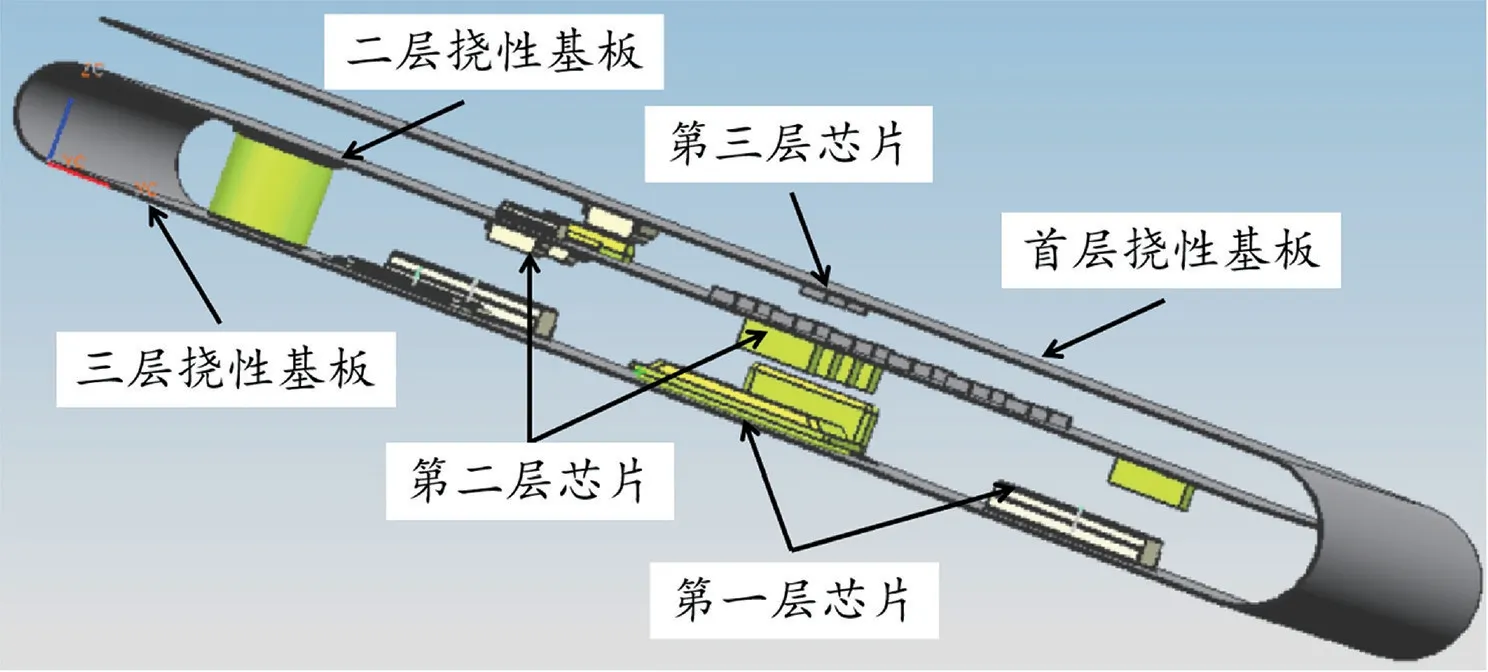

本文研究的挠性基板叠装互联组件结构如图1 所示,组装芯片后的挠性基板经卷曲折叠形成三层立体组装结构。随后,采用灌封材料灌封组件首层基板和第三层基板间的芯片分布区。

图1 互联结构示意图Fig.1 Schematic diagram of interconnection structure

1.2 材料参数定义

仿真分析时主要考虑组件热导率对其散热性能的影响,组件主要发热元件及内部材料热导率参数如表1 所列[7-9]。其中,内部芯片采用环氧树脂模封块替代,热导率取0.4 W·m-1·K-1。进行组件整体灌封时选用HY484P 环氧树脂作为灌封材料。

表1 组件材料参数Tab.1 Material parameters of components

接插件是挠性基板叠装组件与外部电路信号交互的通道,组件经挠性基板与接插件上焊点相连,外部通过插针与外电路相连。为简化分析模型,接插件采用LCP 塑料替代,热导率取0.32 W·m-1·K-1。仿真分析过程在外部对流系数取10 W·m-2·K-1的条件下进行[7]。

1.3 模型建立及网格划分

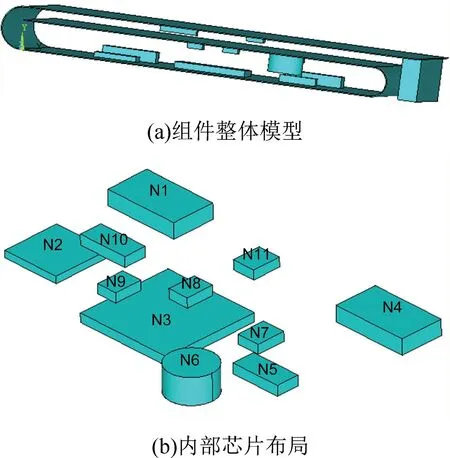

建模是仿真分析的首要步骤,模型合理与否直接决定运算精度[10]。为便于后续组件布局优化和材料选择优化,采用ANSYS 软件自带APDL 参数化模块建立参数化有限元模型[8]。参数化建模便于后续改变模型几何特征、元件布局和材料参数等,提升了模型后续参数优化对比的适应性。采用ANSYS 前处理功能[9],结合自底向上和体素生成方法,生成组件三维整体模型,叠装结构及内部芯片布局模型如图2 所示,组件内部芯片尺寸等参数如表2 所列。

图2 互联结构三维模型Fig.2 3D model of interconnection structure

表2 内部芯片结构参数Tab.2 Structure parameters of chip

网格划分是保证分析准度的关键,网格划分好坏直接影响到运算精度和速度。因组件各部分尺寸差异较大,自动网格划分生成的较多畸形单元大大影响分析结果,本文采用人工控制网格划分方式,选用8 结点四面体有限元热分析单元SOLID70[10]。

为提高运算速度,首先进行较粗略网格划分,然后提高组件核心部位网格划分精度[10]。对温度梯度变化陡峭位置即11 个芯片处进行网格细分,对温度梯度变化缓慢处,如远离芯片的基板和灌封胶处的网格划分较稀疏,网格划分后的有限元分析模型如图3 所示。

图3 组件整体有限元模型Fig.3 Overall finite element model of components

1.4 边界条件设置

互联组件内部芯片均为发热体,依据表1 材料参数加载各芯片的热生成率。分析条件选择全表面对流方式,对流系数根据实际工况进行设置。组件整体通过右侧接插件与外部电路相连并固定,接插件处设置全约束,右侧面其他位置设置单方向约束,对组件上下面各6 个螺钉固定处设置节点全约束[4]。

2 叠装互联组件热分析

挠性叠装互联组件有三层结构,三层基板上均分布有芯片并整体灌封。除同层基板间热耦合作用外,因灌封胶热导使得层与层间会产生较大热干扰,有必要对内部芯片布局进行优化。芯片平面布局指的是对组件内部芯片在其所在层内进行分布位置调整,不作层与层间移动[4],内部不同芯片布局方案如表3 所列。

表3 不同芯片布局方案Tab.3 Different chip layout schemes

对初始布局(方案1)模型进行热分析,组件内部最高温度如表4 所列,虽然芯片N7 和N11 总功率不大、体积较小,但其热生成率却高达1.97×107W·m-3。结果显示,组件最高温度在芯片N7 上,同时N6、N8、N9 和N11 温度也相对较高,因稳压管N6体积大、功率高,确定布局在第二层右下角位置[11]。然后,针对N7、N8、N9 和N11 芯片进行布局调整及分析。分析所得不同布局方案条件对应的组件内部芯片温度分布如图4 所示,对应组件内部最大应力应变分析结果如表5 所列。

表5 不同芯片布局组件最大应力应变Tab.5 Maximum stress and strain of components under different chip layout

图4 不同布局方案的芯片温度云图Fig.4 Chip temperature cloud diagrams of different layout schemes

表4 组件内部最高温度分布Tab.4 Max-temperature distribution of different chip layouts

分析可知,随着芯片布局条件的改变,组件内部最高温度出现位置不同,芯片布局方案1 组件整体温度显著过高且应力最大。依据高温芯片分散布局的原则[12],将N7 置于左下角、N11 置于上边靠左位置时,对应组件最高温度降幅高达24.11 ℃,此时芯片最大应力下降也较为显著。

同样,可对调整内部芯片位置及间距所得的其余5 种布局方案进行分析。对比可知,布局方案2 对应最高温度出现在N11,且受N8 影响较大。调整N8 布局至右边中间位置所得芯片布局方案3 对应温度基本不变但应力较小。布局方案4 拉开了相互影响较大的N11 和N7 的间距,结果显示温度降低且最高温度出现位置转移至N7,但应力水平仍较高。进一步拉大N7 与N11 间距、调整N9 位置得到布局方案5,分析结果显示最高温度点出现在N8 且整体温度和应力均得到了改善。调整N8 位置得到布局方案6,分析结果表明组件温度较之方案5 显著下降,且最高温度点转移至N7,此时对应芯片应力和应变值均最小。

首先,政府需要深刻认识乡村旅游所带来的机遇与挑战,化被动为主动,积极开展相关工作;其次,深入了解当地固有的自然资源,探索如何将其优势实现最大化;再者,根据如今乡村旅游业的现状,分析潜在游客市场,进行全局统一规划,指导乡村旅游的可持续发展。

选取布局方案1 和方案6,内部芯片应力分布情况如图5 所示。分析可知,布局方案6 对应组件整体温度、整体最大应力、整体最大应变和芯片最大应力值均最小,此方案是最优芯片平面布局方案。

图5 组件内部芯片应力分布图Fig.5 Stress distribution diagram of chip inside the components

综上所述,从散热角度来看,通过将高热生成率芯片在组件上呈四角型分布且避免垂直层间芯片重叠可显著改善组件热环境。布局方案6 中,热生成率高的芯片N6、N7、N9 和N11 分布在组件四角位置,芯片N8 位于第二层中间位置,其余器件则均匀分布其间。此时,组件内部芯片最高温度下降最为明显,且热场分布较均匀,可有效减小各区域温度峰值间的温度梯度,减少热应力积聚。

3 组件温度场影响因素分析

相关研究表明[13-15],灌封胶材料热导率及厚度、环境对流条件等因素对组件内部芯片温度场分析影响较大,有必要对其展开进一步分析。基于正交试验分析法可研究各主要因素对挠性组件温度场的影响权重及规律。其中,温度场影响因素主要包括基板热导率、灌封胶热导率及环境对流系数等。

3.1 正交试验设计

在影响组件温度场的四个影响因素中,本文取灌封胶厚度固定值,选用三因素三水平的正交试验设计方法设计试验[16]。所选三个影响因素为基板热导率J、灌封胶热导率G 和环境对流系数H。依据实际工况,各因素选择三种不同因素水平,如表6 所列。其中,所选三类基板材料分别是聚酰亚胺、聚酯树脂和聚芳香酰胺;所选三类灌封胶材料型号分别是HY484P、HY484T 和PX439N/GY。

表6 结构参数组合因素水平Tab.6 Structural parameter combination factor level

根据前述确定的试验因素及水平,采用等水平正交试验设计安排试验,选取等水平正交表L9(34)安排结构参数组合[12]。其中,所选正交表中存在的空白列可用作极差分析的误差项。

3.2 结果分析与讨论

基于前述芯片布局方案6 进行仿真分析,除正交试验方案涉及的材料参数外,组件其余材料参数、结构参数及分析模型与前述分析保持一致。叠装组件上下层均匀对称灌封,灌封厚度可改变且对温度场分布有一定影响。分析时,上下层灌封层厚度D 水平分别取5.3,2.2,0.4 mm。依据L9(34)正交表、针对三种不同灌封厚度仿真分析后所得结果如表7 所列。

表7 正交试验分析结果Tab.7 Orthogonal test analysis results

分析仿真结果得到各因素正交分析结果和极差分析结果如表8 所列,通过极差大小可判断、评价各因素对组件内部温度影响程度[17]。分析结果表明,灌封胶热导率对组件内部温度影响最大,权重为49.71%;外界对流系数、上下层灌封胶厚度对结果影响较为显著,权重为29.01%和15.83%,基板热导率影响程度最小,权重仅5.45%,可以忽略不计。

表8 正交试验极差分析结果Tab.8 Orthogonal test range analysis results

经分析可知,挠性组件内部最佳温度分布对应因素组合为D1-K3-J3-G3,对应的内部芯片最高温度为71.138 ℃。除基板热导率外,各影响因素极差分析曲线如图6 所示,据此可观察组件内部温度分布随各因素的变化情况,组件内部芯片应力分布如图7 所示。

图6 影响因素极差分析曲线Fig.6 Range analysis curves of influencing factor

图7 组件内部芯片应力分布图Fig.7 Stress distribution diagram of chip inside the components

实际应用中,为获得最佳组件温度分布,选择材料时要以提高灌封胶热导率及外部对流系数为主要因素,并兼顾影响组件整体组装高度的灌封层厚度[18]。

4 结论

本文针对基于ANSYS 建立的挠性基板叠装互联组件三维有限元模型进行了稳态热分析,对比了挠性互联组件各芯片平面布局条件下的热特性,并基于正交试验分析了影响组件温度场各主要因素。研究结果表明,从热应力角度来看,高温芯片位于中间层时组件温度场分布更均匀,布局方案6 是最优芯片布局;叠装组件热分析影响因素中,灌封胶热导率影响最显著,权重为49.71%;空气对流系数、灌封胶厚度对结果影响较显著,权重分别是29.01%和15.83%,基板热导率影响最小。最后,分析给出了组件内部最佳温度分布对应的因素组合。通过调整影响因素可有效降低组件芯片温度值及热应力,提高组件热可靠性。本文的研究结果可为进一步改进挠性组件叠装互联结构芯片布局及提升组件热可靠性提供参考。