微小型、低功耗三轴高冲击存储测试装置

2022-03-21张振海牛兰杰李禄刚3宋钱骞4张大治

李 锐,张振海,牛兰杰,李禄刚3,,宋钱骞4,,赵 旭,张大治

(1.北京理工大学,北京 100081;2.西安机电信息技术研究所,陕西 西安 710065;3.湖北三江 航天红林探控有限公司,湖北 孝感 432000;4.北京旋极信息技术股份有限公司, 北京 100094;5.航空工业北京长城计量测试技术研究所,北京 100095)

0 引言

随着现代化武器装备和防护工程的发展,侵彻硬目标高冲击试验研究愈发重要[1]。高冲击试验通过弹载存储测试装置采集和存储试验信号,然后读取试验数据进行分析处理,得到有用信息。该技术是侵彻引信设计与层数识别的重要数据支撑[2],也是分析评价防护工程有效性的重要手段[3]。侵彻灵巧弹药、超巡武器是精确打击敌方入侵航母等大型舰船、地下指挥中心与核设施等高价值目标的杀手锏武器。为了有效打击和毁伤坚固防护目标,侵彻速度越来越高,冲击加速度幅值由几万g到十几万g,甚至二十万g以上,这对弹载存储测试装置提出了更高要求。国外的弹载测试装置起步较早,例如美国Lawrence liversore弹道数据记录仪,该装置体积为Φ4.25″×Φ0.25″,采样频率200 kSps,存储容量2 KB。之后推出的CM346弹载记录器,可以承受10万g冲击,采样率1 Mbps,其内置电路板尺寸至少在20 mm×100 mm[4]。国内多家单位已经开展多种弹载存储测试装置产品。中北大学研制的微小型记录仪能记录弹上多种参数,承受49 000g冲击,内壳外形结构尺寸为Ф100 mm×80 mm,重0.6 kg,低功耗模式下电流2~5 mA,分数据采集板,状态控制板和信号调理板,掉电后能记录10 ms数据。北京理工大学研制的某款存储测试装置其PCB是边长大于30 mm的多片方形板,采样率800 kSps,存储容量4 MB[5]。现阶段国内的弹载存储测试装置或多或少存在某些缺陷,装置可靠性需要进一步提高。高冲击试验有时采集数据不全,甚至采集不到有效数据,导致高冲击测试试验不成功。为应对越来越高的冲击强度,对失效形式进行分析,提出三轴高冲击存储测试装置。

1 存储测试装置总体设计

弹载存储测试装置有多种失效形式[6],任何部件的抗过载能力不足都会导致装置工作异常。为了降低失效概率,除了合理设计壳体结构、隔离缓冲[7]以及可靠灌封外[8],PCB电路板微小型化设计尤为重要。PCB板尺寸越小,受冲击损坏概率越小[9]。实际测试需求会对存储测试装置的灌封大小、安装尺寸等有限制,小尺寸的PCB板为外壳及灌封保护装置提供了更大的空间。

弹体侵彻硬目标以及冲击测试过程中,冲击与振动载荷会降低电池供电可靠性[10]。存储测试装置在受到冲击时会发生瞬时掉电甚至电池损坏。为保证这些情况下仍能完成数据采集与数据存储工作,要求该装置有掉电工作能力,因此合理设计电源电路,选用固体电容作为储能元件尤为重要。保证冲击发生之前储存足够的电能,在冲击发生之后为整个数据采集与存储过程提供足够电能。由于电容存储电量有限,要求整个装置的功耗越低越好。

依据实际需求提出存储测试装置应具有微小型、低功耗与掉电保护功能。该装置主要性能指标和功能指标包括:三轴向同步采集,单轴向采样频率不低于100 kHz,12位ADC精度,支持连续存储时间不低于500 ms。

存储测试装置的前端为三轴高冲击加速度传感器,将传感器信号进行调整、放大、滤波,再进行A/D转换,并存储于数据存储器中。为减少器件,以缩小尺寸和降低功耗,选用片内ADC。存储测试装置灌封于金属壳体中,提高其抗冲击能力。传感器与存储测试装置通过足够长引线连接,防止拉断甚至压断引线。存储测试装置可以安装于弹体内缓冲结构中,传感器和装置外壳固连,减少冲击损坏概率[7,11]。传感器也可以通过硬连接方式安装于弹头位置,并被存储测试装置外壳笼罩保护,这样传感器信号是未经缓冲结构过滤和衰减的原始冲击过载信号。存储测试装置总体设计组成框图如图1所示。

图1 存储测试装置组成框图Fig.1 Storage test device block diagram

2 三轴高冲击存储测试装置

2.1 数据采集与存储模块设计

MCU主控芯片选用ST公司TSSOP20封装的STM32G031芯片,该MCU芯片采用cortex-M0内核,功耗较低,最高64 MHz主频,64 KB的片内Flash,8 KB的片内SRAM。工作电压范围是1.7~3.3 V,保证供电电压下降时,该芯片仍能持续稳定工作,可靠性较高。ADC模块支持原生12位,最高支持16个外部通道,3个内部通道,可以在全电压范围内稳定工作,单通道最高采样率2 MSps,满足100 kHz最低采样频率要求。ADC的3个内部通道,分别是电源电压、参考电压和温度。这些参数直接影响片内ADC的转换结果,在供电电压下降的情况下,同时采集3个内部通道有助于传感器数据的分析与校正。

由于片外晶振在高冲击下容易失效[12],导致数据采集任务无法执行。存储测试装置的器件增加会带来整体可靠性下降,且时钟振荡电路所占PCB空间较大,因此选择片内高速全集成RC振荡器生成时钟源。

低功耗、小体积封装是数据存储器选型要求。Flash、EPROM、EEPROM、铁电存储器等是较为常见的存储器类型。其中Flash存储器容量大,应用较多,但是工作电流较大、功耗较高,单次写入时间较长且不稳定。铁电存储器功耗极低,每次访问存储器写入时间短,可重复读写次数高,容量虽不如前述存储器高,但能满足测试系统要求,因此选用容量为512 KB的铁电存储器。

2.2 电源模块设计

为了实现掉电保护功能,在LDO电源芯片之前并联电容器作为储能元件。电源电压越高,能量存储越多。在电容逐渐放电,电压下降的情况下,仍需保证LDO芯片正常工作,因此需要低压差电源管理芯片,且输入电压范围较宽。

实际中由于储能电容容量和电压相互制约,需要选用多个电容并联。线性稳压器输出电流基本等于输入电流,电荷损耗较小。因此用电荷量作为中间量进行计算。依据系统工作时的电流大小和工作时间,计算所需存储的电荷量:

(VLi-VLDO)×C=Q=I×t

(1)

式(1)中,VLi是锂电池电压,VLDO是LDO芯片输出目标电压时的最小输入电压,C是并联电容器容值的总和,Q是存储的电荷量,I是系统工作时的电流,t是工作时间。

工作时间即数据采集的采样时间长度,工作时间不仅受电源限制,还受存储器大小限制。采样率、ADC位数和存储器容量确定的情况下,可以计算出理论上最长的工作时间。以100 kHz采样频率为例,计算存储数据的工作时间。在单帧数据记录三轴加速度数据,三个片内传感器数据时,铁电芯片支持存储数据的时间长度约436 ms。单帧只记录三轴加速度数据时,支持存储数据的时间长度约为900 ms。

主要器件选型确定后计算存储测试装置的工作电流。MCU芯片最大工作电流5.25 mA,铁电存储器最大工作电流2.6 mA,三路仪表放大器最大工作电流共计1.05 mA,运算放大器电流0.91 mA,选择高内阻传感器,工作时电流小于3 mA,工作电流共计12.81 mA。考虑外围电路,留一定冗余,取15 mA工作电流。按500 ms工作时间计算,系统所需电荷量为7.5×10-3C。LDO输出3.3 V所需的最低输入电压为4.3 V,电池电压12 V,电容压降为7.7 V,计算可得电容器所需容值974 μF。

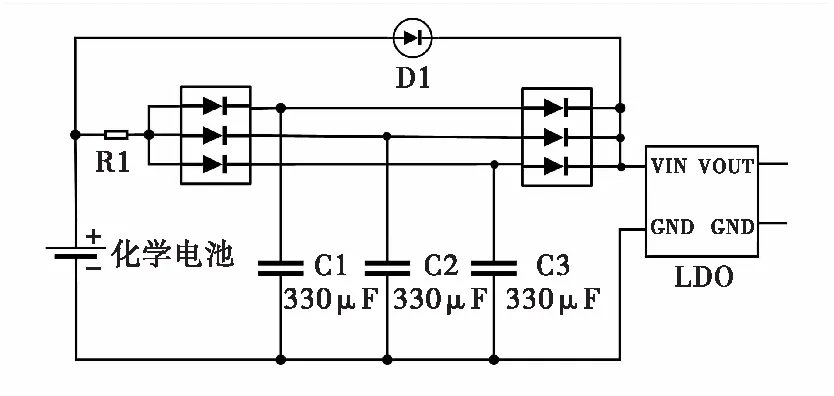

冲击载荷作用可能导致某个储能电容失效短路,其余储能电容器会通过短路通道放电,导致储存的能量耗散。为提高装置的可靠性,在化学电池、三个储能电容和LDO之间,添加两组二极管,防止短路放电。同时还需防止电池失效后电容存储电荷回流到电池端。储能电路原理图如图2所示。

图2 储能电路原理图Fig.2 Schematic diagram of energy storage circuit

2.3 信号放大滤波模块设计与分析

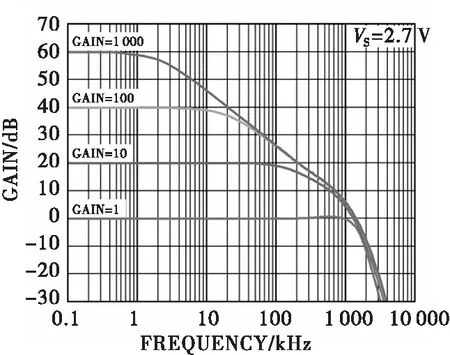

选用AD8226轨到轨输出仪表放大器,其增益范围1~1 000倍,典型工作电流350 μA。增益为1时放大器带宽为1.5 MHz,2.7 V单电源供电时增益和频率关系曲线如图3所示。通过改变外接电阻的阻值大小调整增益大小,有利于存储测试装置与不同型号加速度传感器搭配使用。其输出方程为:

VOUT=G×(VIN+-VIN-)+VREF

(2)

式(2)中,VOUT是输出电压,VIN+和VIN-是差分输入的两端,G是增益系数,VREF是输入参考电压。

增益放大倍数计算式如下:

(3)

式(3)中,RG为外接电阻阻值。

选定传感器后,根据传感器量程和灵敏度,确定所需增益,再由增益放大倍数计算公式求得所需外接的电阻阻值。

图3 AD8226增益和频率的关系曲线Fig.3 AD8226 gain and frequency curve

加速度传感器输出差分信号,有正信号与负信号,而AD转换的输入只支持0~3.3 V电压范围,因此需要对零点进行调整。X轴向和Y轴向两个侧向加速度信号需要将零点偏置设在1.65 V左右,Z轴向的主轴方向信号也需要调整零点位置。根据仪表放大器输出方程,利用仪表运放的参考输入端可以调整零点。仪表放大器参考电压输入端阻抗过高会影响其性能,由电阻分压提供参考电压面临的矛盾是:要么阻抗高,要么功耗高。因此选用运算放大器跟随电阻分压,为三路仪表放大器提供参考电压。

为了简化设计,缩小尺寸、降低功耗,选择使用RC滤波器,其目的是对高频噪声进行抑制,将高于传感器固有频率的信号,以及会引起混叠的高频信号滤除;但是RC滤波的增益衰减缓慢,较低的带宽可能导致对有用信号的过度抑制,甚至导致信号失真,因此要按照实际需求进行取舍。仪表运放在增益较高时的带宽有限,对前级引入的高频噪声也有一定的抑制效果。RC滤波的具体参数可以由传感器频率响应和ADC输入端建立时间为两个边界进行选取。

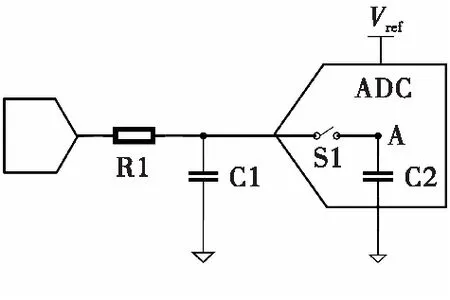

对RC滤波环节和SAR-ADC进行简化,示意图如图4所示。图中C2是ADC内部电容,其容值可以通过查询数据手册得到,Vref是ADC参考电压。

图4 RC及ADC简化模型Fig.4 RC and ADC simplified models

假设前端驱动是理想驱动,即在给C1,C2充电的过程中前端电压保持不变。ADC单周期内包含采样时间和逐级逼近时间。转换结束后C2放电,为下一次采样做准备。

Tconv=T采样+TSAR

(4)

式(4)中,Tconv表示单次转换时间,T采样表示采样时间,TSAR表示单次转换逐级逼近时间。

采样时S1闭合,C2充电。要保证在采样时间内C2被充电至输入电压附近,且差值小于ADC的1/2LSB。讨论最难达到的情形,即上一次转换结束,C2完全放电,且此次转换的输入为Vref。此时节点A需要建立的电压Vsettle为:

(5)

式(5)中,b是ADC位数。

在新的ADC采样周期转换开始前,C1两端电压为Vref,S1闭合后瞬间,C1和C2上电荷重新分布。此时节点A电压VC2为:

(6)

式(6)中,C1表示外接电容C1的容值,C2是ADC内部电容C2的容值。

在R1,C1,C2组成的RC环节时间常数τ如下:

τ=R1×(C1+C2)

(7)

式(7)中,R1是外接电阻R1的阻值。

由此,可以计算出电压建立所需时间Tsettle,采样时间应大于建立时间,如式(8)所示。

(8)

RC系统的带宽BW如式(9)所示:

(9)

采样频率一定、ADC时钟频率一定的情况下,可以得到采样时间。依据式(8)和带宽限制就可以确定RC参数选定范围。

ADC转换位数一定时,越高的ADC时钟频率,单次转换中的逐级逼近时间越短。由式(4)可推知,采样频率一定时,ADC时钟频率越高,ADC单周期的采样时间更长,有利于提高采样精度。

2.4 存储测试装置硬件电路研制

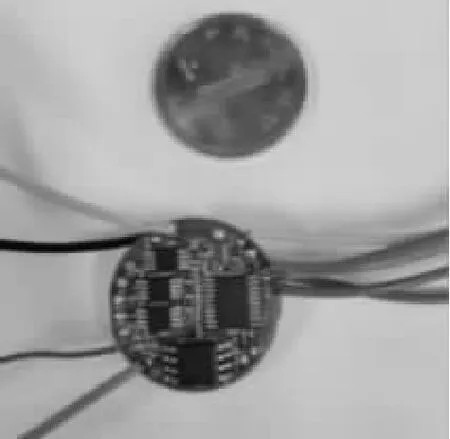

为便于后期调试,把主控剩余的三个引脚定义为输出模式。在程序的不同阶段输出不同信号,便于检测工作是否正常,也便于调试软件。外围电路中的电容和电阻选用贴片式小封装的型号,PCB电路布板时选用紧凑型焊盘,器件紧密排列,合理布局。制作完成的微小型、低功耗的存储测试装置是一个直径22 mm的圆形双面电路板,焊接元器件后存储测试装置的厚度小于8 mm,如图5所示,便于灌封在微小型壳体内部。

图5 微小型低功耗的存储测试装置实物图Fig.5 Micro low power storage test device

2.5 存储测试装置软件模块设计与分析

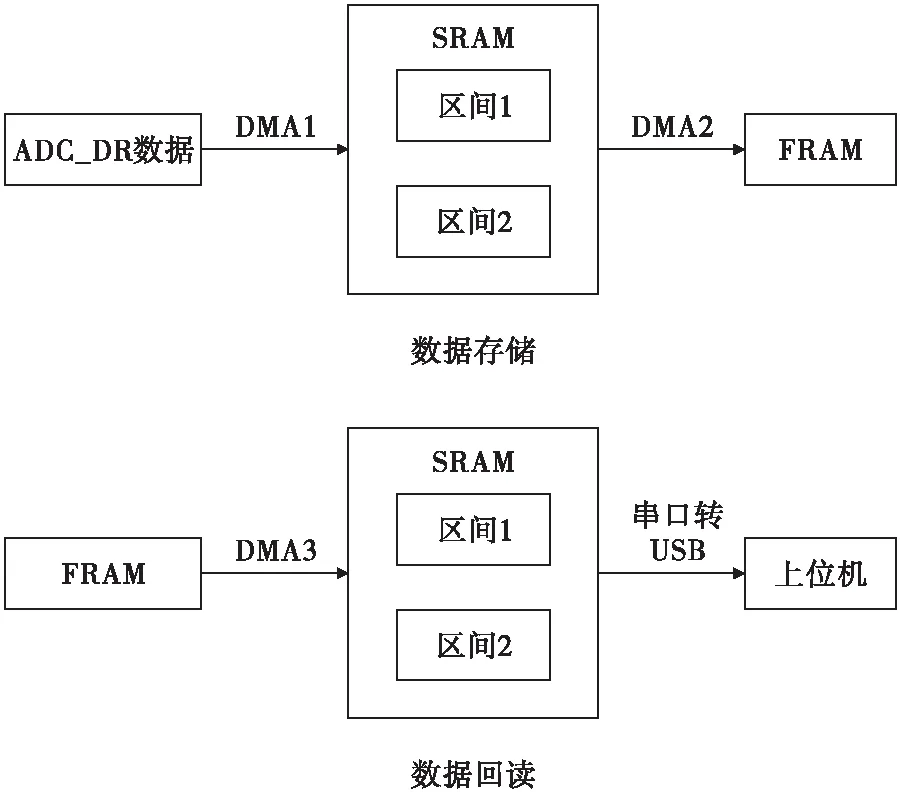

主控芯片选用的STM32系列需要对片内的ADC、SPI、串口等进行相应配置。ADC数据先以DMA直接数据存储方式传输到片内SRAM中,再通过DMA的方式由SRAM传输到外部FRAM中。待连接上位机后,通过串口实现数据读取。数据流如图6所示。

图6 数据传输过程Fig.6 Data transfer process

由于片内SRAM只有8 KB,不能存储整个采集过程的数据,因此需要采取兵乓工作模式,循环多次写入和读取SRAM。在SRAM内部开辟两个区间,其中一个区间进行ADC写入SRAM操作时另一个进行由SRAM到FRAM的数据传输,避免ADC和FRAM同时访问一个SRAM位置。SRAM到FRAM的数据传输完成较快,可以实现ADC连续乒乓模式交替写入两个区块,直至外部FRAM写满。片内的SRAM虽然不能同时读写,但是写入和读取速度很快。有内部逻辑控制的DMA可以有效地实现该场景下的资源调配,只需要配置好各个DMA的优先级即可。

ADC在转换写入SRAM时需要对递减计数寄存器、目标地址寄存器等进行重新配置,这些操作花费的时间尤为关键。经过实测,主频越高转换时间越短,且远小于单次采样周期。为防止测试结束后误触发,覆写FRAM导致采集的实验数据丢失,在FRAM中设置标志位。在触发开始和采集结束后分别进行标记。用于判断FRAM状态,流程图如图7所示。

图7 系统流程图Fig.7 System flow chart

3 调试分析与试验验证

3.1 实际工作电流测量

电路中串联小电阻,用示波器测量电阻两端电压,计算得电流波形图如图8(a)所示,图8(b)为局部放大波形。图中可以看出等待触发和采集存储完成后电流均小于8.5 mA,采集存储时电流峰值为15 mA左右,计算得采集存储任务进行时的电流均值为9.95 mA,功耗低于33 mW。

图8 电流波形Fig.8 The current waveform

3.2 供电模块测试与分析

存储测试系统在进行采集存储工作时电流最大。通过编写测试程序,保持装置在此工作状态下,使其不停地连续A/D转换并循环写入FRAM,在这种状态下进行掉电测试。同时测量12 V直流电源电压和LDO的3.3 V输出,测量掉电后工作时间。如图9所示,在零时刻,断开12 V直流电源,LDO的3.3 V输出保持了700 ms以上,可以完成采集存储任务。

图9 供电模块测试结果Fig.9 Power supply module test result

3.3 信号放大与存储功能测试

为验证存储测试装置信号放大功能是否正常,选择信号发生器生成一定幅值和频率的波形的信号作为输入。存储测试装置进行数据采集,读取存储的数据进行分析。结合仪表运放增益带宽图,在带宽允许情况下选择尽可能大的增益倍数进行测试。选用1.21 kΩ误差0.1%电阻,计算得此时增益为41.826。信号发生器生成1 kHz,60 mV矩形波传感器输入,采集到的数据如图10所示,可以看出调偏置功能符合预期。计算得增益为41.1,增益误差1.6%,增益符合预期。

图10 矩形波测试结果Fig.10 Rectangular wave test results

利用信号发生器生成1 kHz,不同幅值的简谐波作为存储测试装置的输入,保证峰值点附近有采集数据,进行存储测试装置的精度测试。以41.826为增益倍数计算理论值,与实际采集数据进行比较。采集数据调零后如图11所示,数据处理计算得测试结果如表1所示。最大误差为2.6%,测试结果表明采集数据正确可靠。分析误差原因主要为增益误差、信号传输线路损耗、外界干扰。后期在进行装置迭代再版时可以进行相应调整,并优化测试方案,使进入ADC的信号质量更高。测试结果表明调偏置功能符合预期,采集、放大、存储功能模块满足要求。

图11 简谐波测试结果Fig.11 Simple harmonic test results

表1 精度测试结果Tab.1 Accuracy test results

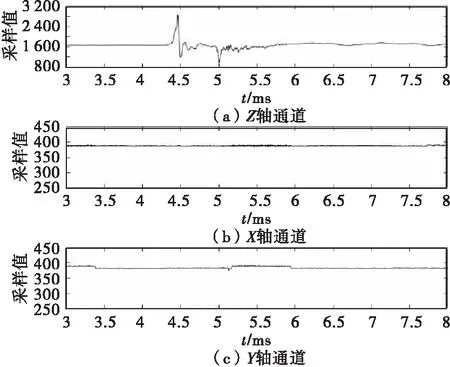

3.4 三轴加速度计冲击测试

功能验证实验选用ADXL377型号三轴加速度计进行测试。依据其灵敏度和量程调整仪表运放的增益。冲击测试试验将加速度传感器和存储测试装置置于直线行进的平台中,平台前进方向为传感器Z轴方向。初始时平台静止,前方0.5 m处放置一挡板,某一时刻撞击平台,使其直线前进并撞到挡板停止。三轴测试示意图如图12所示。

图12 三轴测试示意图Fig.12 Triaxial test diagram

传感器受到两次冲击,分别为出发撞击时和撞到挡板停止时,初始速度为零,第二次撞击前,平台沿Z轴方向位移了0.5 m。忽略传感器旋转,采集数据处理后进行二次积分求得三轴位移。多次试验,积分结果如表2所示,符合实际情况。其中数据(a)如图13所示,局部放大如图14所示。测试结果表明装置采集数据符合实际情况。

表2 二次积分结果Tab.2 Quadratic integral result

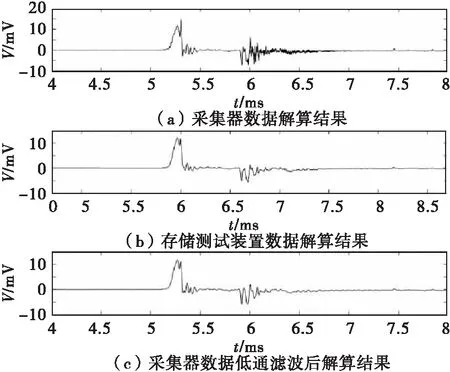

3.5 空气炮高冲击试验与分析

为验证存储测试装置高冲击环境下信号采集功能,进行空气炮加载试验。压缩空气推动炮管内模拟试验弹丸与静置于靶室位置的砧体碰撞,瞬间加速砧体向前运动,产生高过载信号。高冲击加速度传感器和砧体硬连接,存储测试装置采集并存储加速度信号。同时加速度计输出信号经由超动态应变仪和NI高速采集系统同步采集输出,与存储测试装置信号进行比对。砧体上贴有合作光栅,与激光干涉仪构成冲击加速度基准信号测试系统,测量并解算出冲击加速度基准信号。

图13 三轴加速度曲线Fig.13 Triaxial acceleration curve

图14 三轴曲线局部放大Fig.14 Local amplification of triaxial curve

典型高冲击测试曲线如图15-图18所示。两次高冲击试验,激光干涉仪测试系统输出的加速度基准信号峰值分别为6.377万g和4.919万g。存储测试装置三通道同步采集原始曲线如图15、图16所示。Z轴向为冲击加载主轴方向。根据NI高速采集系统和存储测试装置采集数据解算加速度信号,主轴Z方向解算结果如图17、图18所示。从图中可以看出,两组试验曲线基本吻合。由于存储测试装置100 kHz的采样率低于NI高速采集系统的1 MHz采样率,且板上有RC滤波环节,对高频信号有明显的抑制作用。对NI高速采集系统数据进行低通滤波处理后,与存储测试装置波形趋于一致,说明存储测试装置采集的高冲击信号符合实际情况。

图15 三通道原始曲线1Fig.15 Three channel original curve 1

图16 三通道原始曲线2Fig.16 Three channel original curve 2

图17 主轴方向数据解算结果1Fig.17 Spindle direction data solution result 1

图18 主轴方向数据解算结果2Fig.18 Spindle direction data solution result 2

4 结论

本文提出用于高冲击测试的三轴存储测试装置。该装置体积小、功耗低,电池损毁后依旧可以完成当前数据采集与存储任务,降低了存储测试装置对电池抗冲击性能的要求。PCB电路板直径仅为22 mm,抗高过载能力强,便于灌封保护。整个装置配备外壳、电池并灌封保护后,实际尺寸可以限制在Φ50 mm×50 mm的圆柱体内。装置功耗不高于33 mW,掉电后可工作700 ms以上。该装置实现了三轴同步数据采集与存储功能,采样率100 kHz,采样精度12位,采样时间不少于500 ms。样机测试试验验证了放大模块和调零模块功能,采集数据连续,准确,最大误差2.6%。空气炮高冲击试验中,存储测试装置采集数据与NI高速采集系统采集数据吻合,采集的信号符合实际情况。该存储测试装置具有一定的应用前景。