22 nm 带隙基准电压源的设计

2022-03-16郭苹苹

郭苹苹

(上海电力大学电子与信息工程学院,上海200090)

带隙基准电压源是物联网系统中模拟芯片和数模混合芯片的基本组成单元,它的主要作用是输出一个不受工艺、电源电压和温度变化影响的稳定电压[1],基准电路的稳定性直接影响整个芯片的性能和精度,评价其好坏的性能指标有很多,如温度系数、功耗、面积等。指数曲率补偿、对数曲率补偿等各种曲率补偿技术被用来改善输出基准电压的温度特性[2]。随着管子尺寸的不断减小,工艺技术也越来越小,其中,22 nm 全耗尽绝缘体上硅器件具有很大的优势,其具有优越的栅极控制能力和较低的漏极电流、可忽略不计的衬底电容、没有闩锁效应、具有理想的器件隔离等良好的性能。因此,设计一款22 nm的带隙基准电压源是必要的。

本文在Global Foundries 22 nm FDSOI 先进工艺的基础上,设计一款电源输入电压为1.8 V,输出电压为0.8 V 的结构简单,实用性强,温度系数好,能够应用在大多数SOC 芯片上的性能良好的带隙基准源。

1 带隙基准电压源的原理

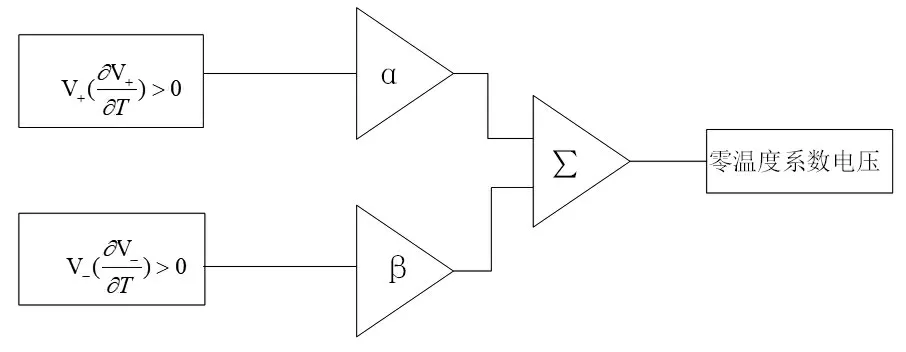

带隙基准电压是将一个负温度系数电压与一个正温度系数电压分别加权求和而获得[3]。最终得到输出温度系数为零的基准电压。其产生原理如图1 所示,用公式可表示为:

图1 带隙电压基准一般原理图

其中,V-为负温度系数电压,V+为正温度系数电压,α 和β为权重系数;合理地调节式中的权重α 和β 使等式(1)成立,从而使带隙电压基准输出电压为零温度系数特性,输出的零温度系数电压的表达式为:

1.1 负温度系数电压

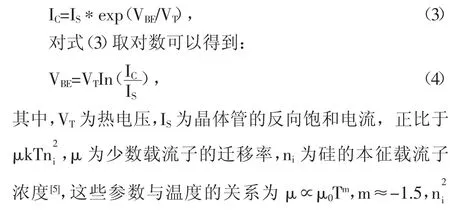

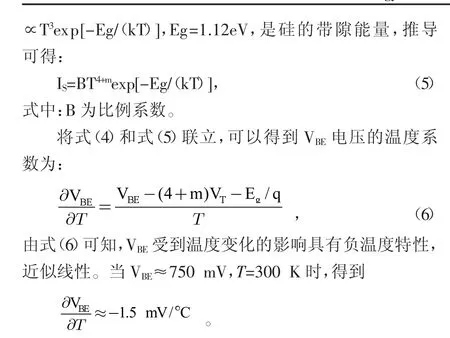

晶体管BJT 的电流在一定条件下,双极型晶体管的基极-发射极电压VBE具有负的温度系数[4];双极型晶体管集电极电流(IC)与基极-发射极电压(VBE)之间的关系为:

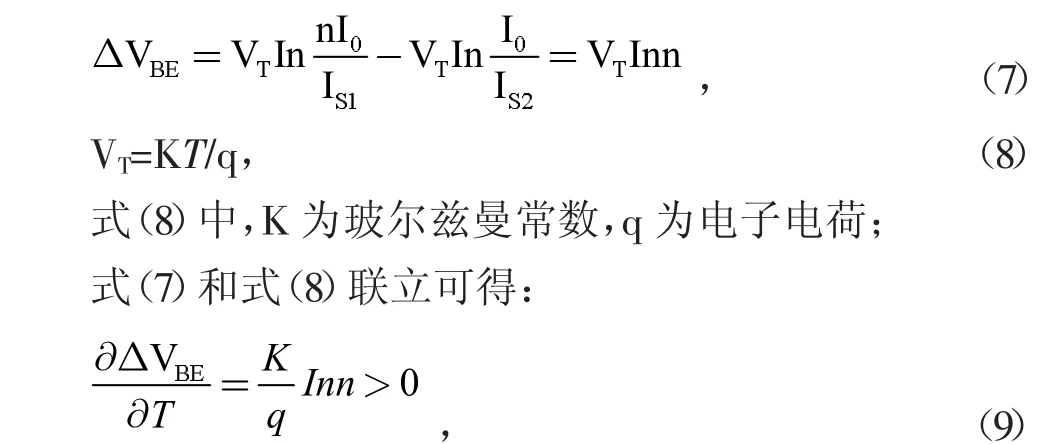

1.2 正温度系数电压

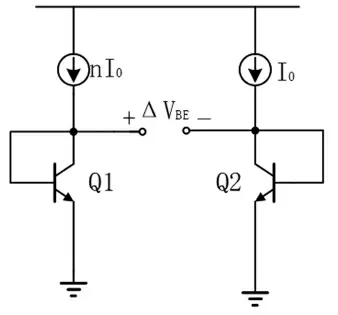

2 个相同的双极性晶体管,工作在不相等的电流密度下,那么这2 个双极性晶体管的基极-发射极电压差△VBE与温度成正相关[6],如图2 所示,三极管Q1 与Q2 完全相同(IS1=IS2=IS),它们的集电极电流分别为nI0和I0,在忽略基极电流的条件下,他们的基极-发射极电压的差值为:

图2 PTAT 电压产生电路

由式(9)可知:△VBE为正温度系数电压,且与温度和集电极电流无关。

2 带隙基准电压源的设计

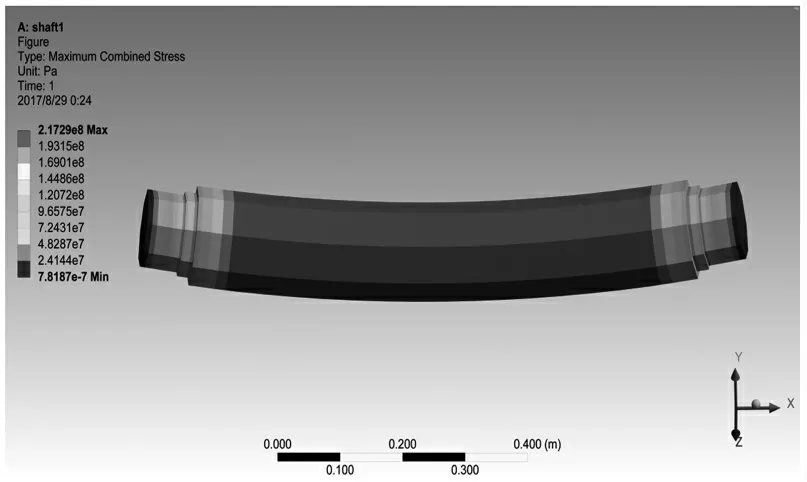

2.1 启动电路和偏置电路的设计

带隙基准电压源在工作时,存在两个平衡工作点,一个是正常工作点,另一个是“简并”偏置点[7]。当所有的晶体管都处于关断状态时,带隙基准电压源的输出电压为零,这就是“简并”偏置点的工作状态,为了避免出现这种“简并”工作状态,必须要有启动电路,使电路进入正常工作状态。如图3 所示,最左边虚线框里的为带隙基准电压源的启动电路,其中EN 与ENN 为电路的使能信号,并且互为反向,工作时,EN 为高电平,ENN 为低电平[8]。当电路上电并使能信号有效的瞬间,流过基准电压产生电路的电流为零,此时P21 关闭,P2打开,N1 的栅极连接的是电源电压VDD,所以N1 导通,把P3 的栅极电位拉到地,P3 管子导通,此时,P2、P3 组成的支路完全导通,产生的电流注入到基准电压产生电路,使整个电路进入到正常工作状态,P1 复制P17 所在支路的电流,N1 为多个NMOS 管串联的倒比管,具有较大的电阻,因此就会瞬间将P3 的栅端电压拉至高电平使P3 管子截止,这时启动电路就不会对基准电路产生影响,从而减小了电路的功耗。若启动不成功,电路就会又进入到零点工作,启动电路会再次启动直至电路启动成功。另外,由于带隙基准电压源是提供电压的源头,所以需通过自偏置技术产生直流偏置电压。如图3 所示的偏置电路,通过调节R1的大小和流过R1的电流就可以改变偏置电压VBN1 和VBN2 的大小,使运放能够正常工作。

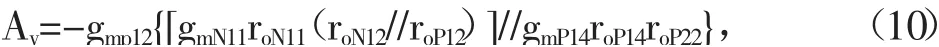

2.2 运算放大器的设计

在基准源中,放大器起钳制电位的作用,同时确保基准核心电路中两条支路的电流相同,放大器的增益越高,钳位效果就越好[9]。普通的差分运放其增益较小,通常只有20 dB 左右,不适合用在带隙基准电路中,为了提高运放的增益,通常采用Casecode 折叠式运放或者两级运放,两级运放虽然增益较高,但是其频率补偿比较困难且增加了电路的复杂度,所以本文采用的是Casecode 折叠式运放,如图3 所示,P10 为电流源MOS 管,P11 和P12为输入差分对管并与N9~N12 构成折叠式共源共栅结构,P13、P14、P22、P23 构成负载,该一阶折叠式共源共栅放大器的增益Av为:

式中,gmN11、gmP14为MOS 管的跨导,roN11、roN12、roP12、roP14、roP22为MOS 管的沟道导通电阻。该一阶折叠式共源共栅放大器的增益可超过80 dB。

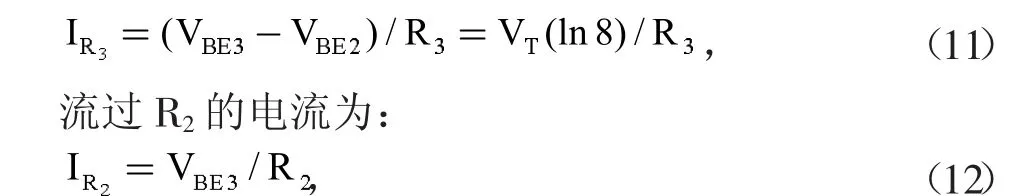

2.3 基准电压产生电路的设计

本文所设计的带隙基准电压源,如图3 所示的最右边虚线框,三极管Q2 的发射面积是Q3 的8 倍,因此三极管Q2 的反向饱和电流为Q3 的1/8。流过P15、P17、P19 的电流比为1∶1∶8,由于运算放大器的钳位作用,使得P16,P18 的漏端电压相等,同时,电阻R2 的阻值与R4相等,所以Q2 与Q3 的集电极电流相等,由此可得流过R3的电流为:

图3 轴组合应力云图

图3 带隙基准电压源整体电路

通过调节R2与R3的比值来控制基准电压源的输出,输出电压的大小由R4、R2、R3的比值决定,与具体电阻值的大小关系不大。

3 电路仿真

基于Global Foundries 22 nm FDSOI 工艺完成带隙基准电压源的设计,并使用Cadence 中的Spectre 仿真工具对该电路的功能进行了仿真。

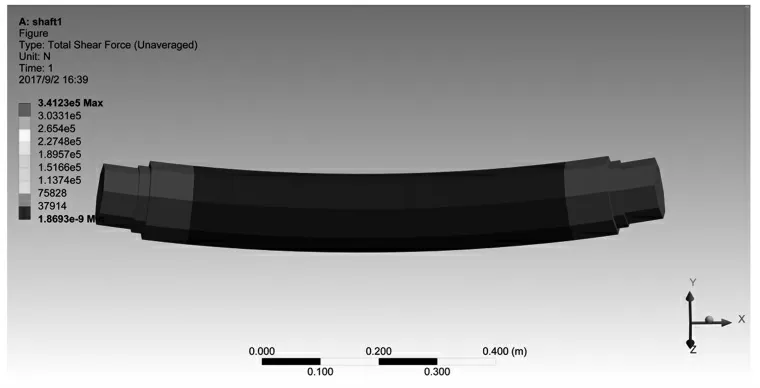

3.1 折叠式共源共栅运算放大器仿真

折叠式共源共栅运算放大器的增益越大,钳位效果越好,因此需进行仿真验证其是否适用于带隙基准电路,仿真结果如图4 所示,仿真结果显示,该放大器的低频增益达82.5 dB,且相位裕度为61.28°,单位增益带宽为1.03 M,因此适用于带隙基准电路。

图4 轴剪力云图

图4 折叠式共源共栅运放的频率特性曲线

3.2 带隙基准源温度特性仿真

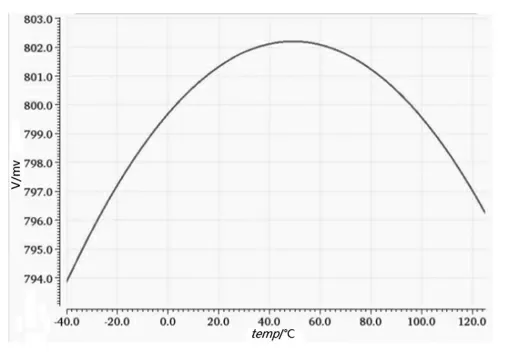

在不同工艺角情况下,温度从-40℃扫描到125℃,带隙基准电压源的温度特性仿真波形如图5 所示,其输出电压变化范围为794~802 mV,温漂约为8 mV,温度系数约为60 ppm/℃。

图5 基准电压随温度变化的仿真曲线

3.3 带隙基准源PVT 仿真

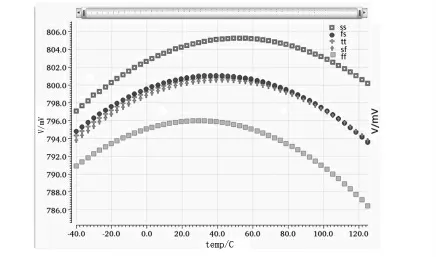

MOS 管,BJT(三极管)和电阻在不同的工艺角下,温度在-40~125℃范围内变化,仿真波形图如图6 所示,带隙基准电压源的输出电压在786.3~806.5 mV 之间变化,变化范围约为-14~6.5 mV,精确度为-1.75%~0.81%。

图6 不同工艺角不同温度下的基准电压仿真图

3.4 带隙基准源直流特性仿真

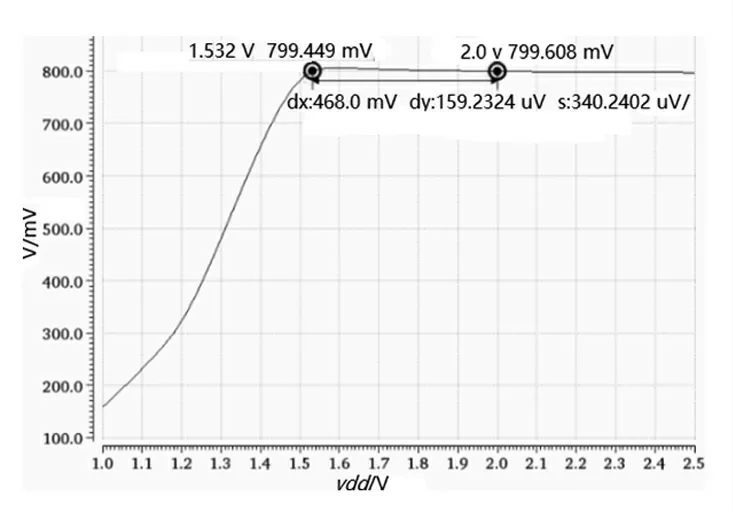

带隙基准源直流特性仿真波形图如图7 所示,对带隙基准源进行DC 仿真,将电源电压从1 V 扫描到2 V,当电源电压达到1.53 V 时输出电压趋于稳定,此时对应的带隙电压为799.753 mV,电源电压在1.53~2 V 变化时,输出电压仅变化了0.16 mV,误差很小。即电源电压的变化对输出电压的影响较小,电路具有良好的电源抑制特性。

图7 基准电压随电源电压变化的仿真图

4结论

本文设计了一款22 nm 的带隙基准电压源,该带隙基准电压源结构简单,易于实现,性能较好,在输入电源电压为1.8 V 时,稳定输出电压为800 mV;在不同工艺角情况下,温度从-40℃扫描到125℃,带隙基准电压源输出电压变化范围为794~802 mV,温漂仅为8 mV;输出电压对电源电压的变化不敏感,具有较好的电源抑制特性;在不同工艺角不同温度下,输出电压的精度较高,是一款能够应用在大多数SOC 芯片上的性能良好的带隙基准电压源。