基于CHROMA 和FPGA 的芯片FT 测试系统的研究

2022-03-16范耀华陈建丽

范耀华,童 杰,苏 江,陈建丽

(广东科学技术职业学院,广东 珠海 519090)

随着智能化潮流的盛行,物联网、大数据、人工智能等已是大势所趋。而芯片作为实现这一切的硬件基础,对其产业化和普及化发挥不可替代的作用。我国集成电路起步较晚,在和发达国家或地区的竞争中处于劣势。但近年来,国内涌现出如海思、中芯国际、天水华天等一批优秀的芯片产业链相关企业,为我国的集成电路事业发展提供强大动力。芯片的产生主要由IC 设计、制造和测试3 个主要环节组成,其中IC 测试作为芯片流入客户前的最后环节,对芯片质量最终把关以及对芯片可靠性和稳定性的检索和鉴别都起到了重要作用[1]。所谓芯片测试,主要分为wafer 测试(CP 测试)和芯片封装或功能的测试(FT 测试,业内定义为Final Test)。而FT 测试作为筛选质量可靠芯片的最后一步,其重要性更是不言而喻。其中,稳定且可靠的FT 测试系统不仅对芯片质量的筛选极为重要,更对保证芯片良率及误宰、误放等方面的达标有重要意义。本文重点讨论的是一个新的稳定FT 测试系统的实现。

1 一般FT 测试方案

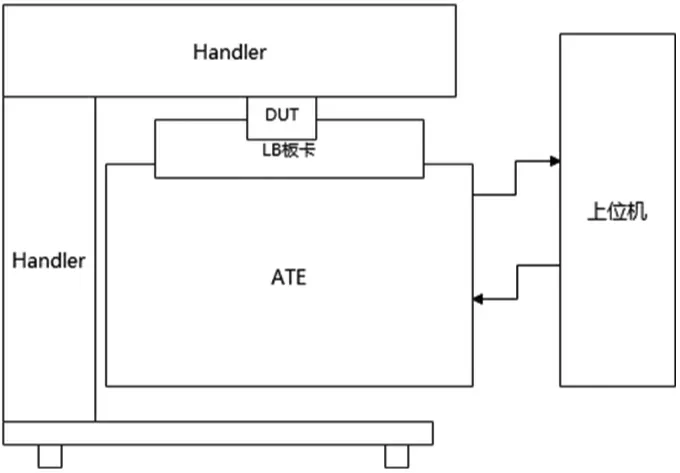

FT 系统主要由上位机、测试机(ATE)、LoadBoard 板卡(LB 板)、装载芯片DUT 板卡、kit、socket 和编带机(Handler)等组成,如图1 所示。

图1 一般测试方案整体框架图

上位机通过不同的通信协议和ATE 进行测试数据或测试结果的交换,而测试机通过LB 板将其可用的测试资源和通道引出,接到DUT 板卡中。在DUT 上装载socket,用于放置被测芯片。一般不同芯片socket 型号、尺寸等均不同,需要订做。通过socket 和配套kit 以镶嵌的方式连接,装载到Handler,对所测芯片实现自动化和连续化,并根据不同测试结果将测试的芯片分bin,这部分在测试系统中很难改动。整个测试系统LB 板卡、DUT 板卡需要测试开发工程师根据被测芯片的测试模块、覆盖功能以及测试需要的数字或模拟通道进行设计开发,kit和socket 需要根据芯片尺寸等参数设计制作。而测试机需要根据芯片被测功能的复杂程度、稳定性以及经济性等因素选择使用。而Handler 作为实现连续和自动测试的专用机械设备,一般选定短期内就不会改变,它可兼容多类型芯片的自动化测试。作为测试开发工程师,除了设计和开发LB、DUT 板卡以及socket、kit 之外,另一个主要工作是根据芯片规格、参数、模块等开发包括上位机程序在内的所有测试程序[2-3]。

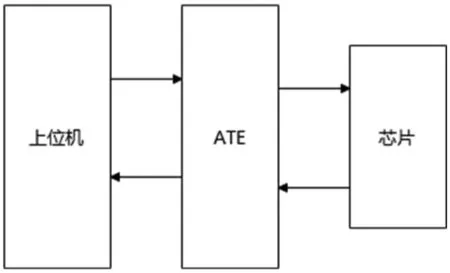

除去Handler、socket、kit 等机械装置,将ATE 和引出ATE 资源的LB 板卡、与LB 板卡相连的DUT 板卡归为一体,整个测试系统将简化为如图2 所示的结构。

图2 测试系统简化图

主要测试过程:

(1)上位机依照测试项顺序发出测试指令,等待ATE返回测试结果(PASS or FAIL),其中如果有一项测试FAIL,则判断为该芯片不良;

(2)ATE 提供测试资源(激励和测试通道等)对芯片进行测试,等待芯片运行结果;

(3)芯片运行其中功能,如果全部运行完成且无误,测试PASS,结果返回ATE,后返回上位机;运行过程中芯片FAIL,结果返回ATE,后返回上位机[4]。

2 基于Chroma 8000 和FPGA 通信的测试方案实现

2.1 Chroma 8000 简介

Chroma 8000 作为电源供应器自动测试系统,能够提供众多变化的硬件选择,如编程交流/直流电源供应器、电子负载、数字电表、示波器、时序/噪声分析器和过电压/短路测试器等。系统结合开放式软件架构Powerpro III,为用户提供弹性、功能强大、具经济效益的自动测试系统,可满足多种形式的电源供应器测试使用。

Chroma 8000 自动测试系统工作于WindowsXP、Windows7 及Windows10 等操作系统下,方便使用Windows 所提供的资源。系统使用优化测试命令技术来防止系统软件将重复的控制命令下到系统硬件装置,可明显地提高测试速度。

对于芯片的FT 测试,Chroma 8000 可提供最多8 sites 同时测试,可满足测试芯片DC/DC、Open/Short 等开短路测试,并可提供256 路测试资源测试芯片电源模块或芯片管教的开短路问题、是否存在电源倒灌、激励-相应是否在可允许范围等。同时Chroma 8000 同时可为SOC 芯片提供强大的功能测试资源,满足各种类型SOC芯片的测试[5]。

2.2 测试方案的具体实现

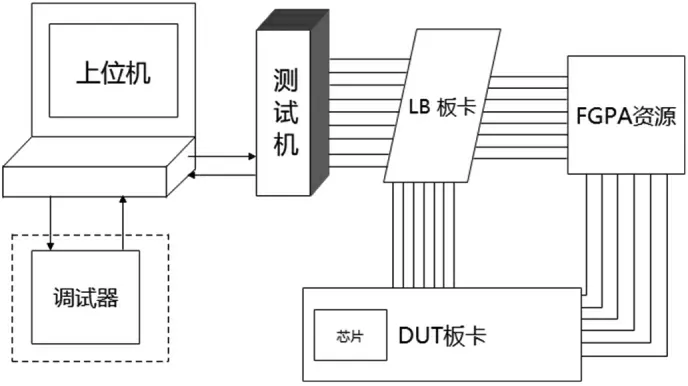

对于芯片FT 测试来说,测试过程可能不仅需要完成对芯片所有功能的覆盖,而且需要根据芯片特性对芯片内部efuse 或者其他寄存器进行不同特性值的烧写。同样,对于同一批次或不同批次的芯片,需要对测试过程中的某些特性进行读取,以便对该批次芯片的不同性能有大致了解,从而对芯片设计或制造等环节提供相应的反馈。对于一般测试方案而言,由于上位机发送的指令和数据都是统一的,为不同芯片发送不同的烧写数据需要在软件算法中,如果采用,会对一般的测试方案带来了很大的挑战。基于此,我们设计了加入FPGA 的芯片测试方案,如图3 所示。

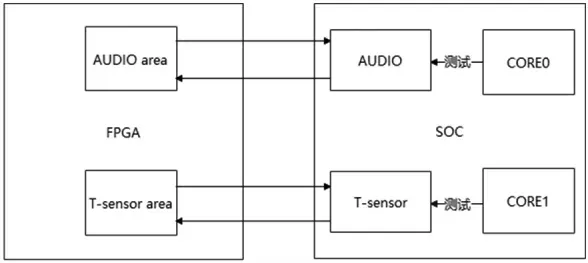

图3 改进后的测试系统图

对于一般测试方案而言,新的测试方案改动部分主要在于测试芯片和ATE 之间增加了FPGA 作为通信桥梁,上位机的测试命令、测试特性数据通过ATE 写入FPGA 的寄存器当中,芯片读取FPGA 寄存器中的测试命令和数据开始相应的测试。具体测试过程:

(1)上位机主要用于发出测试开始命令,等待测试结果(PASS or FAIL),并将需要记录的芯片测试特性数据等做记录。测试过程中,如有必要,通过调试器修改测试主程序做相应调试;

(2)测试机(Chroma 8000 型号ATE)将需要的DC/DC 电源通道、测试资源和测试通道等引出到LB 板卡,并为测试提供硬件的支持。同时将上位机将上位机发来的测试指令等通过LB 板卡写入FPGA 对应寄存器(如果可以,可将FPGA 资源集成到LB 板卡上,以节省空间),等待芯片读取并测试;

(3)LB 板卡将测试机引出的电源通道、测试资源等连接到DUT 板卡上,同时和FPGA 相连,提供相应的电源通道和测试读写通道;

(4)FPGA 通过和DUT 板卡相连从而连接被测芯片,提供相应的寄存器用于保存测试机发来的临时数据和芯片测试过程中的特性数据;

(5)DUT 板卡为被测芯片供电,板卡集成了测试芯片功能所必要的资源,如测试程序存储芯片、继电器、温敏芯片、数字芯片及各种电阻、电容、电感等。同时,DUT 板卡需要有对应的放置芯片socket 位置,该位置不焊接任何元器件,只将socket 通过螺母等机械连接方式连接;

(6)芯片放置于DUT 板卡的socket 中,通过DUT 板卡的通电开机,完成FT 功能性测试,完成所有测试且测试正常,向FPGA 相应寄存器写入测试结果和该芯片对应的特性数据;如果测试不正常,将不正常对应特性写入FPGA 相应寄存器,并将测试FAIL 结果写入相应寄存器。

3 对于加入FPGA 后的测试方案具体分析及例证

3.1 测试方案具体分析

加入FPGA 后的测试方案,看似多了不必要的FPGA中间环节,实则可完成很多必要且一般测试方案无法完成的功能。具体分析如下。

(1)对于一般测试系统,ATE 对于上位机发送的测试指令或测试数据需要及时发送到芯片进行测试,且芯片测试后的芯片特性数据要及时传送到上位机并记录。对于加入FPGA 的测试系统,上位机经过ATE 写到FPGA的测试指令和数据可以给芯片足够的时间读取,且芯片返回的测试性能数据也在FPGA 中保存,可以有足够时间给上位机进行记录,这样就为不同性能的芯片测试带来了很大方便,不会因为各种性能不同的芯片测试时间差异造成芯片的误宰,也不会因为测试数据丢失而造成无法记录;

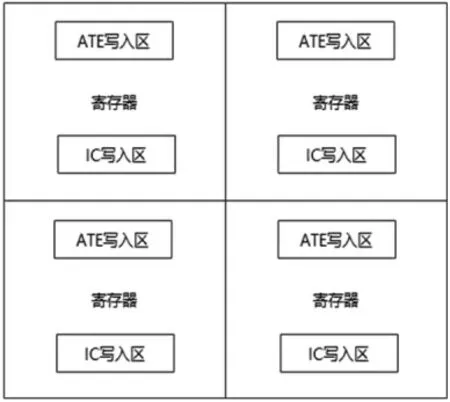

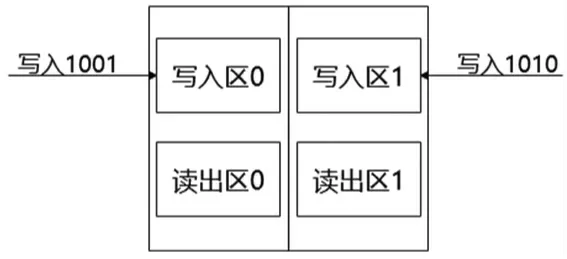

(2)上位机可根据芯片特性发送不同特性值到芯片进行判断或烧写,从而为客户使用芯片带来方便。对于多site 同时测试的系统,将FPGA 分为多个(图4 中为4 个)完全相同的功能区,其中每个区地址不同,从而实现ATE可向对应芯片的ATE 写入区内写入测试指令、测试数据和烧写数据,芯片从其中读出对应的指令和数据进行测试。同样芯片可将测试结果或芯片特性写入对应的IC 写入区供ATE 读取并记录。在一般的方案中,写入芯片的数据由ATE 统一发送,其具体数值做不到因芯片特性而异。FPGA 结构如图4 所示。

图4 FPGA 结构图

(3)对于一般测试方案,如果测试结果FAIL,则直接返回上位机测试结果并关掉该site 的测试资源(即该site断电),这时对于FAIL 项的对应特性由于已经断电,造成上位机无法记录。而使用新的测试方案,对于已经测试FAIL 的芯片,测试的特性数据先写到FPGA 对应的区域内,即使该site 断电,因为FPGA 寄存器中的数据只要不断电就不会丢失,也不会影响上位机读取,从而给FAIL芯片的特性分析带来极大的方便;

(4)芯片测试成本的一个主要考量在于芯片测试时间。对于很多SOC 芯片而言,IC 内部集成模块众多,如对各个模块功能进行单一线性测试,测试时间将会大大增加。如果采用并行测试,测试时间减少,但所考虑的问题涉及复杂的数学模型,调试难度高,开发周期长,上位机和下位机的通信将带来更大的不便。采用新的测试方案,无疑将为并行测试提供了足够信息传输和存储的位置,为并行测试提供了硬件上的必要支持。如现在市面上大多数蓝牙音箱所用芯片,芯片内部集成了温度传感器(T-sensor)、音频录播(AUDIO)等功能,可并行测试,如图5 所示。

图5 并行测试图

SOC 内部可用CORE0 和CORE1 分别对AUDIO 和T-sensor 进行测试,测试性能数据或测试结果可返回FPGA 内部各自区域,等待ATE 读取并传给上位机,完成AUDIO 和T-sensor 的并行测试[6-7]。

3.2 具体测试实现例证

现以集成了温度读取功能的SOC 芯片为例,该例体现了需要测试芯片的温度功能(T-sensor)时的具体测试过程。例证过程为该2 个site 同时测试,芯片已经测试了其他功能,并已了解了温度相关特性后对温度特性进行测试。

(1)上位机发出T-sensor 测试命令,并根据已测内容,判断该芯片在测试T-sensor 需要的参数,如2 个site测试分别发出参数1001 和1010;

(2)测试机提供相应的测试资源到LB 板卡,并将上位机发来的不同参数写入通过LB 板卡写入FPGA 已经为2 个site 芯片定好的寄存器位置。相对于一般测试系统,该系统可以将不同的测试数据写到不同的芯片,更好地有针对性地对不同芯片采取不同的测试手段和方式,如图6 所示。

图6 测试机写入不同数据图

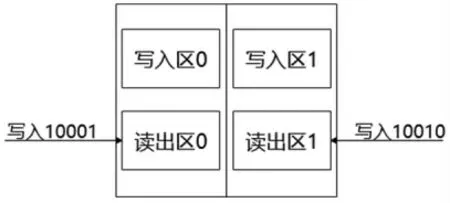

(3)2 个site 芯片通过写入区0 和写入区1 的地址分写读出相应数据,根据相应数据,进行相应功能的测试;

(4)芯片测试过程根据测得的温度不同特性,将该特性转化为对应数据,如10001 和10010,分别写入FPGA对应的读出区,等待测试机读和上位机读取,如图7 所示。

图7 芯片写入不同数据图

(5)测试过程中如果芯片FAIL,则停止测试,并将结果返回上位机;如果测试PASS,同样将结果返回上位机。

注意到,测试过程中即使测试芯片FAIL,相关的FAIL 的特性数据也先写入FPGA 的对应区域中,相对于一般的测试系统,该系统实现了芯片FAIL 断电前已将对应的特性数据写入FPGA 区域内,给之后的FAIL 芯片分析带来很大方便。

4 结束语

本文介绍了一种基于Chroma 8000 和FPGA 通信的芯片测试系统测试方案,主要工作为一般ATE 和测试芯片直接通信的改造。在ATE 和IC 间加入FPGA 芯片作为通信的桥梁,可实现一般测试方案无法实现的功能,并且对于测试时间的减少将发挥更重要的作用。该方案已经在芯片测试,尤其是模块众多、功能复杂的SOC 芯片测试中使用。