一种差分高阶调制联合LDPC编码方案及其FPGA实现*

2022-03-03叶金才1a李国勇1a王国富2李灵巧

叶金才1a,李国勇1a,王国富2,李灵巧

(1.桂林电子科技大学 a.信息与通信学院;b.计算机与信息安全学院,广西 桂林 541004;2.广西科技大学 微电子与材料工程学院,广西 柳州 545616)

0 引 言

近年来随着数字移动无线通信的高速发展,对通信质量和环境的契合度要求越来越高[1]。目前多径干扰的环境中最常用到的物理层解决方案是正交频分复用(Orthogonal Frequency Division Multiplexing,OFDM)联合低密度奇偶校验(Low Density Parity Check,LDPC)码信道编码和多元正交幅度调制(Multiple Quadrature Amplitude Modulation,MQAM),其中LDPC强大的纠错能力以及OFDM的抗多径能力增强了通信的可靠性,但是在一些强多径干扰的环境中,仅依靠OFDM的抗多径能力是不够的[2-3]。因此一种不仅能够在加性高斯白噪声(Additive White Gaussian Noise,AWGN)信道中有良好的误码性能,同时在强多径干扰通信环境中的通信方案尤为重要。由于MQAM信号必须采用同频同相的相干载波来实现相干解调,造成解调中信道估计和载波检测的计算量很大,导致系统接收端硬件实现复杂度提高,并且还需要在OFDM符号中插入导频序列,降低了系统的有效传输速率[4-5]。

时域差分幅度相移键控采用非相干解调[6],不做信道估计便能获得良好的性能。时域差分系统能较好地抵抗频率选择性衰落,在载波相位偏移较大的情况下也能够解调出正确的数据[7],避免了相干解调时的相位模糊问题[8],同时不需要导频信号,节省了信道资源。Chow等[9]对16DAPSK在Rayleigh信道中的误码率性能进行了仿真和分析,得出了差分幅度调制的最优电平及解调的最优判决域,为16DAPSK的实际应用提供了理论基础。秦雅娟等人[10]提出了卷积编码频域16DAPSK在OFDM系统下的解调译码新方法,使系统的误码性能改善了约1.2 dB。张雪等人[11]提出了LDPC编码的并行结构的实现方案,但没有对其在实际系统中的性能做相关分析。上述学者在算法和理论层面上做出了创新和验证。本文针对16DAPSK软解调在OFDM系统中联合LDPC的技术,在硬件验证和实现环节给出了具体的方案和操作步骤。

根据在高阶调制中不同比特位的抗噪声性能差异[12],本文采用国际空间数据系统咨询委员会(Consultative Committee for Space Data Systems,CCSDS)发布的(2 560,1 024)LDPC码结构与16DAPSK调制技术,利用信道中输出的16DAPSK幅度软信息和相位软信息,结合LDPC最小和译码算法不受输入信息的同比例因子影响的特点,降低系统的误码率;同时通过XILINX ZEDBOARD 硬件平台详尽介绍每个模块的实现步骤。下文中统称该方案为时域差分16DAPSK联合LDPC编码。

1 16DAPSK联合LDPC编码的方案设计

1.1 整体方案介绍

首先将比特信息进行串并转换后[13],按照CCSDS(2 560,1 024)LDPC规则编码,输出到比特交织模块,进而将数据按照16DAPSK调制原则完成编码映射。接收端将16DAPSK的解调方式采用软解调,LDPC译码采用最小和译码算法进行译码输出,其特点是不需要对信道噪声进行估计[12]。

1.2 LDPC编码与16DAPSK调制算法

LDPC码主要分为随机LDPC码和准循环码(QC-LDPC)两种。随机LDPC码在误码率瀑布区有更好的瀑布性能[14],然而在译码过程中需要更多迭代次数,不利于硬件实现。QC-LDPC根据子循环矩阵的第一行向量,在编码电路中通过循环移位得到整个矩阵,有利于简化硬件实现。

采用官方文档CCSDS131.1-O-1提出的结构为(2 560,1 024)、码率为0.4的QC-LDPC码。生成矩阵如公式(1)所示,其中B是由稠密循环矩阵和全零列向量组成的矩阵。

(1)

设待编码信息为向量X,其长度为1 024 b,如等式(2)所示:

(2)

将X与G相乘得到码字Y,其包含1 024个信息数据和1 536个校验数据,如式(3)所示:

(3)

由于16DAPSK在空间映射中分为幅度差分(2DASK)和相位差分(8DPSK)两部分[15],因此将LDPC编码后的数据转换为4 b一组的形式进行16DAPSK调制,得出16DAPSK调制后的信号集为

S={αna·ejnpφ|na∈{0,1},np∈{0,1,…,7}}。

(4)

式中:α为高调制电平与低调制电平的比值,表示2DASK调制的幅度调制参数,大小为2;npπ=1/4nπ。设4 b的二进制数为d3d2d1d0,幅度差分调制采用2DASK,将最高位d3先进行幅度差分编码,差分幅度γk=ak/ak-1与d3的映射关系如表1所示。

表1 2DASK输入幅度比特与γk的关系

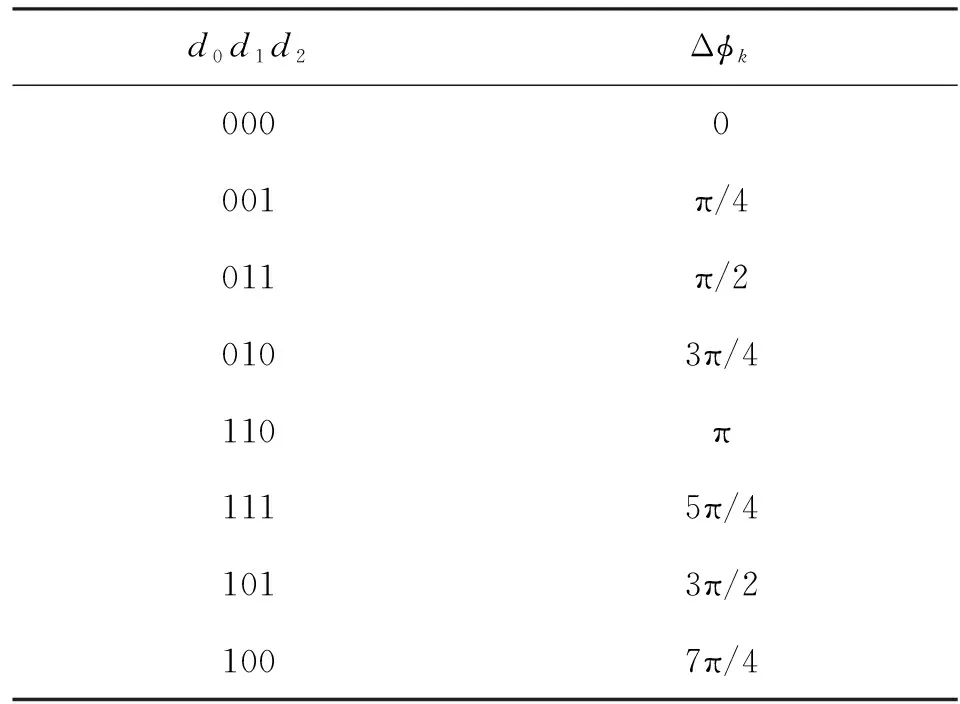

相位差分调制中,采用8DPSK将输入比特的低3位d2d1d0进行相位调制。相位调制比特与相位值对应关系如表2所示,其中Δφk表示当前时刻的绝对相位值与前一时刻的绝对相位值的相对相位差。相位调制比特采用格雷码表示。

表2 8DPSK相位调制比特与相位值对应关系

将调制后的数据通过采用52个子载波的OFDM系统。因为16DAPSK不需要信道估计[16],因此可以将导频信号占用的子载波用于传输有效信号,使得一个OFDM符号中的有效子载波数量由48提升至52,提高了信道利用率。将组帧后的数据经过噪声方差为2σ2、均值为0、传播时延为Delay=[0 2 4 6 8 10]、路径功率分贝值PowerdB=[0 -4 -8 -12 -16 -20]的强多径干扰信道。设接收到的信号值为

Gi=si+ni。

(5)

1.3 16DAPSK软解调算法

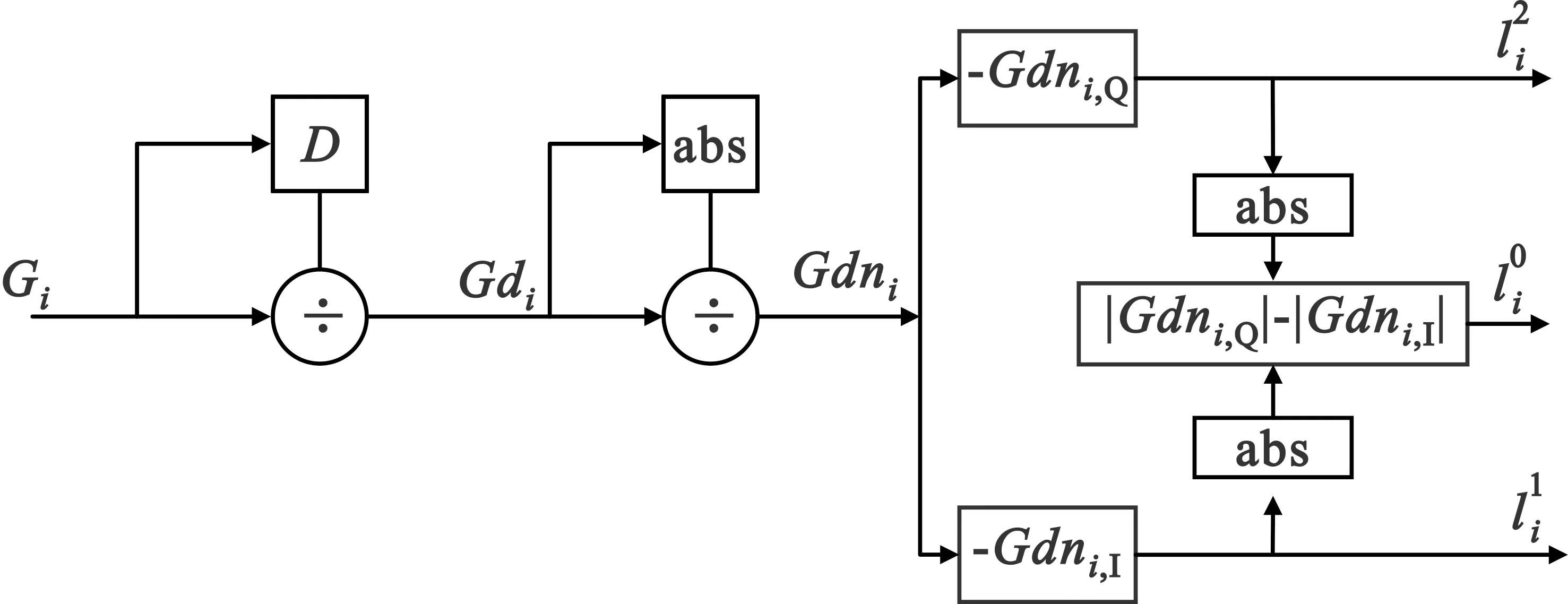

在调制的过程中,由于幅度也参与了差分调制[17],因此接收到的信号包含了幅度分量信息。通过相位软信息提取算法对接收到的信号Gi进行处理,算法框图如图1(a)所示,其中D表示延迟一个OFDM符号长度的时间,abs表示取绝对值。

(a)相位软信息提取算法框图

假设Gi为第i个接收到的OFDM符号,使用公式(6)对接收到的相邻OFDM符号同一子载波上的两个复向量之比做差分解调。

(6)

差分解调后的Gdi依旧包含幅度信息,其中γi表示差分幅度。使用公式(7)对含有幅度信息的Gdi进行相位归一化处理,提取其中的相位信息Gdni。

(7)

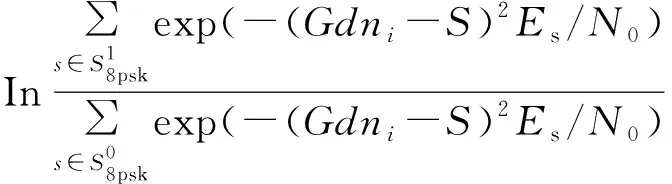

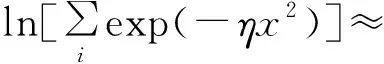

提取出的相位信息由d2d1d0三个比特组成,其中单个比特的对数似然比定义公式如下:

(8)

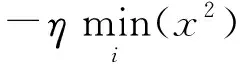

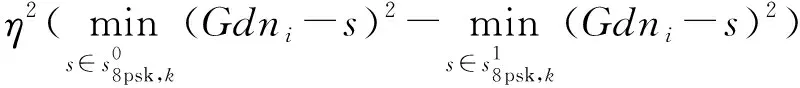

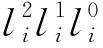

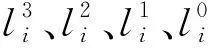

式中:k取0、1、2,表明相位调制中的第k个比特;S代表DPSK调制后的数据点;Gdni代表归一化后的信息。为了降低硬件实现的难度,将公式(8)通过公式(9)进行近似替换:

(9)

式中:η表示常数,在此处代表公式(8)中的Es/N0。近似后的比特软信息如公式(10)所示:

(10)

最后根据归一化后的星座图分布特点得到公式(11):

(11)

(12)

根据公式(6)可知差分后的幅度值γi分布在0.5、1和2的附近。幅度软信息提取算法框图如图1(b)所示。

当γi小于1时,d3位对应的软信息计算公式为

(13)

当γi大于1时,d3对应的软信息为

(14)

2 基于FPGA的设计实现

2.1 LDPC编码的FPGA实现

因为编码矩阵的阶数较大,所以在硬件实现中常用传统的公式法和查找表法占用资源大。CCSDS131.1-O-2中推荐的生成矩阵描述比较复杂,同时循环块过大不利于实现。为了解决上述问题,本文通过对生成矩阵的观察和分析,发现生成矩阵中的校验位部分每一个512×512大小的循环块可以分割成4个128×128大小的循环块,每一个循环块都可以第一行的循环向量得到。本文将每128个行向量提取出来作为循环种子,那么原本6个512×512 大小的循环块变为96个128×128大小的循环块。关于本文所采用的16进制表示的循环行向量种子请扫描本文的OSID码查看。

如图2中所示,采用信源为1 024个比特的“1”,分别通过CCSDS131.1-O-2中推荐的生成矩阵和采用本文OSID码“开放科学数据与内容”中的循环种子产生生成矩阵进行LDPC编码后的仿真图可知,两者图形重合,即本文所给出的循环种子能够正确进行LDPC编码。

图2 LDPC 生成矩阵编码图对比

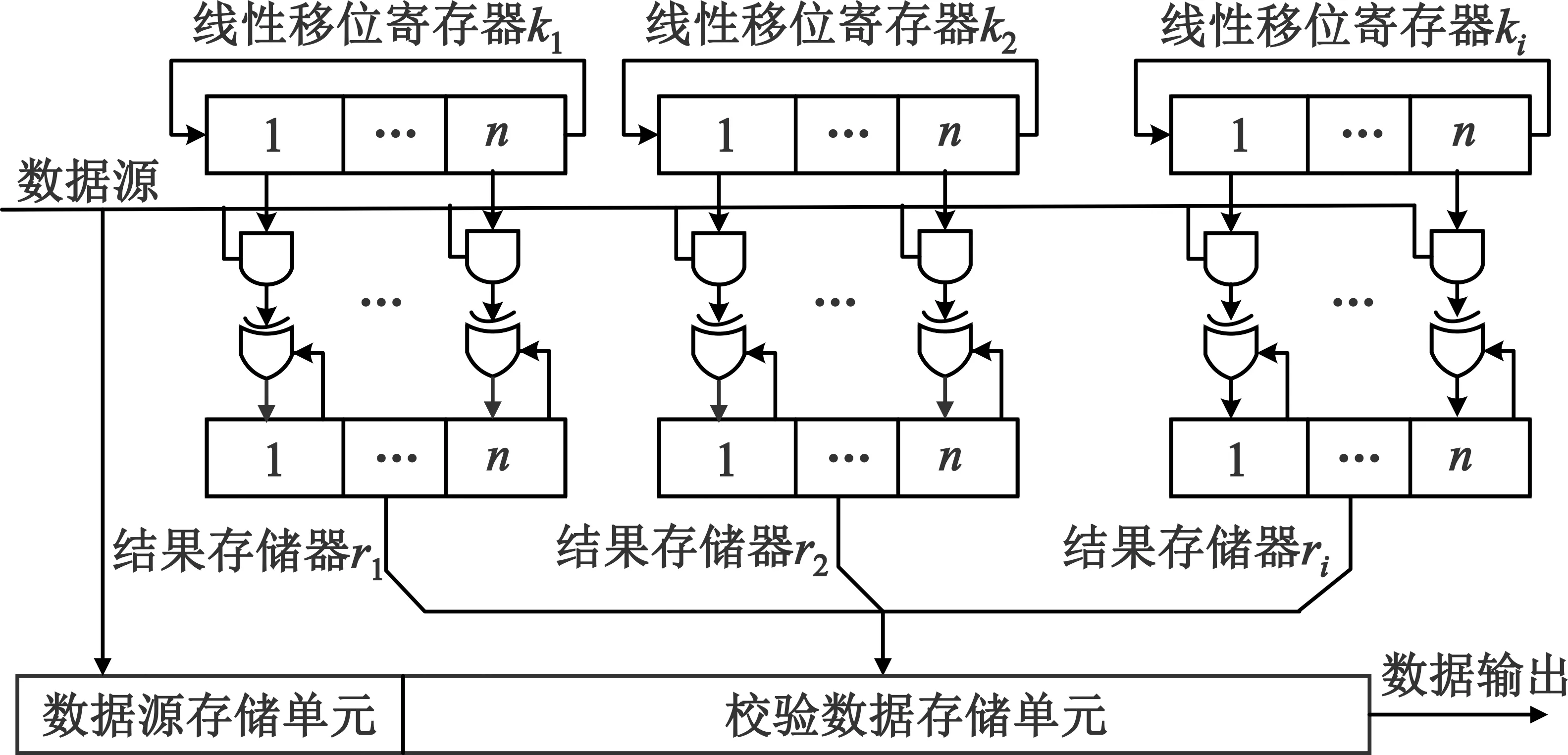

那么,公式(1)中的B将由原来的3×3组512×512的循环块转换为12×12组128×128的循环块。文献[18]中提出了循环编码框图,如图3所示[18]。

图3 单寄存器多位宽的循环编码框图

编码器中包含12个128位宽的循环移位寄存器,即ki=12,ni=128,ri=12。首先将待编码信息向量分割为8个128位宽的子向量。以下为本文提出的解决方案具体实现步骤:

Step1 将循环种子赋值给12个128位宽的移位寄存器,并且将分割好的对应宽度的待编码信息进行初始化。r1~ri分别初始化为128位宽的全零寄存器,同时定义12个128位宽的中间寄存器变量m1~mi。

Step2 循环种子在1~128个时钟周期内,每个周期在寄存器中循环右移1位,同时数据源输入1 b的源数据。将当前时刻输入的源数据与当前时刻的循环种子进行按位与运算,将运算后的结果保存到中间寄存器变量mi。

Step3 在2~129时钟周期内,将Step 1中128位宽的r1~ri的全零向量i分别与Step 2中的m1~mi进行异或运算,将运算结果保存到r1~ri。

Step4 当第129个时钟周期结束时,第1个128位宽的待编码信息编码完成,随后提取编码完成的数据。

Step5 将数据源换为第2个128位长的带编码数据,再次执行Step 2~4。循环执行8次后,编码完成,同时将数据源与校验数据组合到一起得到最终的编码数据。

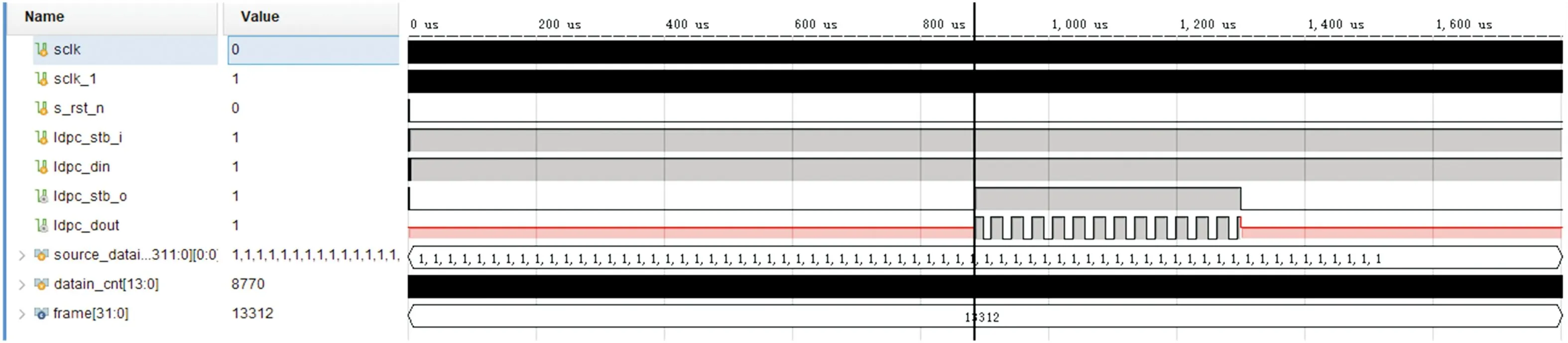

在实现时为了便于观察波形,将数据源全部设置为1,并且一次编码多帧数据。编码后的FPGA时序波形和Matlab 仿真波形如图4所示。对比图4中的(a)和(b)发现,其编码后的波形吻合,由此可知本文提出的编码方法实际可行。

(a)FPGA编码时序图

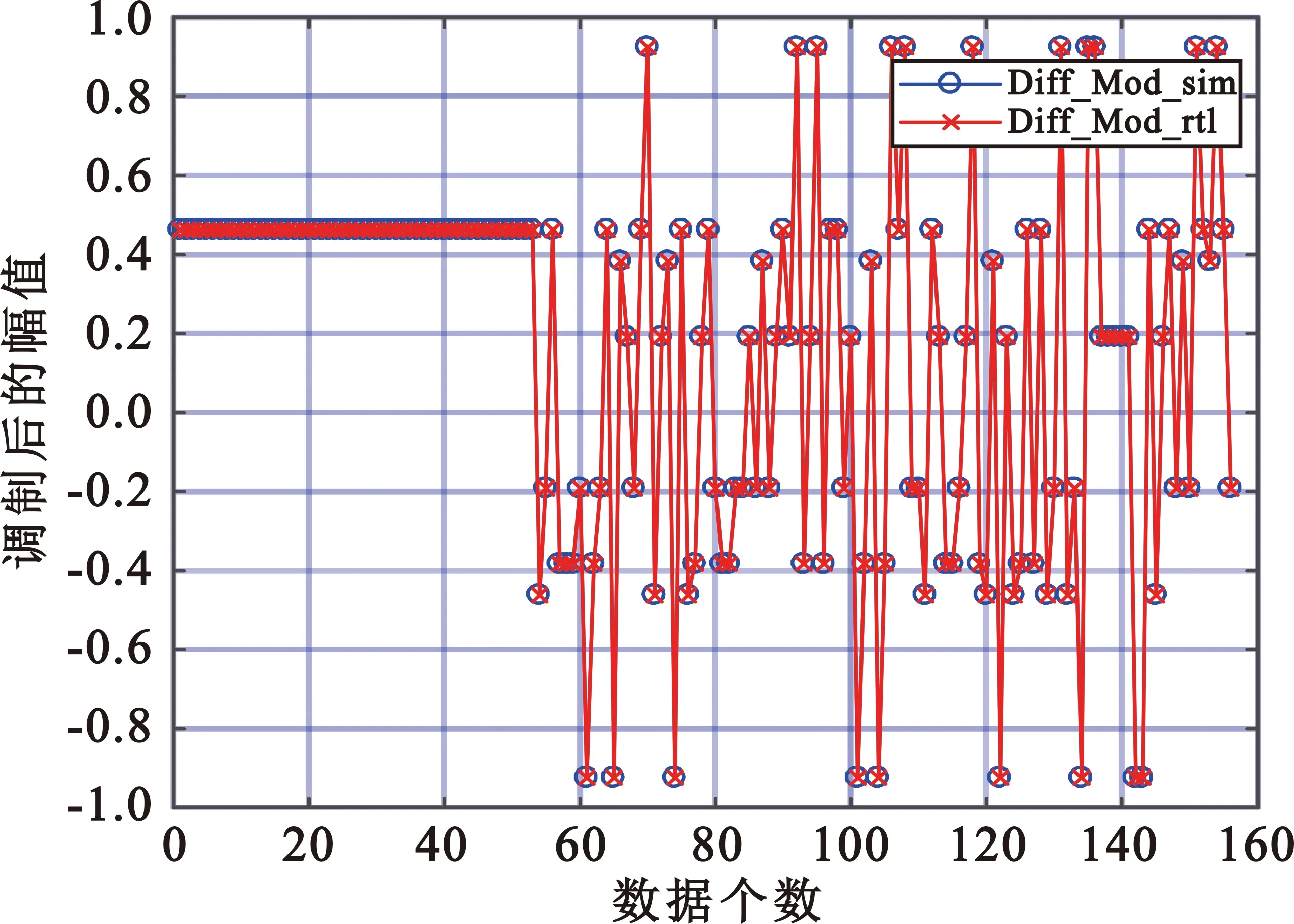

2.2 16DAPSK调制的FPGA实现

16DAPSK调制采用查找表的方式实现,如图5所示。首先将当前时刻到达的d2d1d0与前一时刻的码元状态假设为an-1bn-1cn-1拼接起来作为rom0的地址,其位宽为6 b。然后将本时刻的码元状态anbncn存储到rom0中,其中d2d1d0为rom0地址的高3位,ram输出的数据为地址的低3位。为了实现差分效果,用一个双口ram来存放前一个时刻的OFDM值。之前已经提到过,将传输导频信号的子载波也用于传输有用信号,故一个OFDM符号的子载波个数为52。因此设置双口ram深度为52,采用边读边写模式,读出前一个OFDM符号的值。rom2和rom3存放着绝对相位对应的余弦值,即Q路信号和I路信号。将其以16 b定点数存放,绝对相位比特对应的是rom2和rom3的地址。接下来将d3与前一个OFDM符号相异或得到当前时刻OFDM符号的差分调制值。最后判断差分幅度调制值,当其为1时不移位,为0时右移一位。至此完成16DAPSK调制。

图5 16DAPSK调制FPGA实现框图

16DAPSK调制波形如图6所示。从图6(a)中可以看出16DAPSK调制FPGA实现输出的数据与Matlab 算法仿真输出的数据一致,验证了本文提出的调制方案可行。从图6(b)中可以看出有52个时钟周期时间都是32’h187d3b20,这是因为差分调制的时候需要初始参考信号,即52个初始信号。

(a)16DAPSK调制FPGA与MATLAB的输出对比

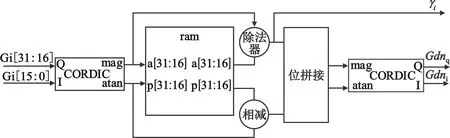

2.3 16DAPSK软解调的FPGA实现

因为软解调中涉及到很多相位计算,所以使用了FPGA中的相角转换IP。软信息解调FPGA实现框图如图7所示,具体步骤如下:

图7 软信息解调FPGA实现框图

Step1 首先将同步处理后的数据送到cordic IP中,计算出相位和幅度值。

Step2 因为要将当前的OFDM符号与前一个OFDM符号做差分解调,所以首先将当前的幅度值与相位值经过一个深度为52的双口ram。

Step3 将Step 1中输出的数据与Step 2中输出的数据,进行幅值相除、相位相减的操作,即完成了对应的公式(6)。

Step4 将Step 3中幅值相除的结果γi用于幅度的软解调。将相位相减和幅度相除的值进行拼接后再次送到cordic IP进行与第一个cordic IP相反的操作,至此完成了对应的公式(7)。

Step5 同样提取出Gdni和Gdnq。最后将提取出的γi通过公式(15)和公式(16)提取出幅度软信息,将Gdni和Gdnq通过公式(14)提取出相位软信息。

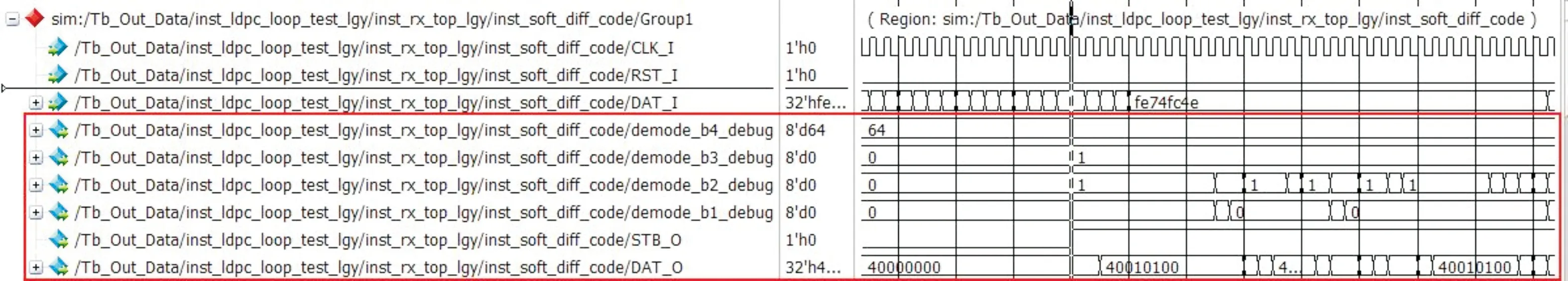

图8所示红色标注的部分为软解调输出的信息,其中demode_b4_debug是幅度d4软解调对应的信息,demode_b3_debug、demode_b2_debug和demode_b1_debu分别对应的是相位d3、d2、d1软解调的信息。

图8 FPGA输出软解调信息波形图

3 仿真结果与FPGA实现资源对比

3.1 不同信道下的仿真分析

仿真系统的子载波数k=52,OFDM符号长度为4 μs,其中保护间隔长度为800 ns,有效数据部分的长度为3.2 μs,子载波间隔为312.5 kHz,信号带宽16.625 MHz,信道间隔20 MHz。为了便于仿真观察,系统采用的每个OFDM符号是52个全为1的数据源,对纠错性能和误比特性能没有影响[19]。最大迭代次数20,每个信噪点200个数据帧。

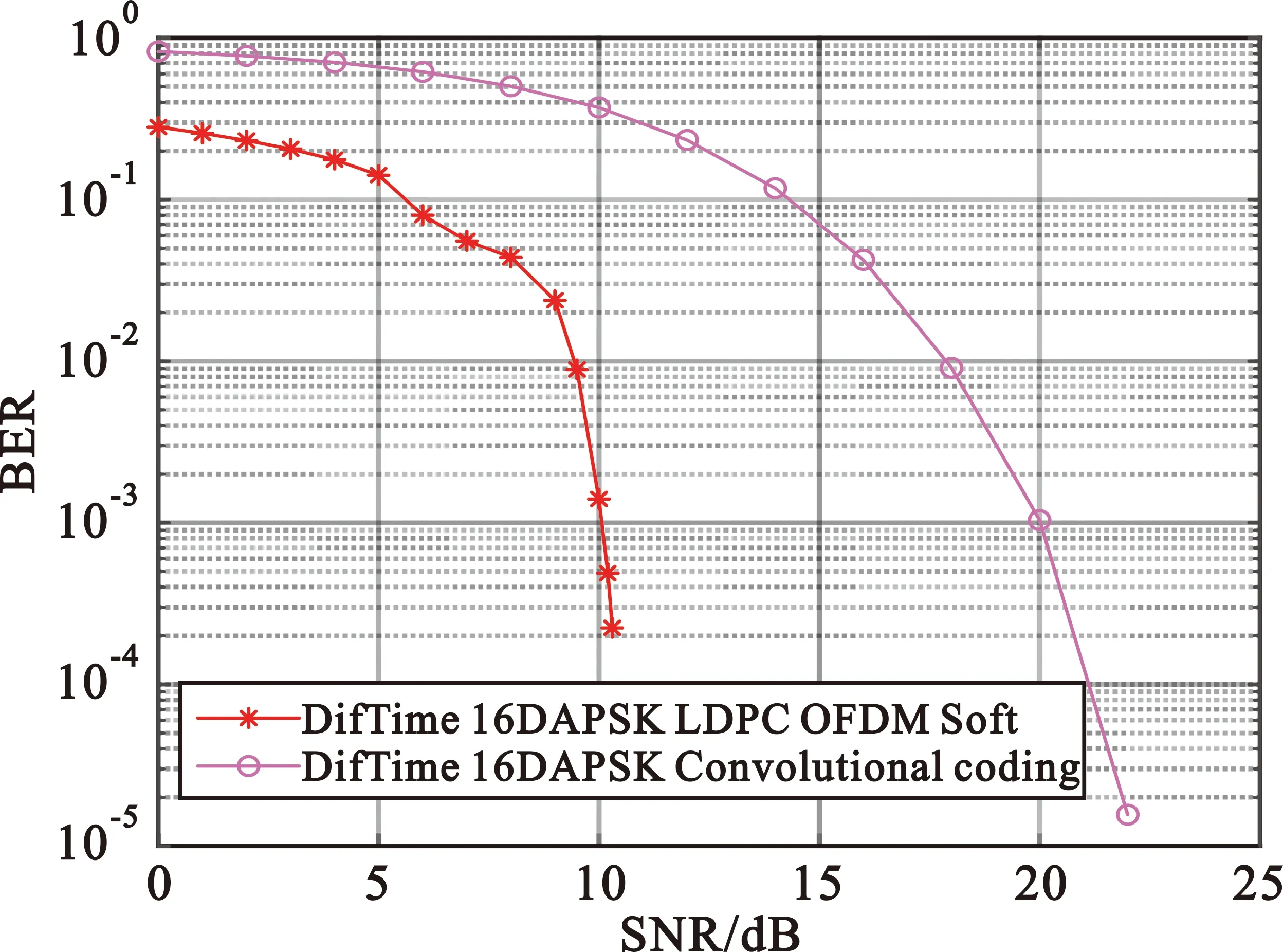

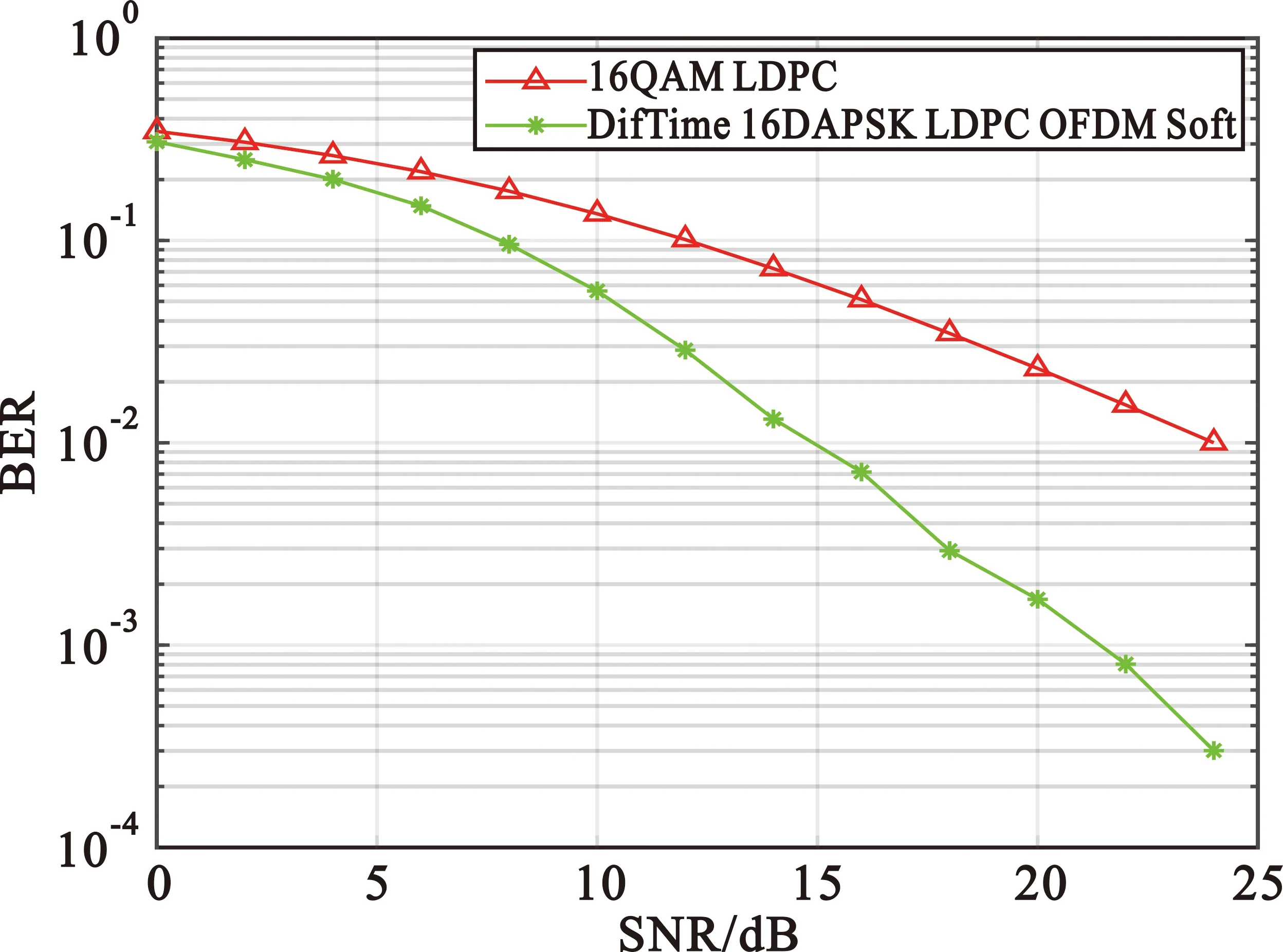

图9(a)给出了在噪声方差为2σ2、均值为0的AWGN信道中的BER仿真结果。可见,当BER为10-3时,与硬解调输出译码相比,采用软输出的LDPC译码可得到约11 dB的性能增益,并且随着信噪比的增大软解调的误码率还在持续降低。图9(b)是采用16QAM调制方式,在没有加信道估计的AWGN信道下两种方案的误码性能的仿真结果。可见当BER为10-3时,本文所提出的方案相比16QAM调制联合LDPC编码且不加信道估计的方案有约1.9 dB的性能改善。文献[20]中,给出了仿真条件为AWGN信道,最大迭代次数为10和50时IEEE802.11a 协议下采用码长为1 536、码率为1/2的LDPC信道编码联合16QAM数字调制的误码率[20]。在迭代次数为50、误码率为10-4时,相比本文所提出的方案迭代20次有约4 dB的增益,但是从文献[20]中给出迭代10次的结果来看,本文所提出的方案有约4 dB的增益。

(a)LDPC信道编码对误码率性能的影响

设置传播时延为Delay=[0 2 4 6 8 10]、路径功率分贝值PowerdB=[0 -4 -8 -12 -16 -20]。以上设置的传播时延和路径功率的参数相比于多径信道模型中的多径干扰更加强烈,更接近实际环境。图10(a)给出了在此强多径干扰信道下的BER仿真结果,可知当BER为10-2时,时域差分16DAPSK联合LDPC编码方案相比16QAM调制联合LDPC编码且不加信道估计的方案有7~8 dB的性能增益。

(a)强多径(6径)信道下误码率对比

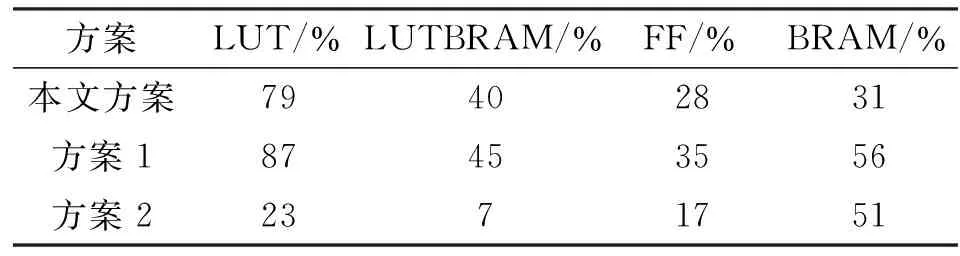

3.2 ZEDBOARD硬件资源开销对比

在IEEE802.11a物理层协议下,分析基于Xilinx ZEDBOARD硬件平台采用不同方案实现通信系统的硬件资源占用情况。表3为三种方案ZEDBOARD硬件实现时Vivado给出的硬件资源占ZEDBOARD总资源的百分比,表中将16QAM调制联合LDPC编码称为方案1,将16DAPSK联合卷积编码、维特比译码方案称为方案2。

表3 硬件资源占用对比

通过表3可知,本文所提出的16DAPSK联合LDPC编码、Min-Sum译码方案,在资源占用上要比采用16DAPSK联合卷积编码(2,1,7)、维特比译码方案大很多,通过图10(b)数据输出误码率图对比可知,在强多径干扰信道中误码率为10-2时,时域差分16DAPSK联合LDPC编码方案比采用采用16DAPSK联合卷积编码(2,1,7)、维特比译码方案有6~7 dB的误码性能增益。

Vivado 中当某项资源占用太多时,就会导致综合电路时布局布线不通过。表3中的方案1表示在IEEE802.11a物理层协议下,采用16QAM联合LDPC串行编码、Min-Sum译码方案的资源占用情况。但是为了能综合出电路,在信道估计的取样长度和精度方面都做了很大的牺牲。将本文提出的方案与方案1对比可知,在硬件实现中LUT资源节省8%,LUTBRAM资源节省5%,FF资源节省7%,BRAM资源节省25%。

3.3 室内环境测试

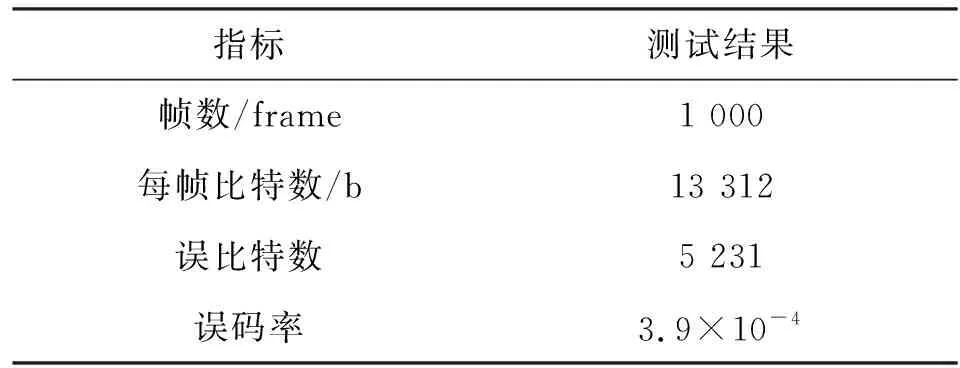

测试系统的硬件平台为XILINX ZEDBOARD 7Z020,射频端采用AD-FMCOMMS2-EBZ评估板。本振设置为2.4 GHz,频带带宽为20 MHz,天线发射功率为5 dBi,每一帧数据传输13 312 b。在FPGA端编写错误统计模块来统计错误比特,通过Vivado软件进行板级数据捕获和误码率统计。测试条件为室内多径环境,测试结果如表4所示。

表4 误码率统计

4 结束语

本文提出了基于OFDM系统16DAPSK软解调联合LDPC编译码的通信方案,仿真结果表明,该方案在AWGN信道中相比16DAPSK硬解调和16QAM调制联合LDPC编码且不加信道估计的方案,在误码率为10-2时分别有1.9 dB和7 dB到8 dB的性能增益;在强多径干扰信道中,误码率为10-2时相比于16QAM联合LDPC且不加信道估计的方案有约8 dB的性能增益;在硬件实现中相比采用16QAM联合LDPC串行编码、Min-Sum译码方案LUT、LUTRAM、FF和BRAM资源分别节省8%、5%、7%、25%,同时在室内实际测量时的误码率可达到10-4数量级。

接下来将着重研究和优化该通信方案在高速移动环境下误码性能,并通过FPGA进行设计和实现。