电磁故障注入攻击综述*

2022-01-25褚潍禹欧庆于

褚潍禹,欧庆于,付 伟,吴 童

(海军工程大学,湖北 武汉 430033)

0 引言

故障注入攻击[1]作为旁路攻击的一个重要分支,它通过在执行加密算法期间引入故障扰动,来获得故障密文输出,进而通过分析获取密钥等相关敏感信息。故障注入攻击的核心目标之一,是在不破坏集成电路功能的情况下实现对其内部重要电路及其数据的翻转、篡改,所采用的手段主要包括光故障注入[2]、电磁攻击[3]、温度变化[4]以及电压和时钟毛刺[5]等。

其中,电磁故障注入通过电磁注入探头上产生的高压瞬态电磁场,在目标芯片中产生瞬态感应电压和电流,从而达到引入干扰信号,改变芯片内部逻辑门电压,并引发数据翻转等软故障的目的。与其他故障注入方法相比,电磁故障注入无需去除芯片封装就能对芯片的局部区域进行攻击,且当前缺乏有效的防护措施。因此,电磁故障注入近年来被攻击者广泛应用[6]。

本文主要从电磁故障原理、攻击方法、故障模型和防护手段几个方面进行综述。研究结果对理解电磁故障注入机理以及后面继续深入研究电磁故障模型以及防护具有重要意义。

1 电磁故障注入原理

电磁故障注入的基本原理是电磁感应现象。根据法拉利电磁感应闭合电路回路中磁通量的变化产生感应电动势和电流的现象,可以利用线圈产生变化的电磁场,并通过近场耦合方式在目标芯片中产生感应电动势和电流,最终达到注入故障的目的。设线圈为线圈匝数为N,其表面积为S,流经线圈的电流为I,通过线圈产生的磁场感应强度为B,线圈表面与磁场线之间的夹角为θ。则该线圈的磁通量φB表示为:

又设线圈中介质的磁导率为μr,线圈的半径为r,线圈圆心到轴线上点的距离为z,则线圈轴心上一点的磁感应强度可表示为:

当线圈靠近目标芯片时,根据电磁感应定律,目标芯片中产生的感应电动势可表示为:

将式(2)代入式(3)可得:

由式(4)可知,在线圈匝数N一定的情况下,被攻击目标上感应电动势的大小受以下几个方面的影响:线圈与目标之间的角度θ和距离z;通过线圈的电流变化率dI/dt;线圈的表面积S;线圈中介质的磁导率μr。

此外,为提高注入的精确度,往往需要将电磁探头放置于目标芯片特定区域上方。电磁探头产生变化较快的磁场,变化的磁场通过目标内部易受磁场影响的器件而产生感应电动势和感应电流,进而影响目标的正常工作。

2 电磁故障注入攻击实施

目前,主要有两类电磁故障注入方法。第一类是基于瞬态电磁脉冲的故障注入,其通过为线圈两端施加瞬态的电压脉冲信号,产生瞬态的电磁场,从而在目标芯片中引入瞬态感应电压和电流;第二类是利用谐波辐射方式,对目标芯片中关键信号线耦合正弦干扰信号,并通过调整耦合信号的频率达到数据翻转和篡改目的。

2.1 基于瞬态电磁脉冲的故障注入

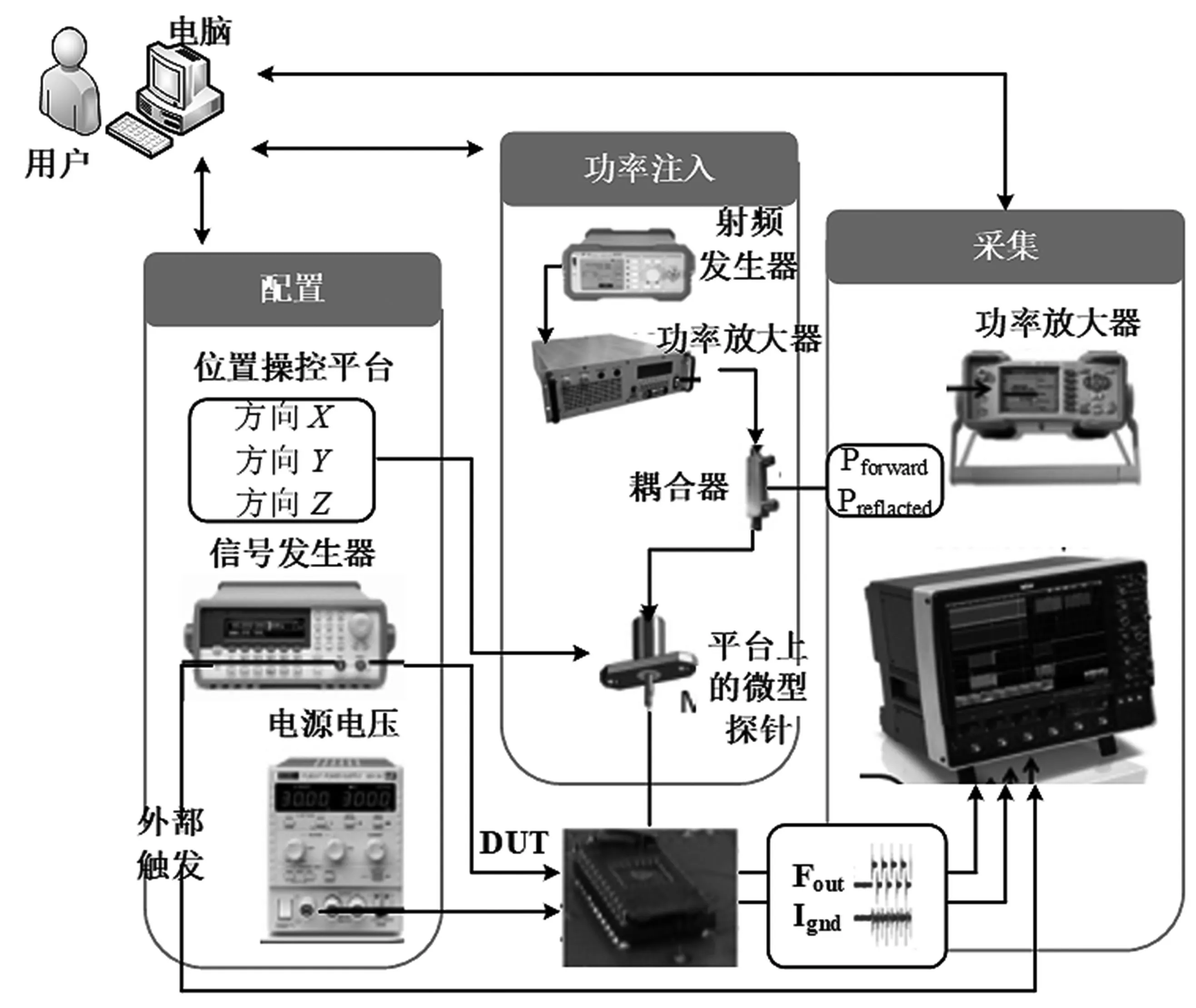

电磁脉冲故障注入产生的瞬态电磁场会对待攻击芯片的内部引入瞬态毛刺信号。典型的电磁脉冲故障注入实验平台如图1 所示,这种类型的电磁故障注入平台可对执行敏感操作的加密模块或处理单元注入瞬态故障[7]。该实验平台主要组成设备有:一台个人电脑,一台高压脉冲发生器,一个电磁探头,一个XYZ方向移动平台,一个待攻击芯片和一台示波器。待攻击芯片放置于XYZ方向移动平台上,通过个人电脑控制和操作实验平台中的各个设备,并使用串口或智能卡读卡器实现外界与待攻击芯片之间的通信。

图1 电磁脉冲注入实验平台

Kyechong 等人在文献[8]中设计并制作了5 种不同尺寸的独立反相器和一种级联互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)反相器,研究了来自大功率微波源的电磁干扰对单个和级联CMOS 反相器静态特性的影响。他们将功率范围为0~24 dBm(1.0~251.2 mW),频率范围为0.8~3.0 GHz的微波信号直接注入到反相器的输入端,并分别观察他们在有微波干扰和无微波干扰下的工作情况。通过试验他们发现两种情况下器件的工作情况产生了显著变化,这种变化是由于在微波干扰下反相器的N 型金属-氧化物-半导体(N-Metal-Oxide-Semiconductor,NMOS)和P型金属-氧化物-半导体(P-MOS)的电流驱动能力的不对称大幅增加,改变了拐点电压和输出电压。此外,他们还观察到由于跨导(gm)的显著降低,增益在1.5 μm 制式器件上减少了6~10 倍;在更小的0.5 μm 制式器件上减少了18~24 倍;在微波干扰下器件的敏感性增强。同时噪声容限严重降低了系统的抗噪性,在级联反相器运行中产生了错码。

Dehbaoui 等人[9]研究了在高级加密标准(Advanced Encryption Standard,AES)算法的微控制器和现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)上进行电磁脉冲故障注入,他们通过脉冲发生器将具有5 ns 恒定的上升和下降过渡时间的低抖动(小于50 ps)电压脉冲发送到线圈,进行电磁脉冲故障注入。为了确保每次只干扰到目标的一小部分,他们还使用了直径为500 μm的磁探针。针对微控制器上的故障注入,由于电磁脉冲发生器能够以纳秒的精度改变脉冲的时间,而通过改变脉冲注入时间可以跳过本应在电磁脉冲期间执行的指令,因此可以使AES的整个字节内部出错。对于FPGA 上的电磁故障注入,他们实现了单比特和多比特故障注入到AES 计算中。通过实验他们还发现电磁脉冲故障的局部效应,针对不同位置的电磁脉冲故障注入可能会得到不同的结果。

Ordas 等人[10]在电磁脉冲故障注入实验中发现,电路中的D 触发器对电磁故障注入特别敏感。他们将不同的电磁脉冲注入到具有640×8 bit的D 触发器(640 字节)的大型先进先出(First Input First Output,FIFO)FPGA 上,发现在使用瞬态电磁脉冲来进行电磁故障注入实验时,当电磁脉冲功率达到一定阈值时,可以影响D 触发器的采样过程,且当脉冲功率更高时,可触发D 触发器的复位或置位信号,从而引发采样故障。他们还发现D 触发器对高电平和低电平的敏感性是不同的。在文献[11]中,他们通过进一步的对D 触发器的研究,提出了采样模型。

Elmohr 等人在实验中探索了电磁脉冲对嵌入式处理器的影响,并在文献[12]证明,电磁脉冲注入可以导致320 MHz RISC-V 处理器上多条指令的跳过故障,从而使其容易受到更大范围的攻击。此外,他们在ARM Cortex M0 和RISC-V 嵌入式处理器上的实验结果表明:在较低的电源电压和较高的时钟频率下,电磁脉冲注入更容易产生影响。

2.2 基于电磁谐波的故障注入

电磁谐波故障注入能通过电磁耦合对芯片内部模块引入寄生信号和谐波电流。在进行电磁谐波故障注入时,电磁探头不需要与芯片接触,这种攻击方法很难被芯片内嵌的电压、时钟等防护措施检测到。图2 为一个典型的电磁谐波注入平台。该实验平台主要由控制平台、谐波功率注入和数据采集3部分组成,通过个人电脑可实现对整个实验平台的操控。与电磁脉冲故障注入实验平台不同,电磁谐波故障注入所采用的信号发生器不要求其能产生瞬态的高压脉冲信号,而是需要其能产生频率、幅值可调的高频正弦信号,且产生的正弦信号需经功率放大器后施加于电磁探头两端。

图2 电磁谐波注入实验平台

Poucheret 在该平台上使用一根30 μm 长,探头两端直径分别为200 μm 和10 μm的细钨杆用来进行电磁谐波故障注入[13]。由于顶端的直径较小,可以将探头发射的90%功率集中在距尖端10 μm的直径范围内进行局部和密集的注入攻击。通过对4 个环形振荡器注入的实验,结果表明环形振荡器的频率与探头注入的功率呈现正相关关系,随着探头注入功率的增加,环形振荡器的频率呈现近似线性地增加,进而产生故障。

更进一步,Bayon 使用同样的设备在FPGA 上分别对4 个由3 个反相器组成的环形振荡器和真随机数生成(True Random Number Generator,TRNG)进行了电磁谐波故障注入攻击[14]。通过对4 个环形振荡器进行高频的正弦波,4 个环形振荡器呈现出相互锁定的情况并且相位差呈现正弦的趋势。他们后续在FPGA 上对50 个环形振荡器组成的TRNG进行了电磁谐波攻击,实验表明通过不同频率的电磁谐波攻击,可以动态地控制TRNG的输出偏置。

2.3 两种故障注入方法的比较

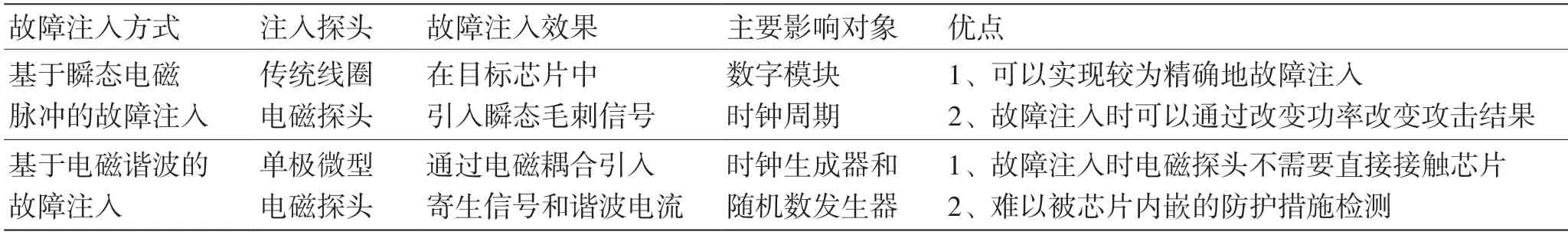

在进行电磁故障注入实验时,基于瞬态电磁脉冲的故障注入可以对目标芯片进行较为精确地局部瞬态故障注入,特别是芯片内部的数字模块一般是由时钟控制的,基于瞬态电磁脉冲的故障注入可以实现可控的方式对数字模块特定时钟周期引入故障。而基于电磁谐波的故障注入可以通过电磁耦合引入寄生信号的谐波电流,进而影响目标芯片上时钟生成器和随机数发生器等。基于电磁谐波的故障注入在故障注入时可以在特定的位置注入较强的电磁功率信号而不会引起芯片内部电压突变,探头也不需要与芯片直接接触。表1 总结和比较了两类电磁故障注入的不同。

表1 两类电磁故障注入的比较

3 故障分析模型及防护手段

目前学术界对电磁故障注入攻击的机理仍无定论。现有的几种电磁故障注入机理的模型主要为时序故障模型[15]、采样故障模型[12]、充放电模型[16]以及电源网络耦合模型[17]。时序故障模型认为电磁脉冲和电源-地面网络之间的耦合增加了延迟,并最终导致设置时间约束违反。采样故障模型认为电磁脉冲在D 触发器的建立时间期间扰乱了数据,在一段时间内暂时改变电路中几个节点的电压,在此时间间隔后,芯片迅速恢复到原来的状态。充放电模型指出电磁脉冲改变了电容的充放电时间,从而产生了故障。电源网络耦合模型从底层进行建模并指出在电磁脉冲攻击下,由于闭合的电源电压端和接地端回路中产生了感应电动势,从而对电路产生了影响。以上几个故障分析模型对理解电磁故障注入进攻有一定的帮助,但对故障对芯片的影响还需要进一步探究。

针对电磁故障攻击的防护,目前还没有特别有效的手段。Jean-Jacques 提出了几种通用防护手段[18]。首先是减小电磁场强度,其旨在利用制造芯片的上层金属层来较大程度降低电磁场的辐射强度;但由于受限于芯片的最大尺寸,所用金属层的厚度一般不会过大。其次是法拉第笼,将芯片放置于法拉第笼内是防止芯片遭受电磁辐射的有效方法;但是,通常芯片需通过导线与电子设备的其他部分连接来实现通信,这样就必须在法拉第笼上留下对应的走线孔,而这些孔将会允许特定波长的电磁波逃离法拉第笼,使得法拉第笼的构建较难实现。最后是双线逻辑,双线逻辑是指使得每条传输关键信号的信号线或总线旁边总有一条与传输方向和传输信号电平均相反的信号线。当攻击者试图进行电磁故障注入时,双线逻辑的走线所产生的电磁场会相互抵消,通过这样的方式可以降低导线的电磁辐射并削弱电磁攻击的强度。

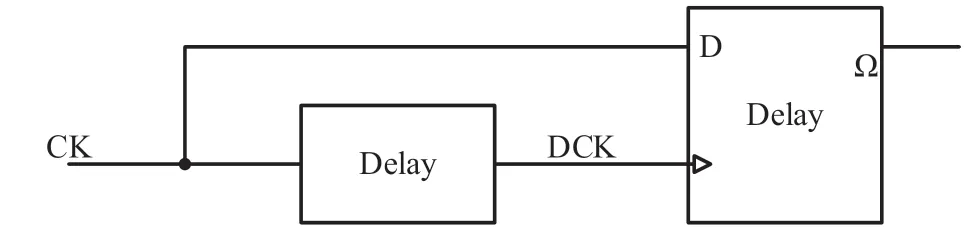

除了通用的防护手段,研究人员也探索了针对特定模型的防护手段。2014 年Zussa 等[19]针对时序故障模型设计了一个电压故障检测器,如图3 所示。在正常信号中增加一小个保护时延用于检测因故障注入导致的电路中关键路径的时延变化,如果信号通过保护时延后的总时延大于设计的阈值则会触发警报。实验表明电磁故障注入时的故障率最高可达32%,而实际产生故障的检测可以达到91%。Deshpande 等人则设计了双互补触发器[20]用于检测电磁故障注入,如图4 所示。当电路正常工作时Main-FF(MFF)部分和Shadow-FF(SFF)部分保持互补值,若电磁故障改变了其中一个触发器的值,使得两个触发器的值相同,就会产生警报信号。通过在FPGA上AES-128 进行注入攻击,他们发现电路的电磁故障注入时故障检测为7%,产生故障的故障的检测率可以达到100%。上述针对特定模型的防护手段目前基本只在FPGA 平台上进行过测试,而且对电磁故障的检测也没有全部达到100%,在其他平台如专用集成电路(Application SpecificIntegrated Circuit,ASIC)等还需要进行进一步测试。

图3 时序故障模型的电压故障检测器

图4 双互补触发器

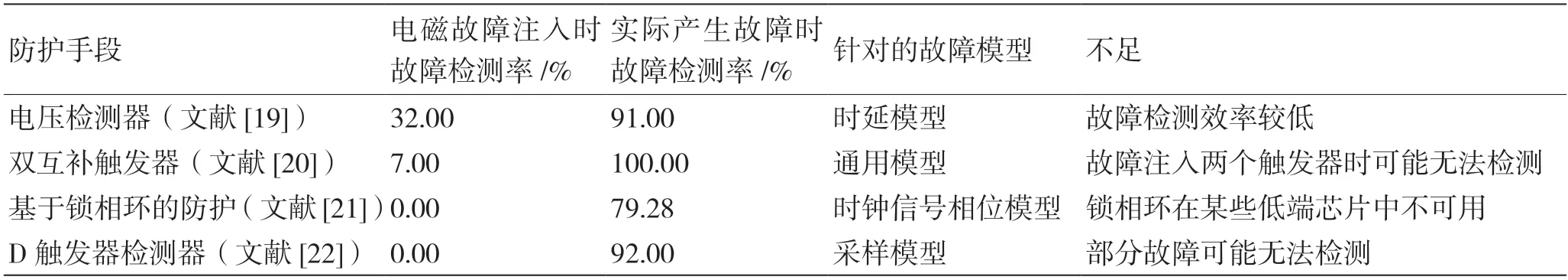

除了上述几种,还有一些其他的特定结构的防护手段,在表2 中进行了比较和总结。

表2 几种特定防护结构的比较和总结

4 未来的研究方向

电磁故障注入作为故障攻击的一个分支因成本较低、控制性较好,并且攻击时可以轻易穿透各种物理封闭而受到广泛关注。尽管目前对电磁故障注入攻击的研究已经取得了一定的进展,但总体上看还有许多方面值得进一步研究。

4.1 故障模型的进一步细化

虽然目前研究人员提出了不同的故障模型,但各个故障模型并不能全面解释电磁故障注入攻击对目标芯片产生的具体影响,下一步可以对现有的模型进行优化,从而更好地探究故障注入对目标芯片的影响。

4.2 对其他微处理器进行攻击

随着ARM 及RISC-V 等微处理器的在日常生活中的广泛应用,其安全性也越来越受到人们的关注。目前已经有部分研究人员进行了相关的电磁故障注入攻击实验,并进行了初步的研究。下一步在进行攻击实验的基础上,进行相应的统计实验及分析。

4.3 对动态随机存取存储器等的攻击

作为计算机系统的主存储器,动态随机存取存储器(Dynamic Random Access Memory,DRAM)中存储着许多敏感的信息,如系统运行的指令、安全启动的引导程序等等。随着网络与信息安全问题的日渐突出,对DRAM的在现有故障攻击技术下的安全性研究对计算机系统的安全性具有重要意义。

5 结语

本文综述了电磁故障的原理和攻击方法,介绍了不同平台的实验结果,并描述了几种故障模型以及防护策略。在攻击方法方面介绍了电磁脉冲和电磁谐波两种方法以及他们典型的实验平台,在防护策略方面介绍了几种通用的防护手段以及应对特定模型而设计的特定结构。其中,对故障模型的研究可以作为下一步的研究方向进行深入探索。