半导体工序为什么如此复杂?

2022-01-16桫椤

桫椤

技术流网友经常讨论国产芯片的制造为何如此之难,实际上半导体的前段工序、后段工序以及封装是一个复杂的过程,今天我们来了解一下。

虽然半导体的前段工序中有500~1000(甚至更多)道工艺,但是工艺却很简单

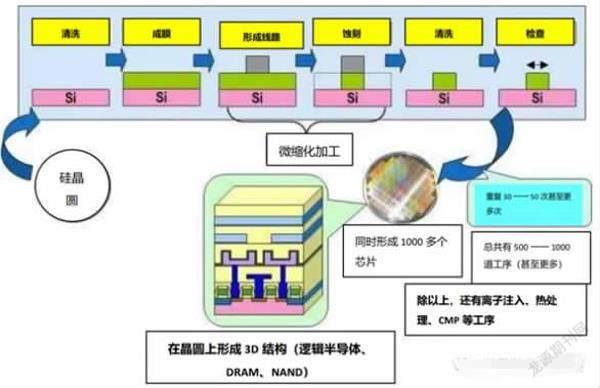

首先以直径为200~300毫米的硅晶圆(Silicon Wafer)为基板,进行以下规定的工序(反复30~50次,甚至更多):清洗→成膜→光刻形成線路(Lithography Patterning)→蚀刻(Etching)→抛光(Ashing)或者清洗→检测。除以上工艺之外,还有离子注入、热处理、CMP等工艺。

通过前段工序,在硅晶圆上形成晶体管、电容、排线等的3D 结构。此外,在硅晶圆上同时形成约1000个芯片(Chip)。前段工序中使用的主要设备,占比较高的有涂布显影设备(Coater & Developer,92%)、热处理设备(也被称为“纵型扩散炉”,93%)、单片式清洗设备(63%)和批量式(Batch)清洗设备(86%)、测长SEM(80%)等。

前段工序中使用的主要材料的企业占比

亚洲企业在硅晶圆、各类光刻胶、各类CMP粉浆、各类高纯度溶液等产品中的占比极高。欧美方面,AMAT(美国应用材料)、Lam Research(Lam,泛林集团)、KLA(科磊)、ASML(阿斯麦)四家欧美企业是如何研发设备的呢?首先,他们根据市场(Marketing),把握需求(Needs),各类设备在最初研发阶段都有科技(Science)成分存在。在需求和科技的引领下,根据强有力的自上而下的领导方式,构架整个设备,且多以模组化的形式呈现。

在研发设备的各个阶段,进行模拟实验。同时,将技术和技巧“软件化”,融入设备。最后,将以上元素汇聚于一体,生产出拥有全球标准的设备。

因此,可以看出,欧美社会的“坚硬强势”的“契约精神”被反映得淋漓尽致。总体而言,大部分亚洲设备厂家是为各个半导体厂家“量身定制”设备,而欧美的设备厂家基本上是仅生产一种具有全球标准的设备。

亚洲企业在液体、流体等形状不固定的材料方面占有较高比例,而欧美厂家在使用光、电子束(Beam)、等离子的真空设备方面占有较高比例的原因正在于此。

欧美人是理论先行。在研发初期,进行充分的讨论,然后才固定一条方针。在此基础上,创造规则(Rule)、情节(Story)、逻辑(Logic)。反过来说,欧美技术人员的下属们比较笨拙,做实验的水平也不高。

接下来我们讨论后段工序。随着3D封装(3D Packing,以下简称为“3D IC”)时代的到来,在前段工序、后段工序(封装)中间,出现了转变。

在2010年前后,半导体前段工序处于绝对优势。其中,光刻技术人员是所谓的“香饽饽”,甚至出现了以下言论:“没有光刻,就不会有蚀刻”;“只要做好光刻,就会通过后面的工艺自动做成晶体管”。

前段工序和后段工序的转移

然而在现代社会的尖端半导体中,各家Foundry代工厂(如TSMC等)、英特尔和三星电子等IDM(Integrated Device Manufacturer,垂直整合型)厂家、OSAT(Outsourced Semiconductor Assembly and Test,外包半导体产品封装和测试)厂家都竞相开始研发3D IC。

面对激烈的市场竞争,终端消费电子产品对“轻、薄、短、小”的外形尺寸以及多元功能的追求不曾停歇,目前封装业研发重点在于把厚度做最大利用,3D IC技术是目前唯一能满足上述需求的关键技术,这项技术是利用 3D IC堆叠、矽穿孔、TSV等技术将芯片整合到效能最佳、体积最小的状态。

就3D IC研发而言,最先进行研发的是封装设计。融入3D IC的SoC(System on Chip,系统级芯片)、GPU、DRAM等芯片已经实现商品化。要生产出以上“商品”,需要前段工序的技术要素。

在前段工序中,在单颗晶圆上形成1000个左右的芯片(Chip),而在后段工序中,通过裁断(Dicing)工艺,将一颗颗芯片(Chip)切割出来,封装到IC载板上,再进行各类测试,最终完成产品。

与前段工序不同,后段工序中相对复杂的是有机基板(一般为有机基板,用于搭载芯片,据说因用途、企业不同而不同)。即,后段工序中没有像前段工序中的硅晶圆(Silicon Wafer)那样的全球标准,因此,要理解后段工序是有难度的。

此外,与前段工序的技术节点(Technology Node)相比,后段工序的设计规则(Design Rule)有三位数的差异(前段工序为纳米级、后段工序为微米级)。

就目前而言,台积电(TSMC)在前段工序中已经开始量产N5(5纳米级)节点,而后段工序中使用的有机基板的设计规则还停留在5微米。此外,台积电已开始使用其 N3(3 纳米级)制造工艺生产芯片。像往常一样,这家芯片合约制造商及其合作伙伴需要几个季度的时间来完善技术和设计,然后才能进入大批量制造 (HVM)。

台积电在其位于台南附近科学园的Fab 18 中启动了 N3 芯片的试生产,由于新工艺的周期时间超过100天,台积电制造的第一批N3芯片将于2023年初出货。台积电的N3 制造技术是代工厂的下一代节点,专为智能手机和高性能计算 (HPC) 应用程序而设计,与台积电通常首先解决移动设计的策略背道而驰。新工艺将积极使用“超过20层”的极紫外光刻 (EUVL),并对现有N5节点进行实质性改进。台积电承诺性能提升10%到 15%(在相同的功率和晶体管数量下)、高达30%的功耗降低(在相同的时钟和复杂度下)、高达 70% 的逻辑密度增益和高达20%的SRAM密度增益。

那些完全沉浸于“唯微缩化是最重要的工艺”想法的前段工序的技术人员看到这种情况后,或许会认为“半导体后段工序也就是MEMS(微机电系统)的水平”。其实,这种想法不严谨,如果后段工序中的有机基板的设计规则可以紧跟前段工序的微縮化发展,那么,封装的最终产品显然能卖到高价,对销售大有益处。

就后段工序的工艺而言,既有OSAT(Outsourced Semiconductor Assembly and Testing,外包半导体产品封装和测试)封装的情况,也有芯片厂(如英特尔)自行封装的情况,为了易于读者理解,我们假设全部由OSAT进行封装。

(1) 首先,由英特尔决定把芯片(Chip)封装在哪家公司的基板上、英特尔决定基板的原材料。

(2) 被英特尔选定的味之素Fine-Techno、三菱气体化学等基板材料厂家把基板材料供给由英特尔选定的基板厂家(揖斐电电子、新光电气)。

(3) 揖斐电电子、新光电气根据英特尔的规格要求,生产有机基板,然后将基板出货给日月光(ASE)、安靠(Amkor)等OSAT厂家。

(4) OSAT再采购各类用于后段工序的设备、材料,如DISCO(迪思科)的切割设备(Dicer)等。

(5) 英特尔再把在前段工序中完成的晶圆(Wafer)交给OSAT。

(6) OSAT利用后段工序的各类设备、材料,为英特尔封装、测试各类最终产品。

如上所述,经过前后段工序各个设备的协调配合,走完流程,一块处理器(Processor)诞生了。