基于位流回读的硬件木马检测方法

2022-01-13万旺张红旗张大宇张松王贺

万旺,张红旗,张大宇,张松,王贺

(中国航天宇航元器件工程中心,北京 100094)

0 引言

近年来,针对硬件木马[1],提出了诸多测试方法,但大体上可以分为逆向工程[2]、旁路分析[3-4]和逻辑测试[5]等几类。对于专用集成电路(ASIC)而言,逆向工程可以通过开封、清洗等操作对IC内部结构进行分析,旁路分析可以通过分析功耗去检测,而逻辑测试亦可以通过功能测试去验证,在特定的情况下,这些方法都能够对硬件木马做出适当的识别。然而,对于现场可编程逻辑门阵列(FPGA:Field Programmable Gate Array)而言,由于其内部是大量的逻辑模块,而其功能是根据需求进行配置的,所以上述的几种方法往往很难对FPGA设计中的硬件木马做出判断。对此,也有人提出了门级网表的测试方法[6],然而该方法也只能防止设计时的隐患,随着StarBleed漏洞的揭露[7],FPGA中在线运行的设计被植入硬件木马的可能性已无法被忽视。而针对这种方式植入的硬件木马,至今尚没有提出有效的解决措施。

因此,本文提出基于位流回读[8-9]的硬件木马检测方法,通过位流对比分析,可以有效地检测出FPGA设计中植入的硬件木马。该方法的主要难点在于测试人员必须深入地了解相应器件的配置及接口等信息,并通过相应的EDA工具进行必要的软硬件协同设计才能够实现该测试过程。本文将对Xilinx系列FPGA的具体配置及接口信息进行分析,并在VC707评估板上进行简单设计以验证该方法的合理性。

1 FPGA配置

FPGA的配置是指将设计生成的位流加载到FPGA配置存储器中,实现相应的功能。该过程中所涉及的3个关键点是配置模式的选择、配置帧的格式和配置寄存器的访问。

1.1 配置模式

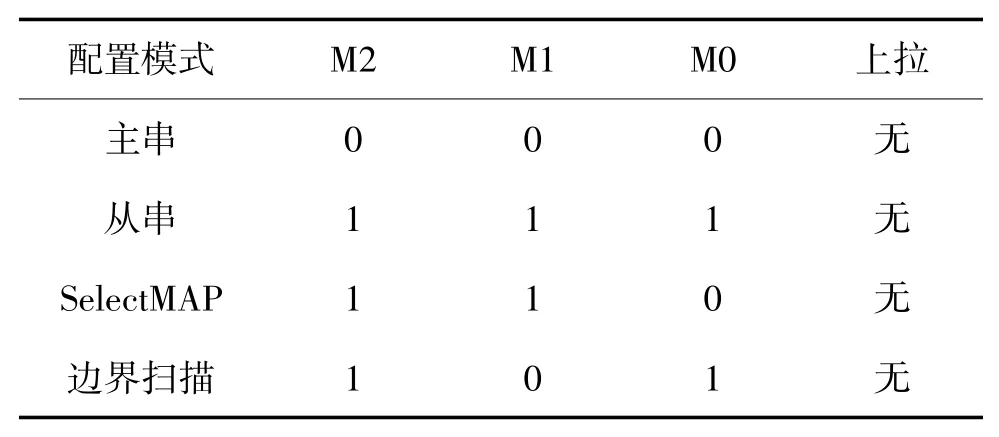

Virtex FPGA的配置模式由3个引脚控制,分别为M2、M1和M0,理论上有8种配置模式,但常见的主要有4种,如表1所示。

表1 Virtex FPGA常见的配置模式

其中,主串模式是指上电后,FPGA产生配置时序,自动地从外部存储器中加载配置位流。而从串模式则相反,FPGA处于从机模式,由CPU、DSP等提供时序,配置位流从硬盘等媒介加载到FPGA中。SelectMAP模式是一种8-bits并行模式。边界扫描(JTAG)模式是一种调试模式。作为相应的配置接口,SelectMAP接口和JTAG接口都能完成配置和回读操作,考虑到JTAG接口对资源占用较少且长期激活等特点,本试验中将通过JTAG接口进行位流的配置与回读。

1.2 配置接口

联合测试行动小组(JTAG:Joint Test Action Group)是IEEE 1149.1标准的常用名称,该协议主要由测试访问接口(TAP)和边界扫描结构两个部分组成。通过JTAG接口,测试人员可以灵活地访问器件的内部节点,对芯片内部的模块进行在线编程和调试,从而大幅度地提高测试效率。

1.2.1 TAP接口

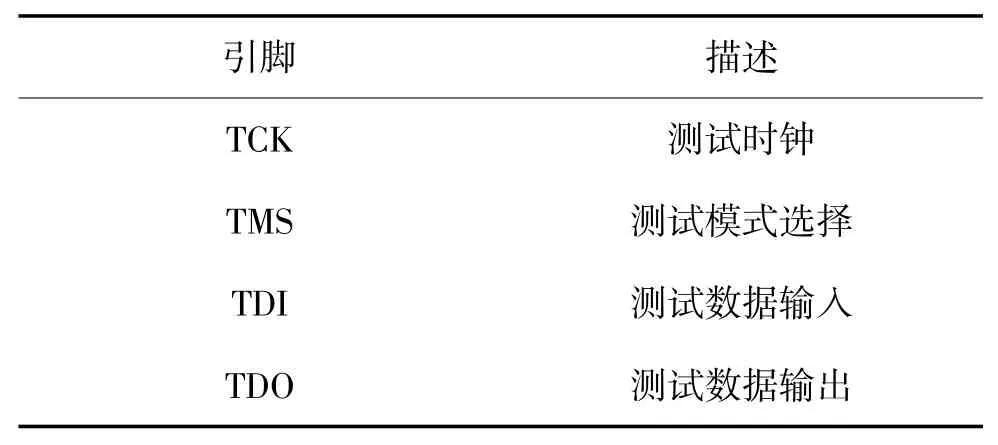

Virtex系列的FPGA全都支持JTAG接口。根据IEEE 1149.1标准的描述,TAP控制器包含了4根强制性的专用引脚,分别是TCK、TMS、TDI和TDO,其余一些引脚如复位引脚都是可选的,如表2所示。

表2 TAP接口控制引脚

其中,TCK与TMS共同作用来控制着TAP控制器的模式选择,TAP是一个16状态的有限状态机,TMS引脚是一个上拉引脚,在不驱动时呈现高电平,在时钟上升沿的触发下,TMS引脚的状态将会决定TAP的状态序列,对于TAP控制器而言,虽然有多种状态,但主要只有两种状态变化序列,即数据移入数据寄存器和命令移入命令寄存器。而对于数据寄存器和命令寄存器中的数据输入和输出,则是通过TDI和TDO引脚串行输入和输出来实现的。

1.2.2 边界扫描结构

JTAG测试得以有效实施的另一依据便是边界扫描结构,该结构的主要组成部分是一系列被串联起来的寄存器所组成的扫描链,边界扫描结构的示意图如图1所示。

图1 边界扫描结构

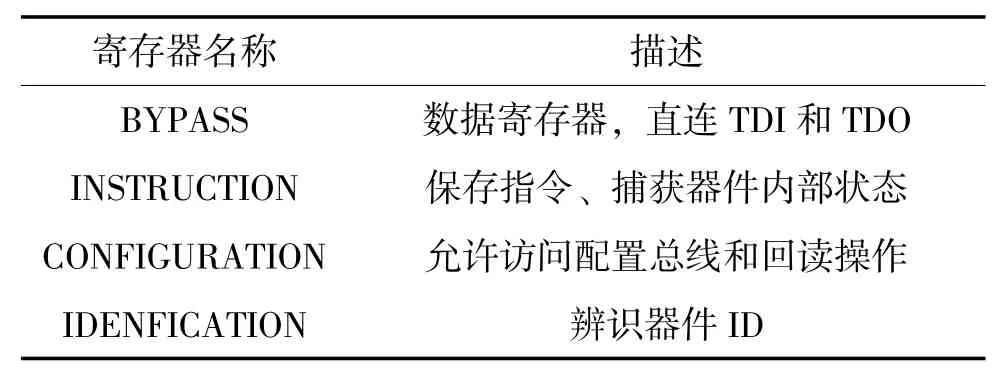

如图1所示,一系列的IOB组成了扫描链,该扫描链形成了数据的输入与输出通道。该结构中其余寄存器的作用如表3所示。

表3 边界扫描寄存器

1.3 配置帧

FPGA的资源主要有IOB、CLB和BRAM,以及互连线资源,这些资源都需要位流进行配置,而配置时,都是以帧为单位对内部存储器进行读写。帧是FPGA配置时最小的可寻址单位,如图2所示,整个配置存储器可以被分为3段,分别为BRAM0、BRAM1和CLB。

其中,每一段都是由若干帧组成,每一帧都是宽度为1 bit的自上而下的一列资源,BRAM0和BRAM1的帧所包含的资源是块存储器中的单元,而CLB中的帧列可以细分为CLB、IO和内部互联控制等元素。

如之前所说,帧是FPGA配置时最小的可寻址单位,所以在配置或回读过程中,需要对相应的地址进行解析。如图2的配置内存图中所示,分为3个帧块,每一帧块都有一个块地址,而帧块中的每一列也有相应的列地址,在寻址时通过块地址、列地址的顺序逐层定位到相应的帧。对于不同型号的器件,帧的尺寸和数目是不同的,但其寻址方式保持一致。

1.4 位流与配置寄存器

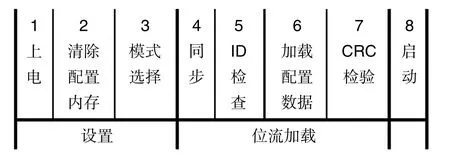

配置寄存器是指配置过程中所使用的若干寄存器,这些寄存器在配置命令的作用下完成了如图3所示的配置流程。

图3 Virtex FPGA配置流程

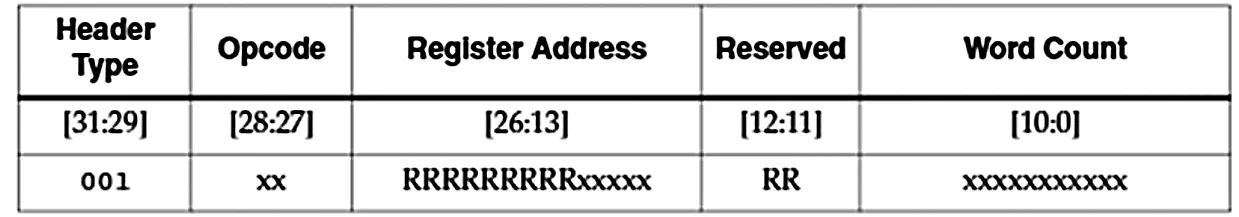

对于初始化设置阶段,主要涉及的是模式选择寄存器,在第一小节配置模式中已有描述,位流加载过程是整个配置过程中最为关键的环节,而且整个过程也是对配置寄存器进行读写的过程。首先,对于位流而言,是由两类数据包构成,如图4-5所示,给出了两类数据包的包头:第一类的包头包含了寄存器的定位等信息,可以独立地完成寄存器的读写,但相应地,其所携带的包数据较少;第二类包头不含寄存器信息,不能独立地使用,必须与第一类包头结合使用。通常在读写帧数据时,考虑到字数较多,所以先发一个不含包数据(字数为0)的第一类包头,再发一个第二类包头,随后开始帧数据的传送。

图4 第一类数据包

图5 第二类数据包

其次,位流对于寄存器的读写只能通过第一类包进行操作,第一类包所涉及的寄存器如表4所示。

表4 配置寄存器

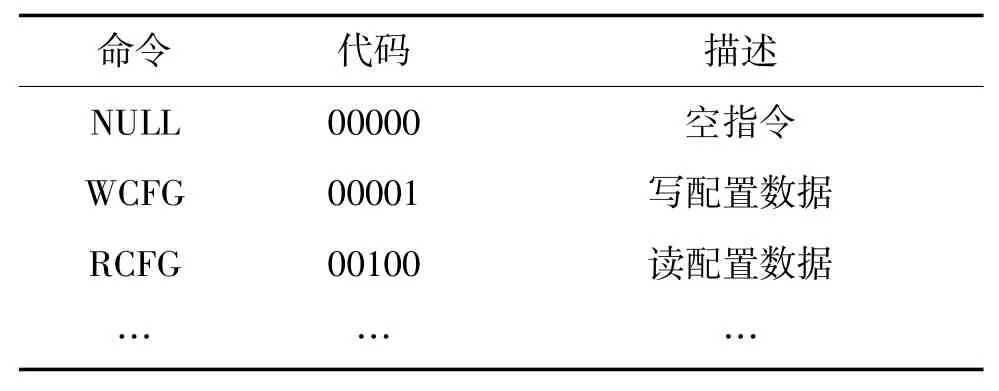

其中,CMD命令寄存器控制着配置帧数据的读写和校验等操作,其常见命令如表5所示。

表5 配置命令

总之,只有正确地使用配置模式、配置接口和配置寄存器才能够将设计载入到FPGA中,这是位流回读的基础。

2 位流回读技术的设计与实现

Xilin x 7系列FPGA允许用户通过JTAG、SelectMAP等接口将FPGA内部配置数据回读到PC端进行分析,回读一般分为两种目的,分别为验证和捕获,验证是将配置内存中的数据全部回读,其中包括了用户的设计信息和当前运行所对应的各种状态值,而回读捕获相当于验证的一个子集,它主要集中于FGPA运行的动态信息,即捕获当前时刻的各种状态。本次试验探究的是设计被篡改的情况,所以此处主要就回读验证进行介绍。

2.1 访问配置寄存器

对于标准的JTAG协议而言,提供了旁路(Bypass)和边界(Boundary)寄存器去进行数据的交互。而通过JTAG访问Xilinx 7系列配置信息时则是通过类似的CFG_IN和CFG_OUT寄存器。回读指令通过CFG_IN寄存器写入,配置内存中的数据则通过CFG_OUT寄存器读出。

回读的主要操作集中于对配置寄存器的读取,尽管并非所有的寄存器都对外开放读取权限,但只要具有读取权限的配置寄存器,通常都可以利用JTAG接口进行读取,这里简要地描述JTAG读取STAT寄存器的流程,对于其余寄存器的读取与该过程基本类似。

a)复位TAP控制器。

b)通过Shift-IR将CFG_IN中的指令移入JTAG的指令寄存器中。

c)通过Shift-DR将数据包写入命令移入CFG_IN寄存器:

1)向器件写入同步字;

2)写入数个空指令;

3)将读取STAT寄存器的包头写入器件;

4)写入两个填充字以刷新缓冲区。

d)通过Shift-IR将CFG_OUT指令移入JTAG的指令寄存器。

e)通过Shift-DR将状态寄存器中的32位数据移除。

f)重置TAP控制器。

2.2 回读数据流

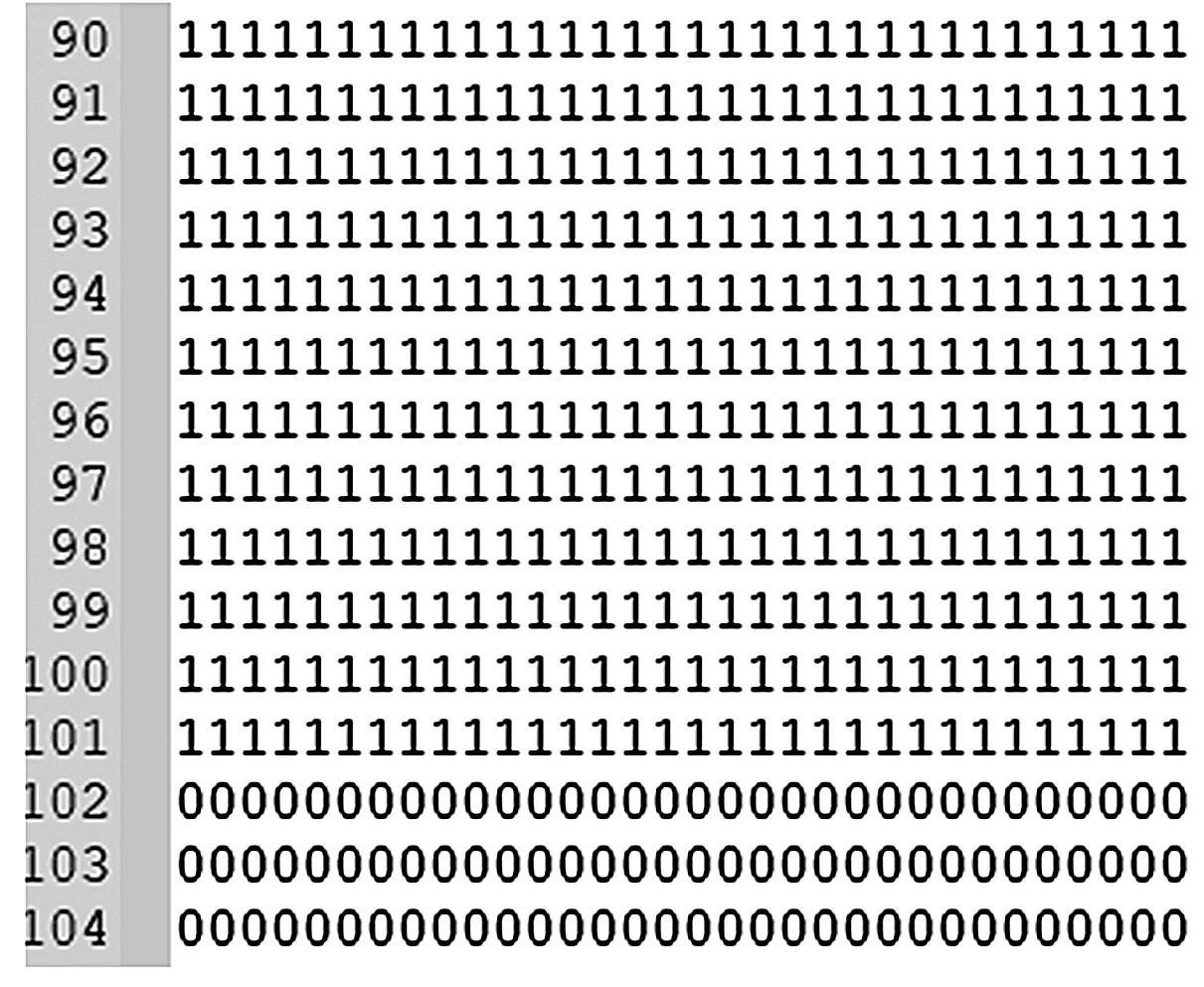

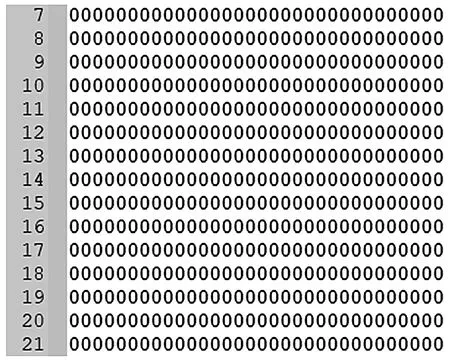

回读的数据流包含了配置帧数据,但是相比于配置的位流,该数据流中不包含配置的指令信息,也没有CRC校验信息。简言之,除了其头部的一个填充帧以外,其余的回读数据都是FPGA内部存储器的帧数据。尽管可以获得所有帧的数据,但其验证过程并不是逐位都需要参与比较,因为其中的一些比特或位置由于特殊用途而不用于比较,对此需要参考相应的MASK文件,对比MASK文件,可以从回读位流中提取出有效的数据位。对于回读验证而言,会涉及到.bit、.rbt、.rbd、.msk和.msd等文件。其中,bit/rbt文件主要存放的是设计位流;msk/msd存放的是MASK文件;rbd存放的是回读位流;而bit、msk文件是二进制文件;rbt、msd和rbd都是ASCII文件。MASK文件和回读数据流的示例如图6-7所示。

图6 MSD文件

图7 回读的RBD文件

对于同一器件而言,MASK文件中的比特数目与RBD文件中的比特数目相一致,但它们中0与1的意义截然不同,对于RBD文件中,每一比特都代表了配置帧中的某一位数据;而MASK文件则是针对回读位流而生成的一类文件,其中1代表了遮盖,即MASK中1出现的位置所对应的位流数据不参与比较,而0所对应的数据需要比较。

2.3 回读实现

对于回读过程,就硬件部分而言,与其配置时采用相同的硬件设施;而软件部分,对于Xilinx 7系列FPGA可以使用Vivado IDE软件进行相应的配置设计和回读。

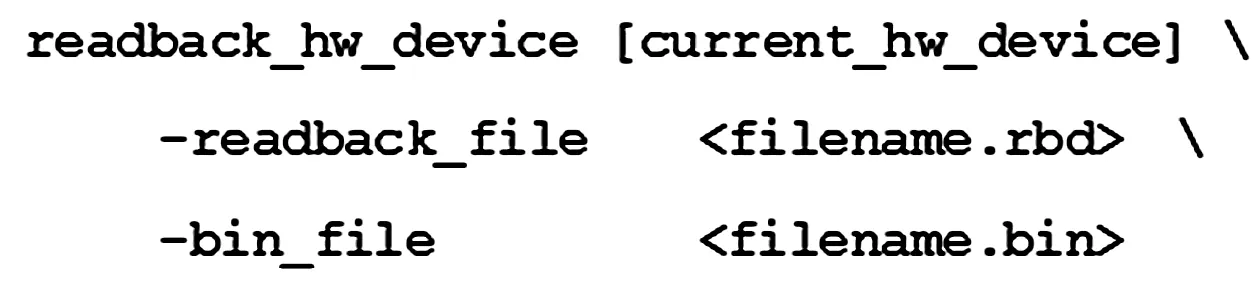

Vivado IDE提供了GUI模式和Tcl命令行模式,对于FPGA配置而言,采取其中任何一种方式都可以达到期望的目标;而对于回读操作而言,则主要是通过Tcl指令去完成。回读操作需要用到的指令,如图8所示。

图8 Tcl回读指令

图8中,-readback_file用于生成ASCII文件,-bin_file文件用于生成二进制文件,回读后的文件与配置时生成的msk或msd文件相对照即可得到配置信息。

3 系统验证

本次试验中将以Vivado IDE作为配置设计和回读操作的软件平台,以Virtex-7 FPGA VC707评估板作为硬件平台进行相应的验证工作。在试验中将使用Trust-Hub网站提供的RS232 T100硬件木马电路[10-11]作为受感染的设计。

RS232 T100硬件木马电路的触发逻辑与内部的19路信号相关,一旦触发,就将会导致接收准备信号产生stuck-at-‘0’故障,一般条件下很难触发此类木马;而且,由于该类木马面积较小,逻辑测试或者侧信道分析的效果并不理想,而在本试验中,通过位流回读的方式,可以直接筛选出那些对设计进行了恶意更改的芯片。如下是本次试验的流程:

1)RS232接口电路设计;

2)配置位流生成,同时生成相应的msd/msk即金位流(.rbd)文件;

3)通过JTAG接口配置Virtex-7 XCV7X485T FPGA;

4)将RS232 T100注入到配置中(注入木马的方式较多,这里为了验证方便,直接用RS232 T100取代原始设计将其载入FPGA中);

5)通过JTAG回读,生成回读位流文件(.rbd);

6)与金位流文件对比,得出结论。

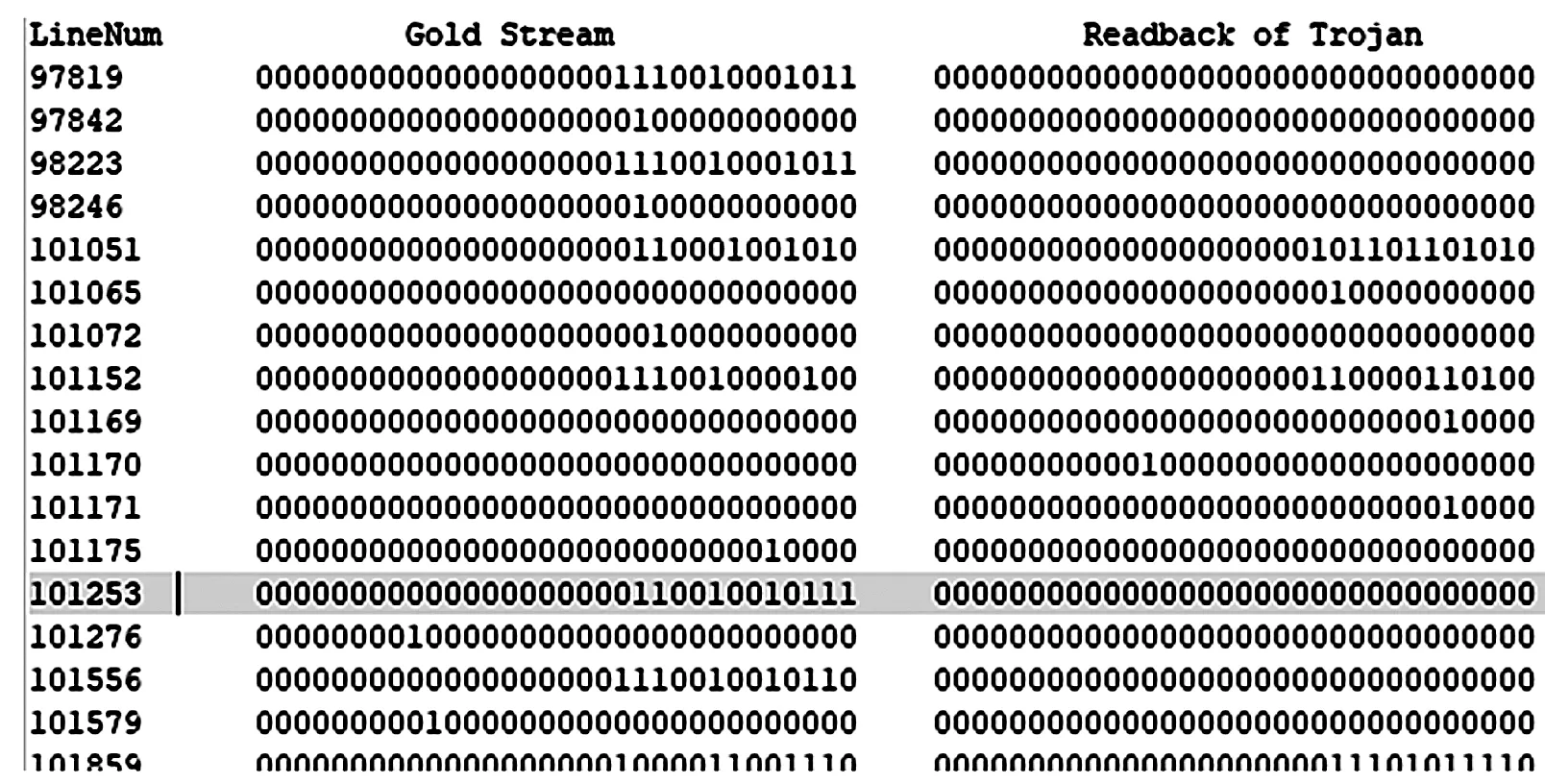

根据如上所述的流程开展试验,得到的结果如图9所示。

图9 位流对比

如图9所示,原始设计与RS232-T100的回读位流存在若干行不一致的情况,表明了原始设计与硬件木马感染电路的位流存在着明显的差异,从而证明了该方法的有效性。

4 结束语

由于FPGA开发的低成本和便捷等特性,其在航天航空等领域中应用广泛,然而,近年来有关硬件安全的问题备受关注,FPGA本身及其设计的安全性也受到了质疑。对于配置之前的设计,可以通过形式验证、门级验证等方式去检测;而对于配置后设计乃至在线运行的器件,如何保证其中功能的正确性,却鲜有讨论,尤其是随着FPGA漏洞的揭漏,该方面问题变得愈发突出。

本次设计的基于位流的木马检测系统,可以对FPGA内部配置进行回读,通过将其与原始设计相比较,可以有效地提取出受感染的部分,从而有效地防止硬件木马带来的危害。该方法的优点是相比于旁路分析等方式,其受环境和工艺影响较小;此外,该方法直接对设计的每一位进行解析,其检测率可以完全覆盖整个设计。尚不足之处是该方法执行过程中对于回读电路本身的安全性未曾考虑,以及对于加密设计,该方法需要进一步地优化。