弹载小型化软件无线电平台设计

2022-01-06马训穷管雪元薄振华

马训穷,管雪元,薄振华

(南京理工大学瞬态物理国家重点实验室,江苏南京 210094)

在外弹道测量研究中,弹载无线通信研究是新兴的且极为重要的一部分。弹载无线电系统主要用来实现弹丸与其他收发设备的实时数据传输、无线定位等功能[1-4]。在实际应用中不同测量任务、不同作战场景、不同型号弹体通常需要定制不同的通信指标与方案。传统的弹载无线电设计方法针对不同的通信系统任务,多是以分散式硬件为核心设计不同通信体制需要定制的硬件系统,这种设计方法不但功能单一、可扩展性差,而且会造成项目开发成本巨大及开发周期长[5-9]。文中运用软件无线电技术、FPGA 可重构技术和硬件电路小型化设计技术,设计了一套弹载小型化无线电硬件平台,为弹载无线数据传输提供了一种功能可扩展、硬件可升级的小型化解决方案,可以满足多种型号弹、箭的无线数据传输任务的需求。

1 硬件平台设计

1.1 硬件平台方案设计

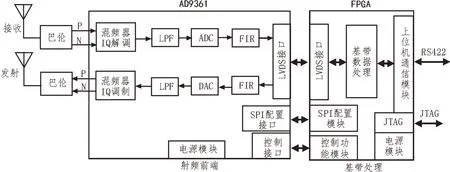

弹载小型化软件无线电平台硬件设计分为射频前端处理模块设计和基带数据处理模块设计两个部分。考虑到弹载安装尺寸小、系统功耗低、实际使用需求和电路电磁兼容等因素,硬件平台设计为一路发射、一收接收结构。硬件平台总体架构如图1 所示。射频前端AD9361与基带处理器FPGA 分别进行射频信号处理与基带信号处理。二者之间通过低压差分信号总线(LVDS)、SPI 配置接口以及控制I/O 接口进行连接。

图1 硬件平台总体架构

射频前端发射通路从LVDS 接收来自基带处理器的数字信号,然后完成数字滤波、DA 转换、模拟滤波、IQ 调制等功能后差分输出,经过巴伦输出单端调制信号到天线,将信号发射到空间中[10-12]。接收通路中,天线接收后单端输出RF 信号,经过巴伦完成单端转差分后输出至AD9361,然后进行IQ 解调、模拟滤波、AD 转换、数字滤波。所得数字信号通过LVDS送入基带处理器中。基带处理器主要完成LVDS 接口驱动、SPI 接口驱动、AD9361 工作状态逻辑控制、数字基带处理算法以及与上位机通信等功能。

射频前端AD9361 集成射频收发器构成的一路收发通道的中心频率可配置范围为70 MHz~6 GHz,信号带宽范围为200 kHz~56 MHz。射频发射端可以提供最大7 dB 发射功率,发射端外接功率放大器的设计可满足大输出功率的需求。

基带处理部分,FPGA 的主要任务是初始化配置AD9361、基带调制解调、信道编码以及RS422 接口。考虑到FPGA 内基带算法计算对于数字信号处理方面的要求不高。同时由于系统中没有高速串行接口,所以不需要高速串行收发器。此外,FPGA 外接的芯片主要包括AD9361、RS422 接口芯片等,这些芯片对FPGA 的I/O 不是特别大。实现以上功能所需的硬件资源主要是可编程逻辑块CLB 和RAM,考虑到弹载硬件系统对尺寸和功耗的要求比较高,在FPGA 厂家Xilinx 公司7 系列芯片中,Artix-7 系 列可以满足以上需求。因此,文中设计选用了Artix-7系列的FPGA。其中XC7A50T-2CPG236I 的逻辑资源和块RAM 资源丰富,同时具有10 mm×10 mm 的CPG236 封装,能够满足该设计对于小型化的需求。

1.2 硬件平台小型化设计

为了适应多种型号弹的载安装尺寸,必须进行小型化设计,提高硬件平台的可安装性能。文中主要从器件选型、布局布线、板卡安装方法3 个方面进行设计。在满足电路负载能力、电磁兼容能力、低噪声要求的前提下优化原理图设计,尽量减少器件数量且优先选用小封装器件,例如选用BGA 封装AD9361 与FPGA 芯片,选用小封装且多路输出的电源芯片,小封装的电阻、电容、电感等。

AD9361 芯片同时具有射频模拟电路与高速数字电路。从信号完整性考虑,为了使AD9361的RF部分与数字部分的快速瞬变保持隔离,设计采用10 层PCB 分层,层叠设计如图2 所示。

图2 PCB层叠设计

PCB 第1 层Top layer 与 第10 层Bottom layer 为射频模拟信号布线层和器件放置层,第2、9 层为第1、10 层的参考地层,两层均为完整铜平面,这对维持射频信号完整性至关重要。第3、8 层为电源层,第3 层分区布置AD9361 模拟1.3 V、数字接口电源为2.5 V、逻辑输出GPO 电源为3.3 V。第8 层分区布置FPGA的内部逻辑电源为1.0 V、辅助电源为1.8 V、I/O 口驱动电源为2.5 V 与3.3 V。AD9361 与FPGA 的数字线路位于内部第5 层和第6 层,包括SPI、LVDS、控制输入输出等线路,阻抗设计等长差分线为100 Ω、单端信号线为50 Ω、参考层为第4、7 层纯铜平面。

为了缩减弹载安装面积,板卡设计为两块直径为24 mm、板厚为1.3 mm 的圆形板,两块板间使用柔性连接工艺,增加连接可靠性的同时保证抗过载能力。硬件实物如图3 所示。

图3 硬件实物图

图中右侧为硬件平台,下面一块为射频板,搭载AD9361及其外围电路,上方一块为基带处理板,放置FPGA 芯片、FLASH 芯片、串口芯片等。两板堆叠安装,板间由3.5 mm 铜柱固定,最终形状为直径24 mm、高8 mm 的圆柱体,可以满足多种弹载安装需求。

2 软件设计方法

2.1 数字接口驱动设计

AD9361 与FPGA 之间的收发通道的数据传输要适应大范围的数据传输速率。硬件设计中AD9361与FPGA 数据传输通过低压差分信号线LVDS 总线连接。在1T1R 工作模式下,AD9361 的LVDS 模块可实现最大I/Q 两路共122.88 MSPS 数据传输速率,射频信号带宽为56 MHz。FPGA 通过四线主从SPI 总线读写AD9361 可编程寄存器,可以实现射频前端的初始化参数配置与工作状态机控制。接口驱动用软件编程的方法在FPGA 内实现LVD、SPI、UART 3 种接口的数据传输时序逻辑与接口通信指标控制的数字电路系统。

2.2 基带数字系统设计

基带数字系统包括发送通道与接收通道两部分。

发送部分设计包括信源编码、信道编码、数字调制等。常用的信道编码算法如LDPC 编码、TPC 编码、扩频编码,常用的调制算法为相移键控PSK、频移键控FSK 调制。调制后输入AD9361 的为12 位伪码的离散数字信号,通过LVDS 接口驱动模块将I/Q两路数字信号送入AD9361 中。

接收通道设计部分,接收数字系统通过LVDS 接口接收到的数字信号,也是12 位伪码的离散数字信号。经过同步处理、数字解调、信道译码后输出传输的信息数据,通过RS422 接口发送给上位机。

2.3 射频收发器编程设计

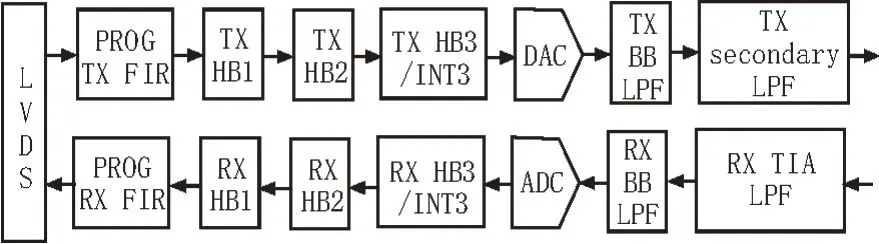

射频芯片AD9361 中收发通路信号处理架构如图4 所示。

图4 AD9361收发信号处理架构

发射通道从LVDS 获取基带I、Q 数字信号,之后经过4 级数字滤波器:PROG TX FIR、TX HB1、TX HB2、TX HB3,对数字信号进行插值,进而获取滤波增益。数字滤波器的插值倍数、滤波器阶数与位宽等参数均可通过对AD9361 的寄存器编程进行控制。滤波后送入内部DA 转换成模拟信号,经过两级模拟低通滤波器(LPF)滤除杂散干扰之后上变频成射频信号。其中模拟滤波器分为TX BB LPF、TX secondary LPF 两级,两级滤波器带宽均可配置。第一级的带宽范围较窄为625 kHz~32 MHz,通带带宽设置为信号带宽的1.6 倍;第二级的带宽范围为2.7~100 MHz,通带带宽设置为信号带宽的5 倍[13-14]。

接收通道中射频信号经过下变频后的信号路径由两个可编程模拟低通滤波器、一个12 位ADC 和四级可编程数字抽取滤波器组成。模拟低通滤波器用于去除下变频产生的高频干扰。数字抽取滤波器可以提供带宽限制和带外噪声,并在数字化后降低杂散信号,也可用来匹配正确的数据速率送入LVDS 基带数据收发接口[15-17]。

2.4 软件实现方法

在硬件平台上进行软件设计以实现任务需要,无线电系统按照如下方法进行设计:

1)明确通信任务与技术指标;

2)设计无线电系统软件框架;

3)平台接口驱动设计;

4)射频端参数配置设计;

5)基带处理算法设计;

6)在开发平台Vivado 上实现3)、4)的RTL 级编程,并对软件功能、时序、布局布线进行仿真;

7)将软件搭建的数字系统执行成bit 文件,烧写入FPGA 芯片并调试平台功能。

3 实验验证

按照2.3 节的软件实现方法,并以射频信号中心频点为2.25 GHz、信息码速率为1 Mbps、传输码型为RNRZ_L、调制为BPSK 数字调制发射机为例进行实验。

3.1 无线电系统软件框架设计

软件系统设计主要分为两部分:基带系统软件设计与射频前端配置软件设计,软件系统设计框架如图5 所示。基带系统软件设计主要实现基带数字信号处理功能,设计包括信源数据输入接口、数据包缓冲、PCM 编码、BPSK 调制以及LVDS 驱动等软件设计。射频前端配置软件设计分为配置参数设计与配置参数写入两部分。其中配置参数设计部分是根据任务指标对AD9361 芯片进行射频收发接口、数字时钟与滤波器、数字接口、内部状态机工作模式、接受增益控制与发送功率衰减控制等六大部分进行设计。配置参数写入部分主要是在Vivado 平台用硬件描述语言Verilog HDL 设计中实现文件写入ROM 逻辑、参数写入逻辑、AD9361 状态监控逻辑与SPI 接口驱动逻辑等。

图5 软件系统设计框图

3.2 软件设计实现与仿真

基带软件设计中信源从上位机输入FPGA 中,缓冲模块拆解包后进行PCM 信源编码,码型设计为RNRZ_L,同时PCM 模块将突发性数据包缓冲为连续的码元速率为1 Mbps 的信号流PCM_out。BPSK调制部分使用DDS 直接数字频率合成器生成1 MHz的正弦波,将一个周期分成16 个相位,通过读ROM方式输出16 个幅值。将PCM_out 码元与载波相乘得到数字调制输出信号BPSK_out。功能仿真结果如图6 所示。BPSK_out 为12 位伪码型数字信号,LVDS驱动模块将已调信号发送给射频前端。

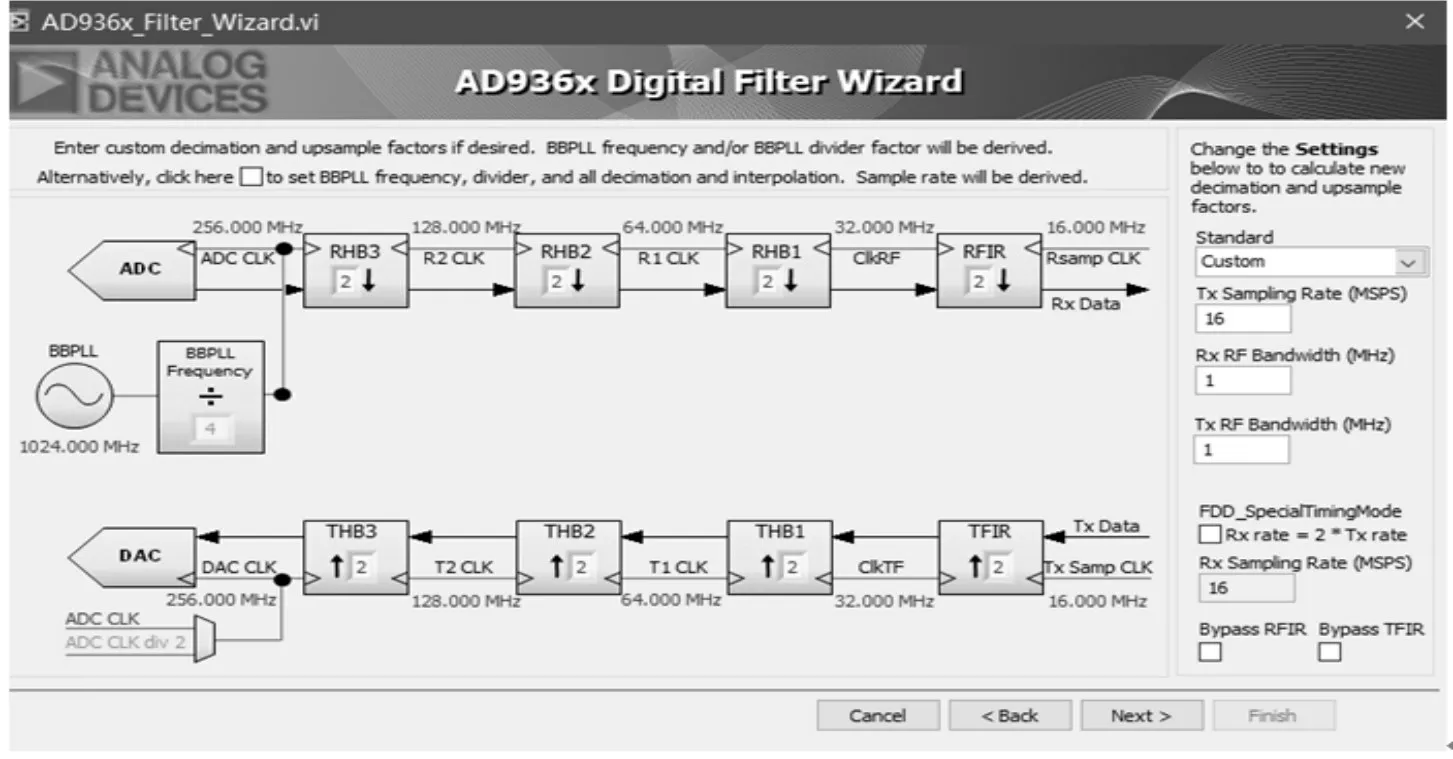

图6 BPSK调制系统仿真

射频前端软件的配置参数是根据3.1 节中阐述的六部分参数进行设计的。图7 为使用AD936X Evaluation Solftware 工具软件进行软件射频前端数字滤波器参数设计的配置页,参数设计完成后可从工具软件中导出配置文件。在这个页面主要进行射频前端AD9361 芯片内部的数字滤波器设计,前面阐述的系统任务码速率为1 Mbps,在BPSK 调制端使用一个正弦周期、16 个相位幅值的方式生成正弦波调制原始码元,通过LVDS 接口输入AD9361 的数字信号符号速率为16 Msps,发射通道符号速率设计为16 Msps,发射与接收通道的射频带宽设置为1 MHz即可。发射端4 个内插数字滤波器的内插因子均设置为2,在DAC 数字输入端,数字信号的符号速率达到256 Msps。

图7 数字滤波器参数配置

将生成的参数文件编辑成可写入ROM 的.coe 文件,在Vivado 平台的工程项目软件中创建配置AD9361 的ROM,之后编写参数配置逻辑与状态检测逻辑,程序仿真如图8 所示。其中dataout_ROM_0为配置文件ROM 输出,高10 位0x3df 为写入寄存器地址,低8 位0x01 为写入的配置参数。SPI_CLK 为SPI 总线读写时钟,SPI_ENB 为总线使能信号,SPI_DI 为写入AD96361 寄存器信号,SPI_DO 为读取AD9361 寄存器信号,当前为写入模式。

图8 AD9361配置仿真

3.3 硬件平台实验与结果

软件系统设计、编程与仿真结束后,进行实验验证。实验利用PC 端串口助手通过RS422 串口向硬件平台每1 ms 发送相同的一帧30 字节的数据包,硬件平台使用直流电源5 V 供电,射频输出端外接一个锥形天线。接收端使用实验室现有的地面接收站,接收解调出数据帧并保存为数据文件,并使用示波器频谱仪通道连接频谱探头测量空间中的射频信号频谱。实验场景如图9 所示,可见软件无线电平台加锥形天线的工作电流为860 mA,信号发射频谱如图中频谱仪所示,单边带宽为500 kHz,接收功率为-65 dBm。在地面接收站中选择接收信号中心频率为2.25 GHz、调制方式为BPSK、码型为RNRZ_L、码速率为1 Mbps,帧头0xEB90 指标对齐后,接收机成功解调并保存接收到的数据。

图9 实验场景

实验完成后,在PC 端将硬件平台发送数据帧data1 与地面站保存的数据帧data2 的帧头对齐后,循环求差校验data2 文件的全部数据帧,验证系统数据传输工作是否正常,结果如图10 所示。可以看出接收机保存数据与平台发送数据求差结果全为0,按任务需求在硬件平台进行软件重构的BPSK 发射机系统设计成功。

图10 data1与data2求差对比图

4 结论

文中设计的弹载小型化软件无线电平台,成功地将软件无线电技术应用到炮弹的弹载数据链传输研究中,拓展了弹载无线电设备通信任务的兼容性与便捷性。该平台具有良好的功能可扩展、硬件可升级及适应多种型号弹搭载的优点,经过工程实践证明,使用该方法设计的硬件平台可以有效节约不同弹载无线电任务的研发成本并缩短开发周期。