基于NRS1800 的SRIO 互连技术的研究与设计

2022-01-04王浩宇李雨航李龙杰张皓林

王浩宇, 李雨航, 李龙杰, 张皓林

(中国兵器装备集团自动化研究所有限公司, 四川绵阳 621000)

0 引言

国内SRIO 技术的发展时间较晚, 并且应用范围有限, 近几年随着信息化建设和宽带无线通信等应用的快速发展,SRIO 技术在国内逐步得到应用。 国内各大相关单位在SRIO 应用方面较为急迫,但是由于起步时间晚,SRIO 设计技术方面的积累较少, 主要表现在高速SerDes、无阻塞交换结构、SRIO 协议处理、以及整个SRIO交换系统集成等方面。 并且由于SRIO 技术在协议硬件实现、高速数据无阻塞交换、动态事件管理等技术的实现复杂性,使得SRIO 交换部件自主研发门槛较高,国内关于SRIO 的研究大部分是基于国外进口SRIO 交换芯片的应用研究。 如中兴和华为等。 目前,国外只有IDT 一家公司提供SRIO 交换芯片,其主打产品是CPS1848。 但随着中美贸易战的深入,作为高端电子行业的代表之一,目前与IDT 的合作已经出现技术支持、采购等方面的困难。 国内天津市滨海新区信息技术创新中心已经于2018 年开发成功了国内首款具有自主知识产权的NRS1800 SRIO Gen2 交换芯片,可用于替换CPS1848。

1 SRIO 互连系统总体设计方案

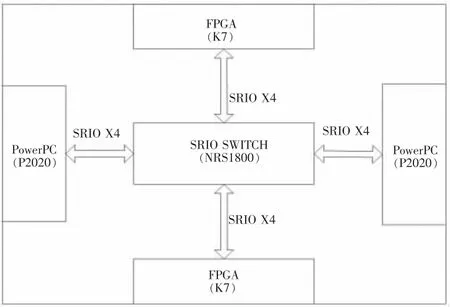

本设计的SRIO 互连系统以国产SRIO 交换芯片NRS1800为核心,搭载两片PowerPC 及两片FPGA。其中,PowerPC 处理器采用的是FREESCALE 公司的P2020NXE2KFC,P2020 拥有4 路SerDes 通信链路可配置成SRIO 通信模式, 本设计中将P2020 的SerDes 接口配置成1 路4X SRIO 端口,参考时钟采用125MHz,速率配置为3.125Gbaud。FPGA 采用的是XLINX 公司的K7, 设计中将K7 的CTX模块配置为一路4X SRIO 接口,并由K7 的SRIO IP 核来控制CTX 模块完成SRIO 接口的收发[3]。 其端口频率配置为6.25Gbit/s。 SRIO 交换芯片采用的是国产SRIO 交换芯片NRS1800,满足SRIO2.1 规范,支持48 路通道和最多18 个端口。 本设计中将NRS1800 配置成12 路4X SRIO 接口,4路4X SRIO 接口,实现了FPGA 和PowerPC 之间以及PowerPC 之间的相互通信[4]。 其SRIO 互连总体关系见图1。

图1 SRIO 互连总体关系图

2 硬件电路设计

2.1 NRS1800 芯片简介

NRS1800 是一款我国自主研发的SRIO 交换芯片,含有18 个端口和48 个通道, 具有低延时, 高可靠性等优点。 同时,NRS1800 支持高达240Gbps 的吞吐量。 也可以与带有SRIO Gen1 与Gen2 的端点设备对接,比如微处理器、DSP、FPGA、ASIC 和桥片等。 NRS1800 端口支持1x、2x、4x 的端口宽度, 每条lane 速率支持1.25、2.5、3.125、5和6.25Gbaud。

2.2 NRS1800 与CPS1848 区别

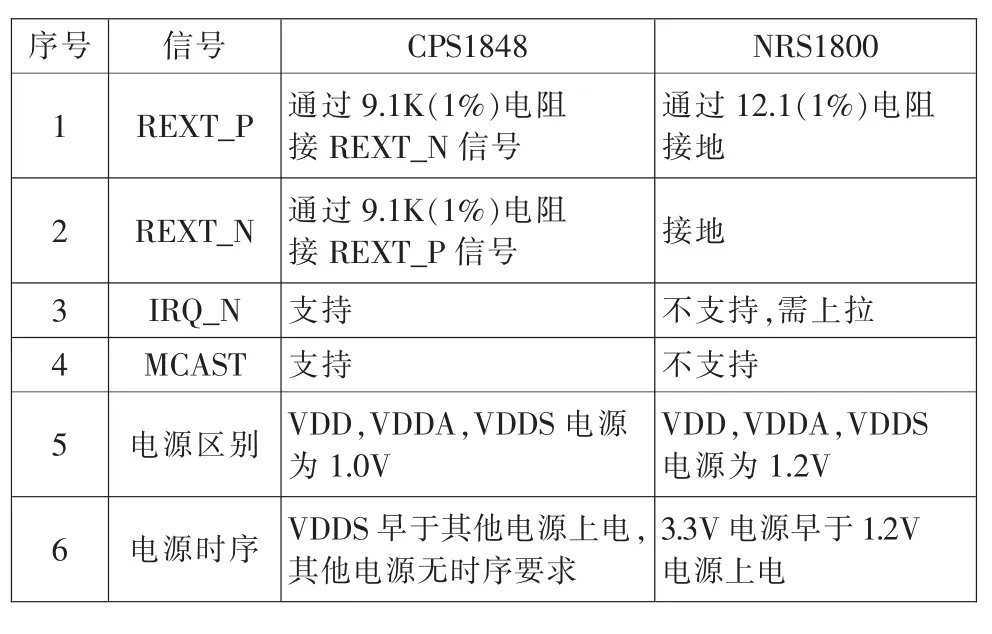

NRS1800 与CPS1848 管脚兼容,但在设计时部分管脚处理任然存在差异,如电源时序REXT_P 及REXT_N 等信号。 具体差异如表1 所示。

表1 NRS1800 与CPS1848 管脚差异

2.3 基于NRS1800 的外围电路设计

2.3.1 供电设计

NRS1800 有6 个电源域电压,分别为数字电源VDD=1.2V,模拟电源(PLL)VDDA=1.2V,Serdes 电源(不包含发送侧)VDDS=1.2V,Serdes 发送侧电源VDDT=1.2V,模拟高压电源VDD3=3.3V,数字IO 电源VDD3A=3.3V。NRS1800上电顺序为3.3V 先上电,1.2V 后上电,间隔10ms。

本设计中采用一片LTM4633 和LTM4620 进行NRS1800 的电源供电。 其中,LTM4633 的两路输出用于P2020 和其他芯片供电,一路用于NRS1800 的3.3V 电源供电, 并用磁珠将VDD3 和VDD3A 的电源输出隔开,LTM4633 的3.3V 输出控制引脚RUN 和电源供电由ATX电源上的12V 电源输入控制, 即ATX 电源启动时,LTM4633 的3.3V 输出到NRS1800 进行供电。 采用LTM4620 的两路输出对NRS1800 的1.2V 电源输入进行供电,LTM4620 的电源供电由ATX 电源上的12V 电源输入控制,NRS1800 稳定运行需要3.3V 和1.2V 上电间隔10ms, 本设计中通过LTM4633 的PG 信号输入到LTM4620 的1.2V 控制引脚RUN 中来控制NRS1800 的上电时序,并在LTM4620 的RUN 输入端设计RC 电路来调整上电间隔时间[5]。

通过上述设计,保证了在系统加电启动后,NRS1800的3.3V 先上电,1.2V 后上电,上电间隔为10ms。

2.3.2 端口配置设计

NRS1800 的时钟输入为一个156.25MHz 的差分时钟,并通过该时钟为芯片的PLL 提供参考时钟。本设计采用一片晶体振荡器产生156.25MHz 的LVDS 时钟信号为NRS1800 提供参考时钟。

NRS1800 有四个象限,每个象限拥有三个SRIO 端口,通过象限配置引脚QCFG[7:0]来对每个象限端口的宽度进行配置, 复位后也可以通过软件来重新分配端口的宽度。 本设计中,通过引脚QCFG[7:0]将各个象限的SRIO端口配置成4X 模式。 通过将速度配置引脚SPD [2:0]配置成111, 使SRIO 端口的每条lane 的数据传输速率为6.25Gbaud/s。

3 软件配置

NRS1800 的配置方式非常灵活,支持5 种寄存器配置方式,可通过外接JTAG 调试适配器,外接I2C 调试适配器,外部EEPROM 配置,CPU 通过I2C 接口配置以及CPU 通过SRIO 维护包配置。外接JTAG 和外接I2C 用于调试时使用,且外接JTAG 调试功能在x86 上位机配套了可视化调试软件。 通过外部EEPROM 配置则是设备在上电复位完成后从外部EEPROM 中加载配置到寄存器,完成交换芯片的初始化工作。本设计选用的是CPU 通过I2C 接口结合SRIO 维护包共同维护NRS1800 的配置。 I2C 接口完成交换芯片初始化工作以及交换芯片工作状态未知时调试交换芯片,增强系统可靠性以及可维护性。SRIO 维护包用于完成交换芯片工作过程中对交换芯片以及其他SRIO 网络上节点状态的查看以及配置修改, 提高运行过程中配置修改与查看效率。

3.1 I2C 配置

NRS1800 芯片可以作为从设备和临时主设备。 当工作在临时主模式下, 仅支持7bit 的从设备地址的外部通信,并且需将交换芯片的配置按照规定格式固化到EEPROM 中,交换芯片在上电复位完成后从外部EEPROM 读取配置,读取数据中包括一个CRC 值,NRS1800 用该CRC值与自身产生的CRC 值作对比,来决定寄存器加载的合法性,CRC 成功后完成寄存器初始化。当芯片工作在从模式时,设备支持7/10bit 的从地址访问,但该NRS1800 I2C 接口7bit 寻址方式不支持多个NRS1800 同时连接到I2C 总线,因此,为增强I2C 总线的节点可扩展性,统一使用10bit寻址方式。 本设计中, 底板中P2020 作为CPU 通过I2C总线访问NRS1800 交换芯片寄存器,实现对交换芯片的配置和状态查询。

3.2 SRIO 维护包配置

维护操作属于SRIO 协议中第八类I/O 逻辑操作,接入系统的主机可通过不同事务类型的SRIO 维护操作,结合各个端点设备的设备ID 以及跳数字段,可精确的访问网络中端点以及交换器件完成对SRIO 能力寄存器、状态寄存器(CAR 和CSR)以及数据结构的访问与控制,从而完成对SRIO 交换系统中所有节点(包括SRIO 端点和交换器件)的访问与控制,具有非常高的灵活性。 本设计中将P2020 中SRIO 节点的窗口1 配置为维护通道,实现对整个交换网络的管理。

4 功能以及性能验证

根据SRIO 协议以及本设计硬件架构, 测试了PowerPC 与Power PC,Power PC 与FPGA 之间的NREAD、NWRITE、SWRITE、维护操作、维护操作等I/O 操作功能以及DOORELL、MESSAGE 等消息操作功能,均能够正确并长时间稳定工作。

笔者编写了Power PC 与FPGA 之间的测试例程,采用NREAD、NWRITE 的方式进行性能测试。使用SysClkRateSet函数将Power PC 的系统时钟频率设置为1000 (即每秒1000 个tick),fpga 初始化后, 映射一块起始地址0x120000,大小0x1000(4kB)的内存空间到SRIO 总线空间,Power-PC 将该总线空间映射到本地起始地址为0xc2000000 的内存空间。将Power PC 起始地址为0xc2000000,大小4kB的内存数据发送65536 次,共256MB 到FPGA,测试总共发送时间并计算发送速率,接收速率测试同理,测试结果见表2。

表2 SRIO 速率测试结果

据SRIO 协议分析,SRIO 数据包载荷最大为256 字节,此时有效传输率为72%,考虑程序运行过程本身具有CPU 开销且PowerPC 本身SRIO 总线仅支持32bit 的访问,因此该速率认为距离理论值有一定差异。

5 结束语

在现代信号处理系统中,SRIO 作为一种基于包交换的互连技术,因其传输速度快,可靠性强、灵活度高的优点,被广泛应用在系统的多个模块互连中。本文设计以我国自主研发的SRIO 交换芯片NRS1800 为核心, 设计了有一种SRIO 互连系统,实现了在FPGA 和PowerPC 之间以及PowerPC 之间的高速通信, 并对系统中各个模块的数据传输进行了测试, 为国产化的高速信号处理平台的设计提供了参考。