基于IEEE1588协议的高精度时钟同步系统设计与实现

2021-12-30崔永俊韩一德

崔永俊,韩一德,郭 峰

(中北大学仪器与电子学院,仪器科学与动态测试教育部重点实验室,电子测试技术国防科技重点实验室,山西太原 030051)

0 引言

时钟同步系统目前广泛应用在分布式数据采集、测试测量、数字变电站及工业控制应用等领域。多个设备间为了实现实时采集、测试及控制,要求各设备中的时钟保持较高的同步精度。目前时钟同步方案主要包括IRIG-B码时钟同步、GNSS时间服务器同步、NTP网络时间协议同步、SNTP简单网络时间协议同步和PTP精确时间协议同步。其中GNSS时间服务器同步是将GPS/BD卫星时间作为统一标准传输到各设备节点,可同步多台设备且授时精度较高。NTP及SNTP协议以时钟源网站为时钟标准,多应用于μs级的PC标准时间等互联网时钟同步应用。PTP精确时间协议同步即IEEE1588协议,通过采用GPS/BD卫星时钟信号及网络时钟为时钟源,在NTP协议基础上实现标记硬件时间戳提高授时同步精度,适用于工业测量控制等应用[1]。本文对PTP协议进行移植,采用硬件STM32F407、DP83640物理层芯片和软件PTPd2(IEEE1588协议源码)实现了硬件时间戳的标记,减少了由于软件协议栈处理冲突等因素引入的延迟干扰,进一步提高了同步精度[2]。

1 IEEE1588时间同步原理

IEEE1588是高精度时钟同步协议,在时钟同步过程中。主时钟与各从时钟之间互相交换包含时间戳信息的报文,各从时钟通过报文中的时间戳信息计算与主时钟间的链路延迟与时间偏差,进而调整本地时钟与主时钟实现同步。主从时钟同步原理如图1所示。

同步报文分为4钟报文:Sync同步报文,由主时钟端发送到从时钟端,携带从时钟端打的t1时间戳;Follow_up跟随报文,跟随主时钟发出的Sync同步报文发出,携带主时钟端打的t1时间戳;Delay_req延时请求报文,从时钟端发送到主时钟端,携带从时钟端打的t3时间戳;Delay_resp延时请求响应报文,主时钟端发送到从时钟端,携带主时钟端打的t4时间戳和请求的端口ID。

一次时钟同步过程分为4步:

(1)主时钟在t1时刻向从时钟发送Sync同步报文,随后t1时间存放在Follow_up跟随报文中发送给从时钟。

(2)从时钟在t2时刻接收Sync同步报文,并从Follow_up跟随报文中获取t1时间戳。

(3)从时钟在t3时刻发送Delay_req延时请求报文给主时钟。

(4)主时钟在t4时刻接收到Delay_req延时请求报文,并发送包含t4时间戳的Delay_resp延时请求响应报文给从时钟。

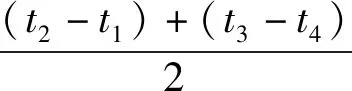

在一次时钟同步完成后,从时钟获取到t1、t2、t3、t44个时间戳,利用这4个时间戳首先计算主从时钟间的平均路径延迟Delay:

(1)

由时钟偏差Offset与平均路径延迟Delay关系:

Offset=t2-t1-Dealy

(2)

继而计算出主从时钟间的时钟偏差Offset:

(3)

2 IEEE1588时钟同步系统设计

同步系统结构图如图2所示。IEEE1588时间同步系统中通过GPS/BD卫星输出1PPS信号给主时钟提供同步信号,主时钟与从时钟均采用STM32F407和物理层芯片DP83640构成,二者采用RMII接口连接,50 MHz有源晶振提供参考时钟,参考时钟主要用于同步报文的接收发送及PTP时钟的速率调节。从时钟数量依据实际测试需求调整,主时钟在一个时钟同步系统中时钟精度最高且只有一个。

进行时钟同步时,主从时钟通过周期性的交换包含硬件时间戳的同步报文,计算主从时钟之间的时钟偏差值,在本地参考时钟的作用下对时钟速率进行调节,增添或减少偏差值实现从时钟的稳定。

2.1 系统硬件设计

系统硬件主要包括STM32F407主控模块和物理层芯片DP83640。硬件平台如图3所示。

STM32F407处理器支持IEEE1588协议,自身同样具有在MAC层的MII/RMII接口处标记时间戳功能,同时可对本地PTP时钟频率进行粗调和细调校正。在需要实现包含多个从时钟设备进行时钟同步时,STM32F407系列CPU芯片价格低廉,相对FPGA与其他ARM处理器芯片具有更高的性价比[3]。但仅采用STM32F407实现的IEEE1588协议是标记时间戳在MAC数据链路层,相比于物理层时间戳精度较低。

物理层芯片DP83640为集成了IEEE1588精密时钟协议硬件支持功能的以太网芯片。DP83640应用框图如图4所示,DP83640主要包括以太网物理层接口、IEEE1588时钟、IEEE1588控制和IEEE1588包检测处理程序。

DP83640可以实现在物理层最靠近网线的地方对数据包标记时间戳,并将时间戳存储在芯片内的时间戳寄存器中,同时DP83640具有自动标记时间戳功能,使能相应功能后,DP83640会自动识别PTP报文并将时间戳标记在发送与接收的报文中。DP83640提供12个GPIO口,使能相应管脚功能后,可对外部中断事件例如上升沿、下降沿标记时间戳,也可以通过相应GPIO口输出定时脉冲提供给自身或其他设备使用[4]。

2.2 系统软件设计

系统软件架构如图5所示,主要包括物理层DP83640、MAC层STM32F407、传输层Lwip协议栈和应用层IEEE1588协议。

时钟设备处于主时钟状态时,PTP报文由主时钟应用层产生,采用UDP报文通信,PTP报文采用Lwip协议栈的UDP_API接口传递给MAC层,MAC层接口采用RMII接口与物理层连接并传递UDP报文,物理层DP83640中的时间戳模块记录并插入包含当前报文到达时间的时间戳在PTP报文中,通过RJ45接口发送给从时钟。

时钟设备处于从时钟状态时,接收到IP报文的DP83640记录包含在PTP报文中的时间戳信息,同时发送含有当前时间戳的UDP报文给MAC层,IP报文经过MAC层和传输层的报文解封,剥离出PTP报文数据发送给IEEE1588协议实现对时间戳信息的提取,之后运行最佳主时钟算法和时钟同步算法,调节本地时钟完成主从时钟同步[5-6]。

2.2.1 IEEE1588协议处理流程

STM32F407完成各协议的初始化后,IEEE1588协议进入PTP_Initializing状态,系统运行最佳主时钟算法判别当前时钟状态。IEEE1588协议处理流程如图6所示。

若当前时钟处于主时钟状态,主时钟向从时钟依次发送Sync同步报文和Follow_up跟随报文,等待接收报文,记录报文到达时间并解包。主时钟判别当前报文是否为从时钟发送的Delay_req延时请求报文,若是,则向从时钟发送Delay_resp延时请求响应报文并继续发送Sync同步报文和Follow_up跟随报文,若否,继续等待接收报文。

若当前时钟处于从时钟状态,从时钟等待接收从主时钟发送的报文,若为Sync同步报文,继续等待接收报文,当接收到Follow_up跟随报文,记录Follow_up跟随报文包含的时间戳t1,并向主时钟发送Delay_req延时请求报文,之后当接收到主时钟发送来的Delay_resp延时请求报文,记录其包含的时间戳t4,根据记录的4个时间戳计算时钟偏差并修正本地时钟。

2.2.2 Lwip协议栈

Lwip是轻型(Light Weight)IP开源协议栈,保持TCP/IP协议主要功能的同时对RAM等资源占用量少,适合在STM32F407处理器中使用,有无操作系统均可运行。

Lwip协议栈主要实现与MAC层的通信接口及上层应用层的通信接口建立。与MAC层通信时,Lwip协议栈调用low_level_output()函数将封装好的IP报文复制到DMATxDescToSet描述符指向的缓存,etharp_output函数将IP报文封装为以太网帧后,调用linkoutput函数将数据包经由MAC层发出。接收到报文时,low_level_input()函数对DMA描述符轮询检查,当DMA描述符缓存中存有报文时,将报文复制到pbuf结构体中,由Lwip协议栈对报文进行处理[6-7]。

与应用层通信时,Lwip采用Nerconn API标准接口,报文封装在netbuf中,调用netconn_bind()函数将本地IP地址addr与UDP端口号319、320绑定,建立网络连接。后调用netconn_recv()接收函数和netconn_send()发送函数实现报文的发送与接收,接收到的报文由IEEE1588协议进行处理[8-9]。

2.2.3 本地时钟调节

DP83640对本地时钟调节有相位调整和频率调整[10]。相位调整采用单步调整,当本地时钟比主时钟运行慢时,调整值为正值,由于DP83640内部会对单步调整值进行16 ns的补偿,因此调整寄存器中的值应为调整值的基础上增加16 ns。当本地时钟比主时钟运行快时,调整值为负值。

频率调整采用固定速率调整和临时速率调整相结合的方式纠正本地时钟和主时钟之间的频率偏差。固定速率调整量为固定的2-32ns。临时速率调整为短时间的速率调整,将临时速率值及持续时间写入临时速率控制寄存器PTP_TEDH和PTP_TEDL,持续时间结束后返回固定速率调整。

3 时钟同步测试

本文采用卫星时钟作为授时源,分别采用主从时钟直连和主从时钟通过交换机相连的方式对主从时钟同步精度进行测试及结果分析。

3.1 主从时钟直连同步测试

主从时钟直连同步测试为主从时钟通过板上的RJ45接口用网线连接,设置同步时间间隔为1 s,每秒主时钟发送1次Sync同步报文,主从时钟的时间偏差通过串口输出,时间偏差值的统计分析结果如图7所示。

进行250次同步后,主从时钟最大时钟偏差为121 ns,时钟偏差基本分布在±100 ns之间,精度优于±150 ns。

3.2 主从时钟交换机相连同步测试

如图1所示,主从时钟之间通过100 MHz交换机连接,设置同步时间间隔为1 s,结果如图8所示。

进行250次同步后,主从时钟最大时钟偏差为-196 ns,时钟偏差基本分布在150 ns之间,精度优于±200 ns。相比于主从时钟直连方式,采用交换机相连由于存在往返时延不对称形成非对称链路,增大了时钟偏差计算误差,造成同步精度下降。考虑若采用支持IEEE1588交换机,降低时延不对称性,可提高一定的同步精度。

4 结束语

本文基于IEEE1588协议,设计了软件与硬件结合的高精度时间同步系统,并在硬件平台测试中实现了主从两个时钟设备的同步,并达到了一定的同步精度。且随着时钟设备的增加,网络负载也会增大,需要进一步对系统拓补结构进行优化,增加一定的网络元件,如透明千兆交换机等,从而提供具有更高同步精度的时钟同步系统。