高精度低时延浮点双曲函数运算单元的VLSI实现

2021-12-17刘明傅文佳

刘明 傅文佳

摘要:高精度浮点超越函数在科学计算等应用中需求越来越大,双曲函数是超越函数中的一个重要组成部分。早期双曲函数的计算借助软件实现,近年来由于硬件实现超越函数的性能优于软件,硬件实现逐渐获得重视。计算高精度的超越函数时,虽然位宽的增加会带来资源消耗的急剧增加,但数字电路集成规模的扩大为全硬件化高精度浮点运算单元提供设计基础。CORDIC算法作为逐位迭代法中的经典算法,仅需要加法和移位操作即可完成函数计算。因此,本文基于CORDIC四步并行迭代算法,完成128位浮点双曲函数运算单元的硬件建模。

关键词:双曲函数 超越函数 CORDIC算法

一、引言

近五年来,中国的集成电路(Integrated Circuit,IC)业在国家政策的有力支持和市场需求的快速提振下取得了快速发展,其整体技术水平和市场规模在不断地增长。随着人工智能、5G、智慧城市等概念的提出和蓬勃发展,IC业逐步成为国内信息技术产业的重要支撑和安全核心。然而,作为全世界IC产业消费占比约1/3的市场国,中国本国的IC产值全球占比不足7.5%。细分至芯片设计产业,我国的通信芯片、LED芯片等虽已有一定的市场规模,但高端芯片市场迫切需要打破瓶颈。

在能源勘测、游戏渲染、气象学和海洋学、金融保险、计算机辅助设计等领域中,需要大量三角函数、指数函数、对数函数、双曲函数等超越函数的计算。在科学计算中,双曲函数在信号处理、电力传输、航空航天、统计学等工程领域,有着广泛的应用。对于实时处理要求高的领域,比如通信、测绘等,高速度、高精度的双曲函数具有重要作用。早期的计算大多借助于软件来实现,往往需要频繁调用浮点运算子程序库,这样显然降低了运算的速度,在进行高精度运算时速度甚至更低。直到近十年,由于硬件实现函数的计算性能优于软件,硬件实现才获得重视。

二、双曲函数硬件实现算法研究

通常,双曲函数的运算只由软件实现,直到最近的十几年,随着生产工艺的升级迭代,使用硬件实现浮点双曲函数计算的性能逐渐优于使用软件的实现方式。诸多文献都提出了双曲函数的硬件实现,其中典型的方法包括查表法、多项式逼近法和CORDIC算法。近年来,随机计算法也引起了广泛的关注。以上的方法都有其优缺点,使用时性能侧重点也不一致。

通过对超越函数计算方法的分析和比较可知,若采用查表法,则需要至少一个2n× n位的ROM表,随着n的增大,硬件资源的消耗剧增。多项式逼近法和基于查找表的多项式逼近法适用于小范围小输入数值的计算,当输入接近某些值时,双曲函数的计算误差将会变大;此外,由于多项式逼近法中有大量的乘法操作,用该方法计算双曲函数时将难以达到高精度的要求。而随机计算法在计算精度和计算速度这两大要求的限制下也不宜使用。相对于这些算法来说,从算法精度和复杂度上考虑,基本CORDIC算法均非常具有优势。

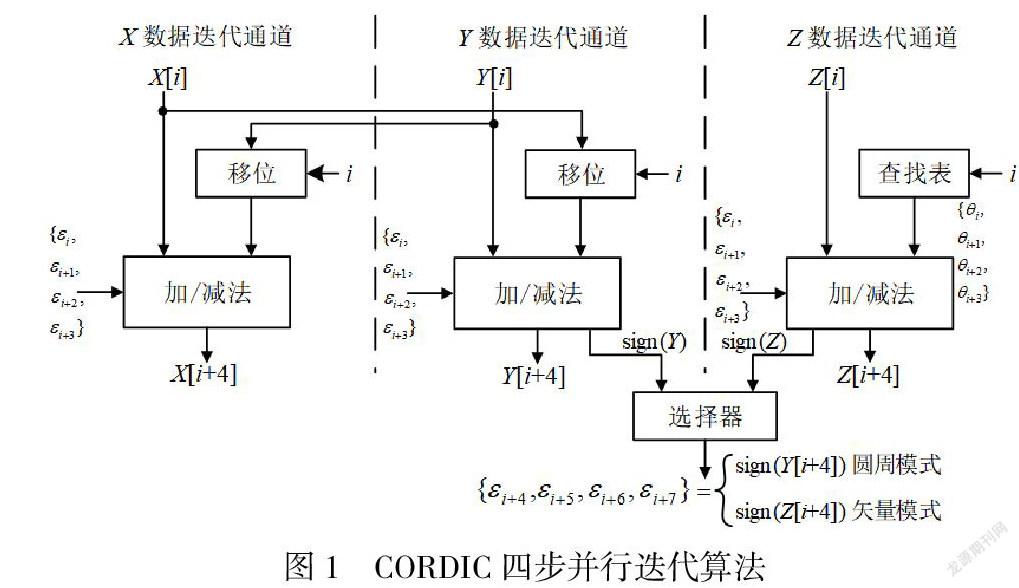

为了大幅提高计算的效率,基于双步CORDIC算法,本文采用了CORDIC四步并行迭代算法,用于双曲函数的计算。CORDIC四步并行迭代算法在一个时钟周期内合并四个连续时钟周期的单步迭代计算,即在一个时钟周期内得到4位位宽的有效计算结果。该算法的关键是在一个时钟周期内预测后四个连续时钟周期的判决因子ε的值。因此,该算法可以大幅减少基本CORDIC算法逐位迭代中的时延,将计算效率提升至四倍左右。其示意图如图1所示:

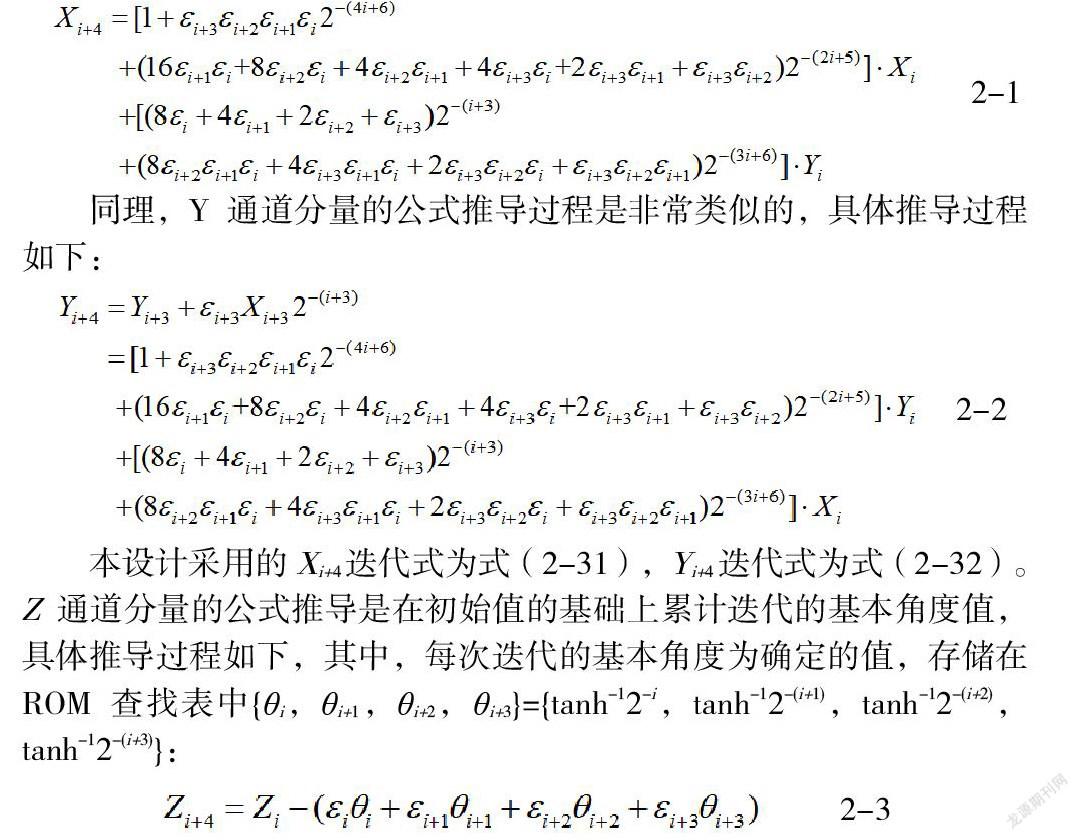

双曲函数的计算建立在CORDIC算法的双曲坐标系,下面将根据双曲坐标系的迭代公式进行CORDIC四步并行迭代算法的迭代式推导。首先,对于X通道分量,公式推导如下:

三、浮点双曲函数运算硬件单元的体系结构设计

在科学计算和工程设计中,双曲线函数的浮点运算占有重要的地位。同时,由于对计算速度和精度的要求不断改进,专用的FPU通常用于执行浮点运算。随着集成电路的快速发展,半导体工艺水平的不断提高,芯片集成程度大幅提高。通过牺牲一部分面积,可以实现高精度高速浮点运算的要求。本章设计和优化浮点计算单元的整体硬件架构,使用Verilog硬件语言实现双曲函数浮点计算单元。

表1列出了满足科学计算高精度要求的一些基本浮点数据格式和相关参数。本文使用表3-1中的128位浮点数据来计算双曲函数。128位浮点数据包括1位符号位S、15位指数位E和112位尾数位T。

根据对IEEE-754标准浮点数和CORDIC四步并行迭代算法原理的分析,双曲系浮点运算硬件单元包括预处理模块、CORDIC定点运算模块、后处理模块。根据双曲函数6个函数的定义式,将这6个函数分为3个总设计来实现,分别是sinh_cosh_tanh函数设计,arcsinh_arccosh函数设计和arctanh函数设计。

顶层结构表明了本设计在进行双曲系函数的计算时,首先,对输入浮点数据进行一定的预处理,接着,将预处理的结果输入到CORDIC定点运算模块中进行迭代计算,最后,将迭代计算的输出数据传入到后处理模块完成标准浮点数规则化。

CORDIC定点运算模块是设计的核心模块,主要包括X通道、Y通道和Z通道的四步并行迭代模块。

浮点规则化模块将CORDIC定点运算模块的运算结果转换成符合IEEE754浮点格式标准的数据,最终输出双曲系函数的128位浮点数值sinh_result、cosh_result、tanh_result、asinh_result、acosh_result和atanh_result。

四、浮点双曲函数运算硬件单元验证与比较

随着芯片系统的日益复杂,在硬件设计中,仿真验证已经成为非常重要的环节。本文使用Verilog语言对双曲函数浮点运算硬件单元中的各个模块进行RTL级建模,整合成3大顶层模块,用于计算6个双曲函数。利用Python的bigfloat函数运算库生成仿真数據集,在仿真工具ModelSim平台上对双曲函数浮点运算硬件单元中的重要模块和整体电路进行测试,然后将Python中的理想值与基于RTL设计的结果进行对比,最后基于TSMC 65 nm工艺,使用Synopsys 综合工具Design Compiler完成双曲函数浮点运算硬件单元的逻辑综合。

经过仿真验证后,利用Synopsys公司的设计工具在TSMC 65nm工艺下完成了DC综合,最终得到双曲函数运算单元的硬件面积和速度等综合结果。

综合结果如表2所示,从表中数据可知,本文提出的浮点双曲函数运算单元以面积换速度的策略实现高运算效率,同时保证精度达到设计要求。

由DC综合结果可知,本文提出的浮点双曲函数运算单元中CORDIC定点运算模块占据了大多数电路面积,因此,若需要进一步的优化,优先可对其作设计优化,以最大程度减少电路面积、降低电路功耗和提高运算性能。

五、总结

随着天体物理和天气及图像数据的高精度需求的增加,同时,随着人们对实时信息处理的要求不断提高,提升运算单元计算效率是十分有必要的。本文提出基于函數化的思想设计了128位的高精度浮点双曲函数的硬件电路。该电路不仅针对传统的CORDIC迭代算法进行了改善,同时在硬件结构中设计出并行的硬件结构,将时钟周期算短至41个,极大地提高了运算效率,减少了输入到输出的电路延时。后续进一步改进预测-修正算法,通过硬件模块复用以及割集重定时技术减少整体电路面积、功耗和关键路径的延时。

参考文献

[1]马群生,温东婵,仇玉章,唐瑞春.微计算机技术[M].北京:清华大学出版社,2006:64-68.

[2]崔林海,张子迎,姜占鹏,郭鑫.计算机组成原理与结构[M].哈尔滨:哈尔滨工业大学出版社,2015:236-237.

[3]侯力秩.DSP中的浮点与定点比较[J].通信电源技术,2020,37(01):105-106.

[4]韩山秀.浮点三角类超越函数的算法研究及硬件实现[D].西北工业大学,2006.

[5]Muller,J.M.Elementary Functions:Algorithms and Implementations,2nd ed.;Birkhauser:Basel,Swit-zerland,2006.

[6]Parhami,B.Computer Arithmetic:Algorithms and Hardware Designs;Oxford University Press:Oxford,UK,1999.

基金项目:

1:深圳市科技计划项目(项目编号:JCYJ20180307123857045)

2:广东省教育厅科技项目(项目编号:2019GKQNCX122)

3:校级科研项目(项目编号:SZIIT2019KJ026)