纳米线环栅隧穿场效应晶体管的电容模型*

2021-11-19芦宾王大为陈宇雷崔艳苗渊浩董林鹏

芦宾 王大为 陈宇雷 崔艳 苗渊浩 董林鹏

1) (山西师范大学物理与信息工程学院,临汾 041004)

2) (中国科学院微电子研究所,微电子器件与集成技术重点实验室,北京 100029)

3) (西安工业大学,陕西省薄膜技术与光学检测重点实验室,西安 710032)

纳米线环栅隧穿场效应晶体管相比于其他多栅器件具有更强的短沟道效应抑制能力及更优异的电学特性.器件模型能够模拟器件电学特性,对于器件及电路的实际应用极为关键.目前,已有纳米线环栅隧穿场效应晶体管的电流模型报道,但是尚没有电容模型的相关报道.电容模型主要用于瞬态特性模拟,对于评估电路速度转换和频率特性至关重要.由于没有可用的电容模型,纳米线环栅隧穿场效应晶体管电路方面的研究主要通过数值迭代的方法开展,该方法不仅对硬件平台要求高,且耗时长,还容易出现收敛性问题,只能勉强用于极小规模电路模块,对于包含晶体管数目较多的电路无能为力.本文针对以上问题,从基本的器件物理出发,建立了纳米线环栅隧穿场效应晶体管的电容模型,该模型不涉及任何数值迭代过程.相比于数值模型,该模型计算速度快、过程稳定,能够加速纳米线环栅隧穿场效应晶体管器件及电路的相关研究.

1 引言

金属氧化物场效应晶体管(metal-oxide-semiconductor field-effect-transistor,MOSFET)的特征尺寸随着摩尔定律不断缩减,使得集成电路集成度不断提高的同时,器件短沟道效应也越来越严重,导致其静态功耗已超过动态功耗成为集成电路的主要功耗来源.隧穿场效应晶体管(tunneling field-effect-transistor,TFET)是1 种利用量子隧穿机制导通电流的新型器件,其可以突破MOSFET室温下60 mV/dec 亚阈值摆幅极限,实现更加陡峭的开关曲线,同时降低泄漏电流及工作电压,进一步降低集成电路功率损耗[1-3].目前TFET 已成为微电子领域的研究热点,被认为是后摩尔时代最有可能取代MOSFET 推动高性能、低功耗集成电路持续发展的技术之一[4].

尽管TFET 能够实现十分陡峭的开关特性,但是TFET 也面临短沟道效应(short channel effects,SCEs)和漏感应势垒降低(drain-induced barrier lowering,DIBL)等非理想效应[5,6],这些效应导致TFET 特性退化,阻碍了TFET 器件及电路的实际应用.为了解决这些问题,研究人员在TFET结构上做出了很多创新,其中基于纳米线结构的环栅TFET (gate-all-around TFET,GAA-TFET)具有最高的沟道电势调控效率,能够在很大程度上抑制SCEs 和DIBL 等非理想效应[7],同时由于栅电极对隧穿结的控制增强,GAA-TFET 比其他多栅结构表现出了更低的亚阈值摆幅和更高的隧穿电流[6].

鉴于GAA-TFET 对非理想效应出色的抑制能力和优异的器件特性,人们针对GAA-TFET 的各个方面开展了大量研究,其中器件模型可用于计算器件及电路特性,对于GAA-TFET 器件及电路的实际应用极为关键.器件模型包括电流模型和电容模型,其中电流模型可用于计算电路稳态支路电流和节点电压,而电容模型可用于计算电路瞬态特性,评估电路的速度转换和频率特性.目前,针对GAA-TFET 的电流模型已有报道[7-12],但是尚未见其电容模型的报道.由于缺乏GAA-TFET 电容模型,目前研究人员主要通过数值迭代的方法开展GAA-TFET 电路设计方面的研究.但是,数值迭代对于硬件计算平台要求高,而且除了计算速度慢,耗时长外,还容易出现收敛性问题,仅能够勉强用于只包含几个器件的极小规模电路模块,对于包含成百上千个器件的电路,数值迭代方法则无能为力,这也是目前关于GAA-TFET 电路研究方面报道很少的原因之一.

本文针对以上问题,从基本的器件物理出发,建立了GAA-TFET 的电容模型,且该模型不涉及任何数值迭代过程.相比于数值模型,该模型计算速度快,计算过程稳定,能够加速GAA-TFET 器件及电路的相关研究.

2 模型推导

2.1 电势模型

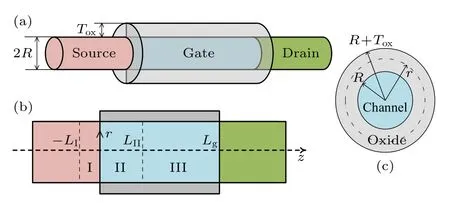

图1(a)为一个n 型GAA-TFET 的三维结构示意图,其中纳米线的半径R=7.5 nm,采用HfO2作为栅氧化层,介电常数εox=22,厚度为Tox=2 nm,栅金属功函数为4.2 eV.图1(b)是GAATFET 沿纳米线直径方向的剖面图,本文主要关注器件核心物理机理的分析,在模型推导过程中,暂不考虑短沟道效应等二次非理想效应的影响,因此器件栅长设置相对较长,为Lg=50 nm[7].源区、沟道和漏区的掺杂浓度分别为NS=1 × 1020cm—3(P 型),NC=1 × 1015cm—3(N 型) 和ND=5 ×1019cm—3(N 型).器件剖面图可划分为3 个区域,分别为源耗尽区I 区、沟道耗尽区II 区以及沟道积累区III 区,其中I 区和II 区的宽度分别为LI和LII.

图1(a) GAA-TFET 的三维结构示意图;(b) GAA-TFET沿沟道方向的剖面示意图;(c) GAA-TFET 垂直于沟道方向的剖面示意图Fig.1.(a) Three-dimensional structure of GAA TFETs.Schematic cross section of an n-type GAA TFET (b) along the channel and (b) normal to the channel direction.

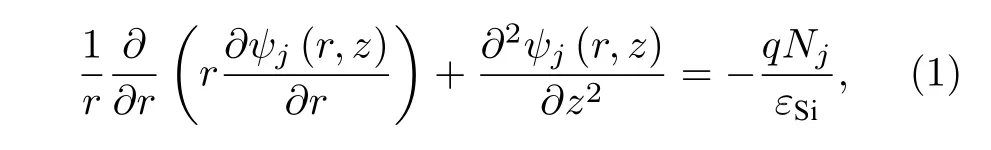

在柱状坐标系下,I 区和II 区的二维泊松方程如下:

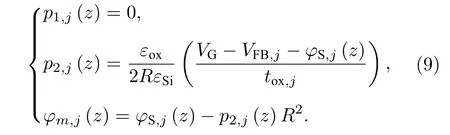

其中下标j=I,II;q为电子电荷;ψj(r,z)为二维电势分布;εSi为沟道介电常数;Nj为掺杂浓度.通过抛物近似[13],沿纳米线直径方向的电势可以写为

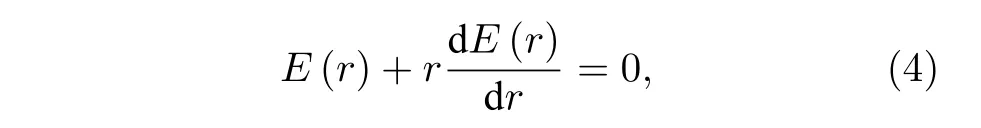

式中φm,j(z)为r=0 处沿着沟道中心线方向的电势分布;φm,j(z),p1,j(z)和p2,j(z) 是未知参量,可通过边界条件求得.由于器件的对称结构,可得沿直径方向的电场在r=0 处等于0,由此可得

其中φS,j(z)为r=R处沿沟道方向的电势分布,即表面电势.

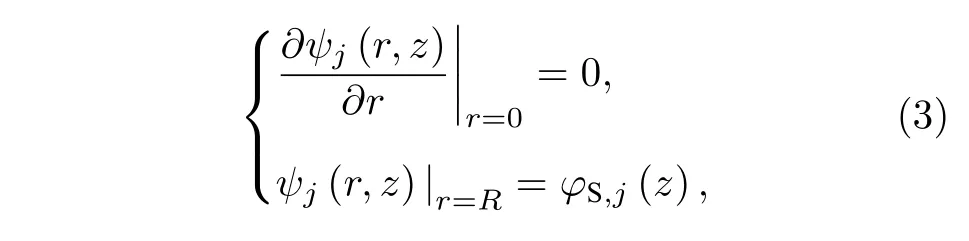

此外,在垂直氧化层与硅界面的方向上电位移矢量保持连续,为求解氧化层中靠近沟道界面处的电场,图1(c)给出了垂直沟道方向的截面图,对于任意半径为r的闭环,假设电场为E(r),沟道电荷为Q,根据高斯定理,得2πrLgE(r)εox=Q.对于某一固定栅电压,Q是1 个常数,因此对等式两边进行微分,可得

其通解为

其中F为常数.沟道表面电势与栅电极之间的电势差为

式中VFB为平带电压,VG为栅电压.由(6)式求得F并代入(5)式可得

由此可以得到栅氧化层中沟道附近的电场为E(R)=(VG-VFB-φS(z))/tox,其中tox=Rln(1+Tox/R)相当于平面器件中的栅氧化层厚度.需要注意的是,在平面器件中,考虑栅氧化层边界泄漏电场对I 区的影响,I 区可被等效为环绕了一层厚度为πtox/2 的氧化层[14].由此根据电位移矢量连续可得

其中对于I 区,tox,j=πtox/2,对于II 区,tox,j=tox.联立求解(3)式和(8)式可得

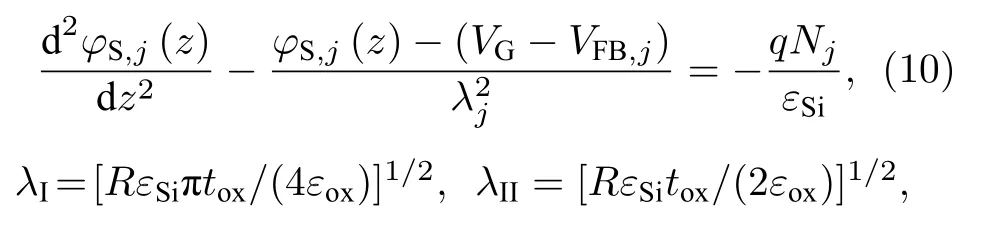

把(2)式与(9)式代入(1)式,即可得到简化的一维泊松方程:

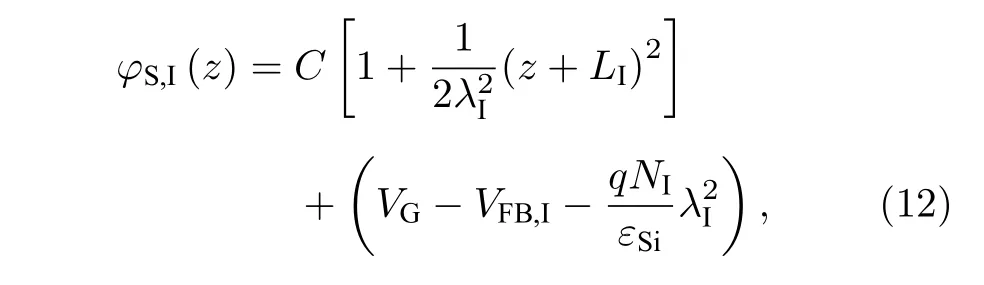

(10)式的通解为

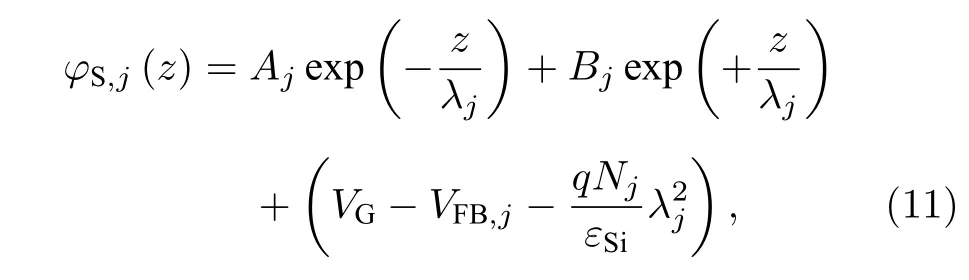

其中Aj和Bj为待求解系数.对于I 区,将(11)式在z=—LI附近展开并仅保留常数项与二次项,可以得到I 区的表面电势为

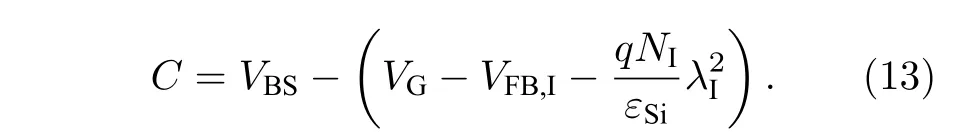

其中C未知,可以通过边界条件φS,I(-LI)=VBS求得,VBS=VS-Vtlog(NI/ni,I) 为中性源区电势,VS为源电极电压,Vt是热电压,ni,I是本征载流子浓度,求得C为

将(13)式代入(12)式求得I 区表面电势分布为

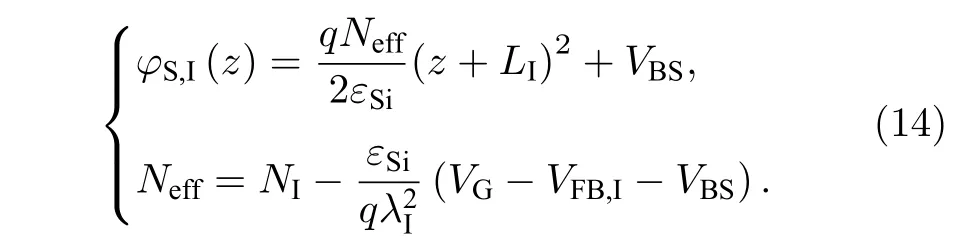

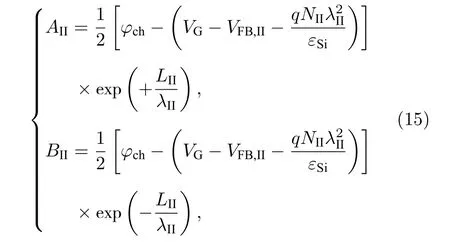

对于II 区,II 区与III 区边界面上的电场和电势保持连续,然而需要注意的是III 区为积累区,在III 区中存在高浓度的电子,这些电子在很大程度上屏蔽了栅、漏电场的作用,因此III 区中的电场很小,为了简化模型推导,假设III 区中电场为零,即可求得系数AII和BII:

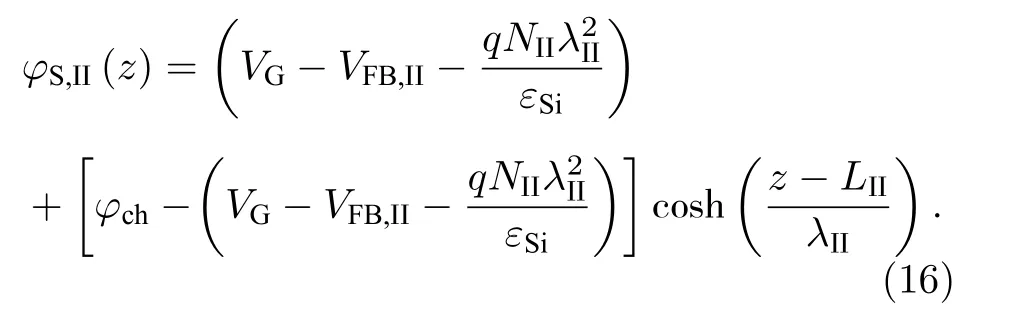

式中φch是III 区表面电势,将(15)式代入(11)式,求得II 区表面电势分布为

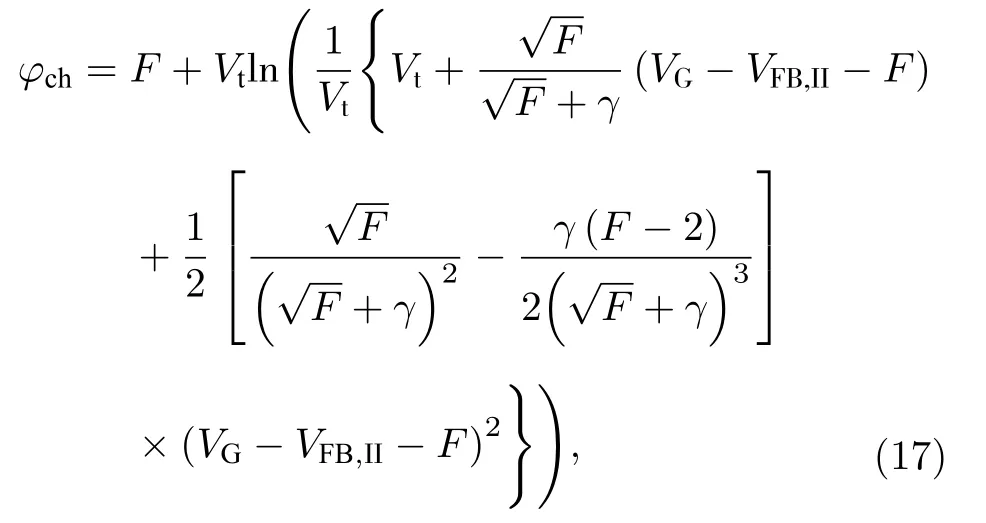

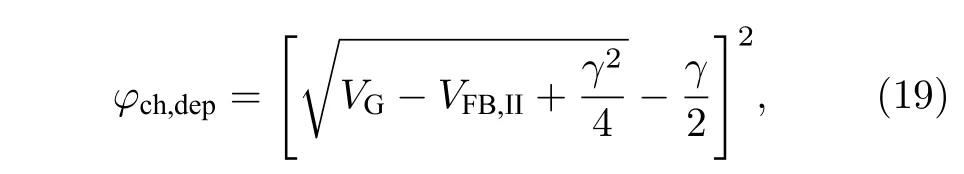

对于III 区,其表面电势φch可写为[15]

其中F和φch,dep为

式中γ=(2εSiqNII)1/2/(εox/tox),δ=0.04 为平滑因子,φ=Vtln(Ninv/ni,II) 是屏蔽电势,Ninv=2.5 ×1019cm—3是1 个从TCAD 仿真中提取出来的经验参数.

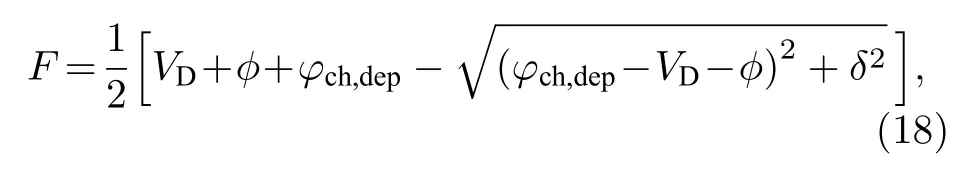

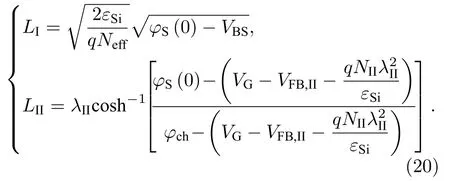

至此未知量只剩I 区和II 区的宽度LI和LII.假设z=0 处,即I/II 界面处表面电势为φS(0),由(14)式和(16)式可以得到LI和LII如下:

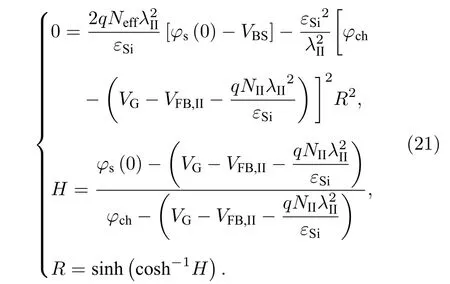

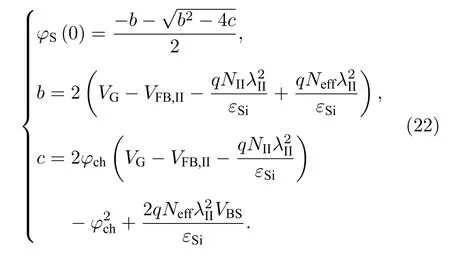

φS(0)是目前唯一的未知量,为了求解φS(0),可将LI和LII分别代入(14)式和(16)式,利用z=0处电势连续,可以得到φS(0)满足如下方程:

借助公式变换sinh(cosh-1H)=(H2-1)1/2,求解(21)式,可得φS(0)为

2.2 电容模型

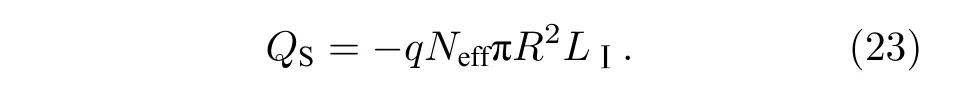

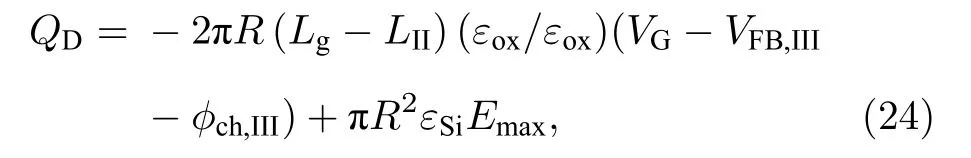

在TFET 中,源区与沟道区之间的隧穿结本质上是个高势垒的反偏结,势垒两侧载流子很难通过热发射相互流通,因此,可以假设源电荷QS主要为势垒左侧的源区耗尽区电荷,而漏电荷QD主要为势垒右侧的电荷,这样器件源端电荷QS可以表示为

漏端电荷QD主要包括沟道中III 区中的可动载流子以及漏区边缘电荷:

其中Emax=(VBD—φch)/λII,VBD=VD+Vt×log(ND/ni)为中性漏区电势,VD为漏电极电压.栅电荷QG、源电荷QS和漏电荷QD满足电荷守恒关系:

将端电荷分别对相应的端电压进行求导便可得到端电容,然而由于上述电势的表达式十分复杂,难以推导出解析的导数表达式.采用差分的方式,求解端电容的表达式如下:

式中Cgg,Cgs和Cgd分别为栅电容、栅源电容和栅漏电容,ΔV为差分步长.

3 模型验证

通过TCAD 二维数值仿真验证所建立模型的准确性,为了能够考虑非均匀电场对隧穿过程的影响,TCAD 仿真采用非局域带带隧穿模型计算载流子隧穿路径和概率.此外,还考虑了掺杂相关的迁移率模型、高电场速度饱和模型以及Shockley-Read-Hall 复合等模型.

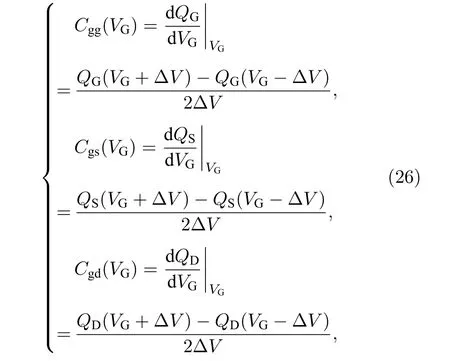

图2 给出了所计算的表面电势分布,模型计算结果与TCAD 结果符合一致,表明所建立的电势模型的准确性.图2(a)为VD=1.0 V 时不同VG下的电势分布,可以看到,随着VG的增大,沟道电势逐渐升高,隧穿结附近电势逐渐变得陡峭,意味着隧穿电场也在逐渐变大,因此隧穿概率和电流也会随着VG增大而逐步增大.然而,当VG逐步增大到1.2 V 后,表面电势的升高开始放缓,这是由于随着电势的升高,沟道中感应出了大量可动载流子,屏蔽了VG对表面电势的影响.

图2 表面电势随不同的 (a) VG 和(b) VD 的变化Fig.2.Variation of surface potential with different (a) VG and (b) VD.

虽然沟道中感应出的大量载流子弱化了VG对沟道电势的控制效率,但是也减小了沟道电阻,使得漏电场很容易穿透进入沟道,甚至到达隧穿结附近,调控隧穿电场及隧穿电流,如图2(b)所示.在VG=1.1 V 时,沟道电势随VG增大而增大,然而当VD增大到1.0 V 以后,沟道电势几乎不随VD变化而变化,这是因为随着VD的增大,沟道中大量载流子被吸引回到漏区,沟道逐步变为耗尽状态,沟道电阻增大,漏电场无法穿透进入沟道,而是被阻挡在沟道与漏区界面附近,因此VD失去了对沟道电势的调控能力,这时沟道电势又回到受VG控制的状态.

由以上分析可以发现,沟道电势是受到VG和VD的交替调控的,当沟道处于耗尽状态时,主要受到VG控制;当沟道处于积累状态时,主要受到VD控制.

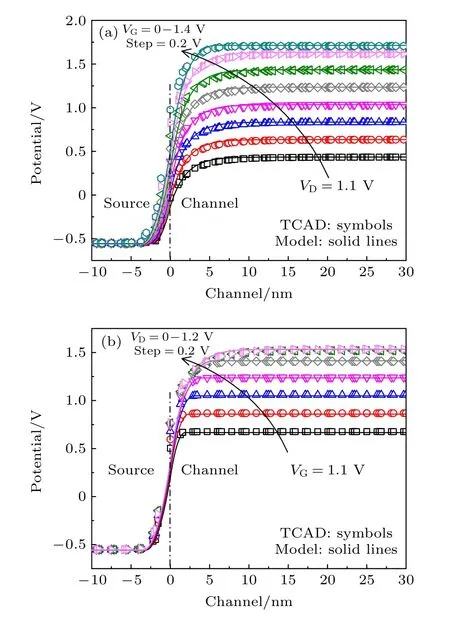

图3 是各个端电荷随偏置电压的变化情况.可以看出,QG主要由QD组成,而QS的影响很小,几乎可以忽略.此外,QG随着VG的增大而增大,随着VD增大而减小,这是因为栅电场的影响是把电子从漏区吸引到沟道中,倾向于使得沟道变为积累状态,而漏电场的影响则是把沟道中的电子吸回到漏区,倾向于使沟道变为耗尽状态,这与VG和VD对沟道电势的交替调控作用是一致的.

图3 端电荷随不同的 (a) VG 和(b) VD 的变化Fig.3.Variation of terminal charges with different (a) VG and (b) VD.

图3(a) 中的插图给出了QS随VG的变化情况.可以看出,QS随着VG增大而增大,QS主要取决于源区耗尽宽度LI,随着VG增大,隧穿结附近电势升高,源耗尽宽度展宽,因此QS变大.然而,图3(b)插图中QS随VD的变化情况与VG有所不同,随着VD增大,QS先是逐渐增大,而后保持不变,这是由于沟道中载流子浓度较高时,沟道电阻较小,漏电场可以穿透沟道,到达隧穿结附近,调控隧穿结附近电势及源耗尽宽度LI,但是随着VD增大,沟道载流子浓度降低,电阻变大,漏电场失去了对隧穿结附近电势的控制,因此LI和QS也不受VD调控.

模型计算的端电荷与TCAD 结果取得了较好的一致性,QS的计算误差较大是因为在计算I 区内耗尽电荷时,简单地把I 区看作一个圆柱体,也就是在图1(b)中将I 区作为一个矩形处理,实际上φS(0)在整个源/沟道界面上是变化的,因此I区的耗尽宽度在r方向上并非常数,也就是图1(b)中I 区的形状并不是严格的矩形.矩形假设以及在I 区电势推导中采用的泰勒级数展开所引入的误差,最终导致QS计算偏差较大,但是所建立的模型从基本的器件物理出发,仍然能够正确地解释QS随偏置电压的变化趋势和规律.

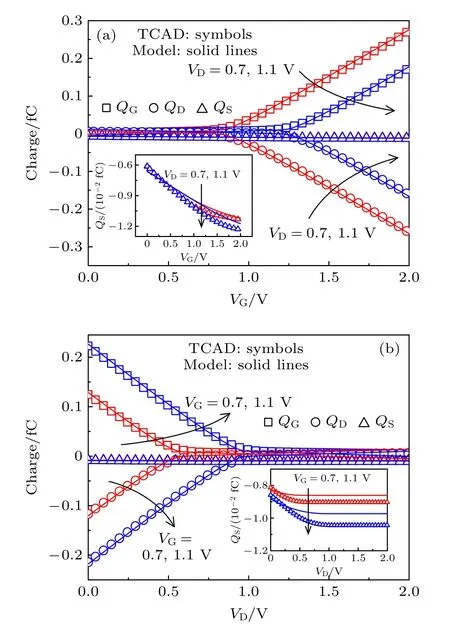

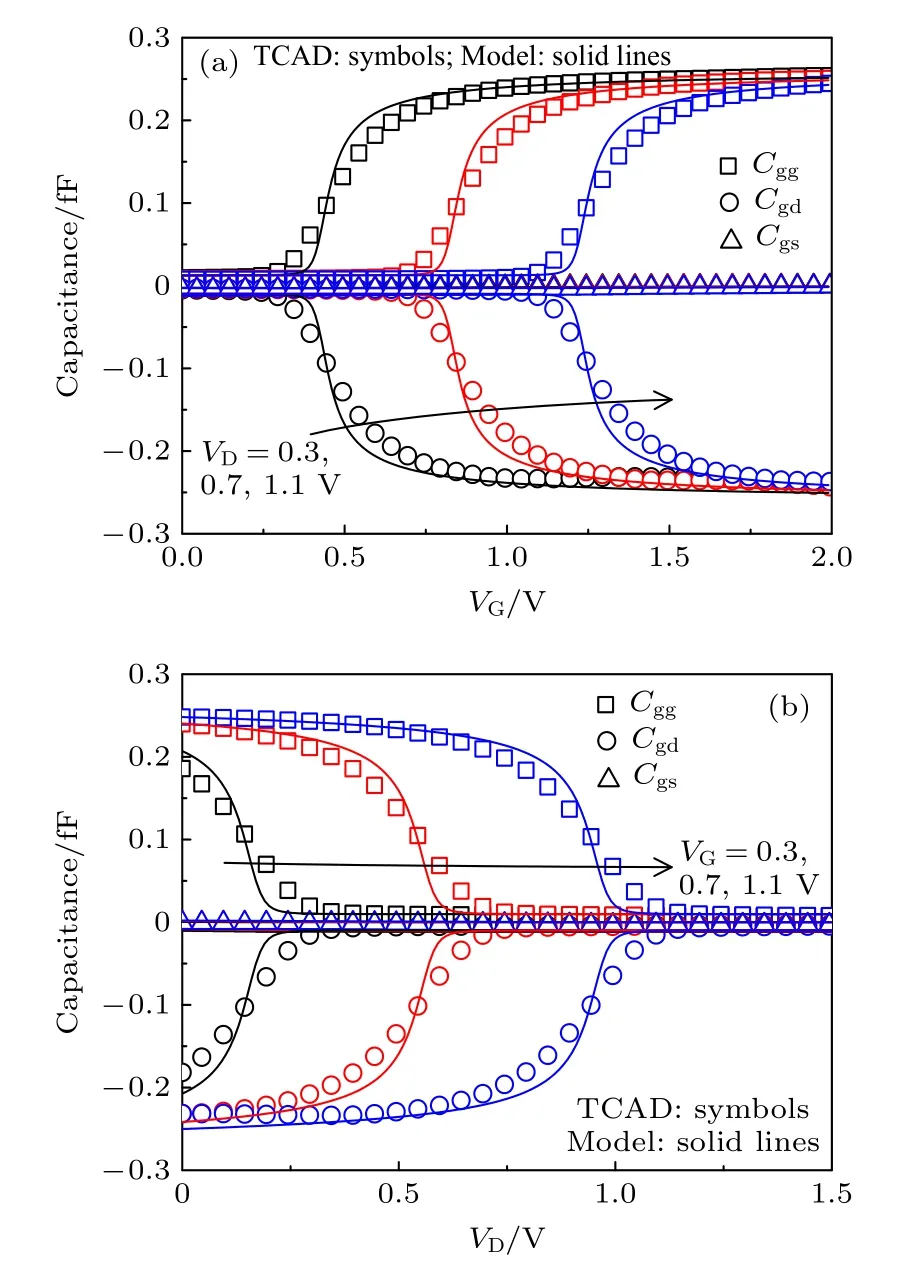

图4 给出了模型和TCAD 所计算的电容特性.可以看出,模型所计算的电容与TCAD 结果取得了很好的一致性,能够准确描述电容变化的基本规律.Cgg随VG增大而增大,随着VD增大而减小,与图3 中端电荷的变化规律一致.此外,还能够看到,栅电容Cgg主要由栅漏电容Cgd组成,栅源电容Cgs的贡献几乎可以忽略,这就导致GAA-TFET具有较大的米勒电容.在数字电路中,米勒电容效应将引起大的信号过冲以及延迟,不利于电路特性的提升,这一效应的影响可以通过采用异质栅结构进行缓解.

图4 端电容随不同的 (a) VG 和(b) VD 的变化Fig.4.Variation of terminal capacitances with different (a)VG and (b) VD.

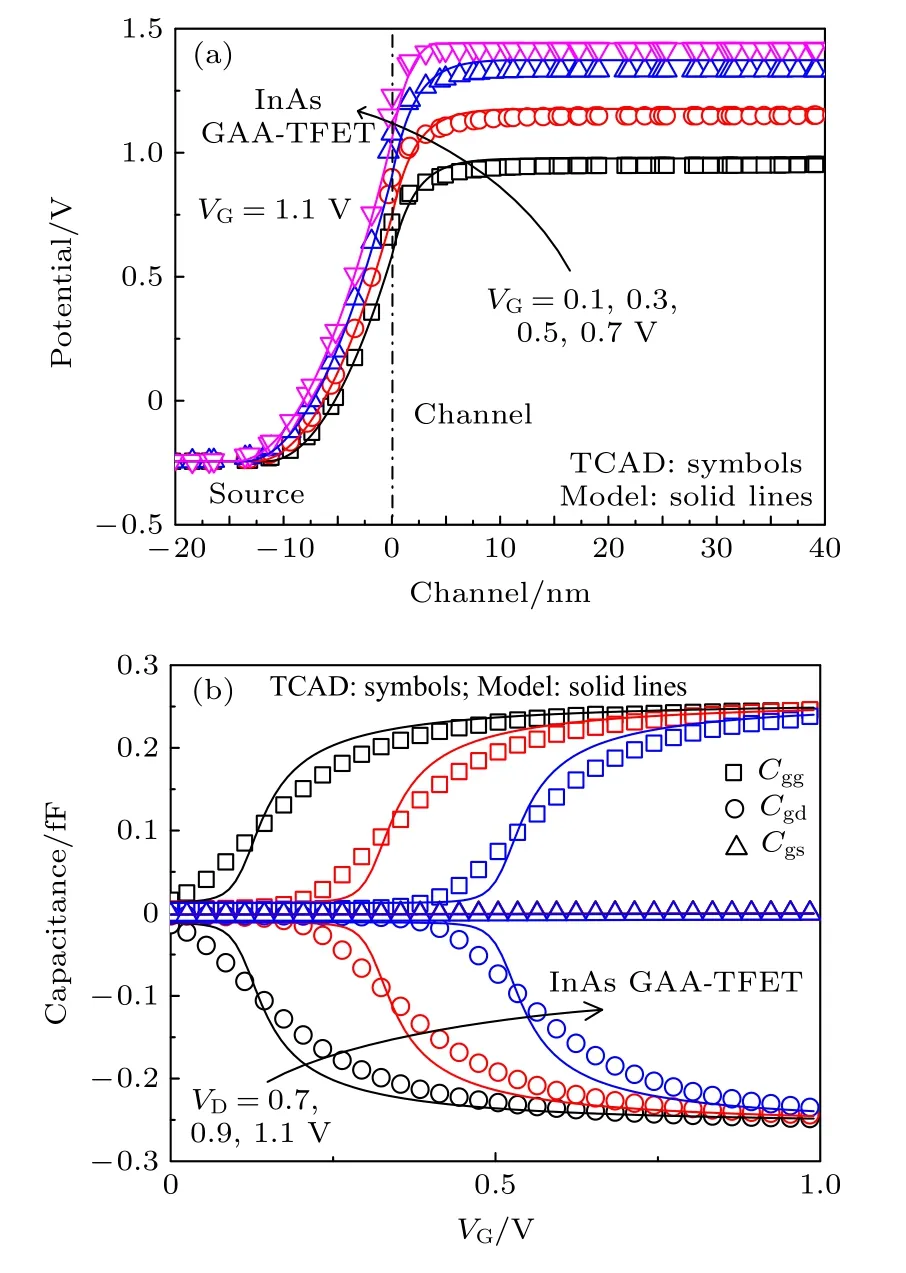

另外,需要注意Si 材料禁带宽度大,且属于间接带隙半导体,载流子隧穿需要额外声子辅助,载流子隧穿概率和隧穿电流十分低,难以满足器件实际应用需求[3].相比之下,InAs 材料禁带宽度窄,属于直接带隙,利于提高载流子隧穿概率,提高TFET 器件特性[16].从以上分析可以看出,虽然本文主要研究了Si 基GAA-TFET 器件,但是模型推导并非针对某一特定材料,因此,本文所提出的模型具有一定程度的材料普适性,能够适用于更适合TFET 设计的InAs 等III-V 族材料.图5 给出了模型所计算的InAs GAA-TFET 器件表面电势及端电容特性,可以看到模型能够精准预测器件表面电势变化,准确描述器件电容基本变化规律.

图5 InAs 基GAA-TFET 器件(a)表面电势和(b)端电容随VG 的变化Fig.5.Variation of the (a) surface potential and (b) terminal capacitance with different VG for an InAs based GAA-TFET.

4 结论

本文从GAA-TFET 的基本器件物理出发,建立了其表面电势和电容模型,所建立模型计算结果与TCAD 数值计算结果取得了很好的一致性,能够准确描述GAA-TFET 中栅、漏电压对表面电势的交替调控原理以及端电容的变化规律,表明所建立模型的准确性.此外,所建立的模型不涉及任何数值迭代过程,相比于数值模型,该模型计算速度快,计算过程稳定,能够用于GAA-TFET 器件及电路的相关研究.