一种新型低冗余抗多节点翻转的加固D 锁存器设计∗

2021-11-13李强,张楠,郭靖

李 强,张 楠,郭 靖

(中北大学仪器与电子学院,山西 太原 030051)

集成电路工艺的不断发展导致了器件尺寸不断的减小,从而使得器件敏感区域的临界电荷值不断降低。因此,当环境中的辐射粒子轰击器件的敏感区域时,其耗尽区中的反向电场会将产生的大量电子-空穴对收集,其中P 型MOS 管器件收集多余的空穴,而N 型MOS 管器件收集多余的电子。一旦收集到的电荷超过器件的临界电荷值,就会导致单粒子翻转(Single Event Upset,SEU)现象发生。SEU 在航空航天以及地面高辐射领域中尤为明显,虽然它们不会永久地破坏电路本身,只是将值暂时翻转到其互补值,直到下一个时钟周期来临,但是将会引起电子系统的功能紊乱[1]。当存储电路如D 锁存器中某个单一节点被轰击,即发生单节点翻转(Single Node Upset,SNU)时,该节点的电压值将会发生改变,由于其电路中含有交叉耦合形成的反馈回路,因此其他节点也将发生翻转[2-3]。然而,在目前使用的先进纳米工艺中,晶体管之间的距离、节点寄生电容以及电源电压均越来越小,在电荷共享效应的影响下,多个节点同时发生翻转就成为了可能,即为多节点翻转(Multiple-Node Upset,MNU)[4]。因此,为了确保D 锁存器锁存的数据不受影响,设计能够抵抗MNU 的加固D 锁存器就变得十分重要。

文献[5]和[6]中分别提出了两种加固D 锁存器电路结构,但是均只能实现对MNU 的屏蔽而不是恢复容错,这将导致输出节点处于高阻抗状态,从而消耗更多的漏电功耗;同时,该高阻节点也将更容易被漏电改变其锁存的值。虽然文献[7]提出的加固D 锁存器可以对MNU 进行容错恢复,但是其所用的晶体管数高达70,这将使得电路的硬件开销变得非常大。为解决这一问题,本文设计了一个硬件冗余较小且又能实现MNU 恢复容错的D 锁存器。

1 本文构造的锁存器

1.1 电路结构分析

根据辐射翻转机制可知,SEU 翻转极性与被轰击晶体管类型有关,即当轰击PMOS 晶体管时只发生0→1 的瞬态脉冲或翻转;而当轰击NMOS 晶体管时则只发生1→0 的瞬态脉冲或翻转。因此,可利用这一机制通过在电路上进行改进设计,使其在某些节点上只产生单一极性的翻转,来减小电路敏感节点和硬件开销。

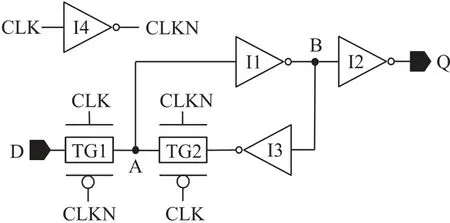

基于上述加固机制,本文构造了一个新型低冗余抗MNU 的加固D 锁存器,其电路结构如图1 所示。该电路共由42 个晶体管构成,其中晶体管TN1~TN20 为20 个NMOS 晶体管,而晶体管TP1~TP20为20 个PMOS 晶体管。反相器I1 产生CLK 的互补信号CLKN。因此,该电路中端口信号包括:D,CLK以及Q,其中端口D 为输入数据端口;端口CLK 为输入时钟端口,而输出端口为Q 端口。

图1 构造的加固D 锁存器电路图

该电路中内部节点为S1~S8,晶体管TP17~TP19 以及TN13~TN15 由内部节点控制用来锁存输出节点Q 的值。因此,当CLK=1 时,该锁存器处于导通状态,而当CLK=0 时,该锁存器则处于锁存状态。TP20 和TN20 构成一个传输门,用来将输入信号D 传输到输出端口Q。当CLK=1 时,TN16~TN19 根据输入信号D 的值驱动内部节点S1、S4、S5、S8 分别处于高电平1 或低电平0。由于辐射电压翻转极性由被轰击晶体管类型而决定,因此,TN1、TN2、TN5~TN8、TN11 及TN12 管可以用来确保当节点S1、S2、S5 和S6 被轰击时,其值不会被改变为高电平1(不会收集正电荷),从而减少了电路内部敏感节点和晶体管数。

1.2 时序分析

本文构造的新型加固D 锁存器为高电平导通、低电平锁存,具体工作过程为:

(1)传输模式(CLK=1):假设输入端D=1,当CLK=1 时,CLKN=0,该锁存器的输出Q=D=1,TP20 和TN20 处于导通状态;同时,TP19 和TN13被关闭,TN16~TN19 被打开,所以S1=S4=S5=S8=1。此时,TN2 和TN9 导通,使得S2=S7=0;TN3 和TN8 导通,使得S3=S6=0。因此,TP1、TP4、TP5、TP8、TP9、TP12、TP13、TP16、TN1、TN4、TN6、TN7、TN10、TN12、TN14 和TN15 被关闭,剩余晶体管被打开,此时反馈锁存环将被成功地建立。而当D=0时,Q=0;由于TN16~TN19 仍处于导通状态,所以S1=S4=S5=S8=0,且S2=S3=S6=S7=1,从而使得TP2、TP3、TP6、TP7、TP10、TP11、TP14、TP15、TN2、TN3、TN5、TN8、TN9、TN11、TP17 和TP18 被关闭,而剩余晶体管则被打开。因此,当D=0 时,反馈环也能正确地建立。

(2)锁存模式(CLK=0):当CLK=0 时,锁存器进入锁存模式。此时TP20 和TN20 被关闭,TN13和TP19 被打开:当S3=S7=0 时,TP17 和TP18 被打开,输出端口Q 将被连接到VDD,此时Q=1;而当S3=S7=1 时,TN13 和TN14 被打开,所以输出端口Q 将被连接到GND,此时Q=0。

1.3 敏感节点

根据辐射翻转机制,电路中的敏感节点主要是那些处于关闭状态晶体管的漏/源极。在本文构造的新型抗MNU 锁存器中,其敏感节点(依赖于电路中锁存的值)为:

(1)当Q=1(即电路锁存1)时,敏感节点为S1、S3、S4、S5、S7 和S8 这6 个内部节点,F3、F5、F6、F9、F11、F12 和F13 这7 个悬空节点及输出节点Q(Q=F14=F15)。此时节点S2 和S6 不是敏感节点,因为在电路设计上,通过引进两个NMOS 晶体管TN6 和TN12 将这两个节点与P+注入区隔离。因此,当这两个节点被轰击时,由于它们是N+注入区,因此只能收集负电荷,而收集的负电荷只能将其值拉到更低(小于GND),但是仍旧是0 逻辑,这并没有改变这两个节点的锁存值。节点F1、F2、F4、F7、F8、F10 和F16 不是敏感节点,因为它们处于导通的反馈路径中。

(2)由于电路结构对称性,同理可得,当Q=0(电路锁存0)时,敏感节点为S2、S3、S4、S6、S7、S8、F1、F2、F4、F7、F8、F10、F16 及输出节点Q(Q=F15=F14)。

1.4 容错分析

下面将对本文构造的加固D 锁存器进行容错分析,假设时钟CLK=0,S1=S4=S5=S8=1,S2=S3=S6=S7=0 且Q=1:

(1)当任意一个内部敏感节点发生翻转时,该D 锁存器均可以对其进行容错恢复。例如,当节点S5 发生翻转时,TN8 和TN3 被关闭且TP16 被打开;S6、S7 和S8 节点保持原来的值,导致TP11、TP13 和TN11 被打开,节点S5 可被快速恢复。

(2)当任意一个悬空敏感节点发生翻转时,其收集的电荷由于缺乏导通路径,从而无法对其他节点产生影响,所以不会改变电路锁存的值。例如,当节点F3 发生翻转时,积累的电荷不会流动去影响其他值,因此不会改变电路锁存的值。

(3)当输出节点Q 翻转为0 时,由于节点S3 和S7 保持不变,所以Q 的值将通过导通的TP17~TP19 恢复到高电平1。

(4)当任意两个内部敏感节点发生翻转时,该D 锁存器可以依赖内部反馈机制将翻转的节点进行恢复。例如,当电荷共享翻转内部敏感节点S3 和S4 时,TN6 被打开且TP3、TP6 和TP10 被关闭;同时,TN5 被关闭且TP5、TP4 和TP9 被打开。但是,由于节点S5 保持原值,所以TN3 被打开,从而节点S3 的值将被恢复;随后,TP6 将被打开。由于TP2、TP6 处于导通状态,所以节点S4 值也可以被快速恢复。

(5)当电荷共享同时影响两个悬空敏感节点时,由于其积累的电荷缺乏导通路径,所以将不会影响其他节点,电路锁存的值也将不会发生改变。例如,当节点F3 和F5 发生翻转时,积累的电荷将被限制在各自节点,因此,电路锁存的值将不会发生改变。

(6)当电荷共享导致一个内部敏感节点和一个悬空敏感节点(或输出节点)发生翻转时,可将其看成是在一个内部敏感节点和一个悬空敏感节点(或输出节点)处分别发生单个SNU。由于悬空敏感节点(或输出节点)发生的SNU 不会影响其他节点值,那么这类MNU 可看成是只有一个内部敏感节点发生翻转,因此这类MNU 同样也是可以被恢复的。例如,当节点S1 和F3 发生翻转时,TN2 和TN9 被关闭同时TP8 被打开,由于S2、S3 和S4 节点继续保持原来的值,所以节点S1 可以被导通的TP3、TP7和TN5 恢复,同时节点F3 翻转不会改变电路中晶体管的工作状态,其他节点将保持各自的原有值,因此电路锁存的值将不会发生改变。

由于构造的加固D 锁存器在结构上具有对称性,所以当电路锁存低电平0 时,发生的SNU 和MNU 也均可以被恢复。综上所述,本文构造的新型加固D 锁存器可以直接在电路级对所有的SNU 和MNU 进行恢复容错,从而确保电路锁存正确的值。另外,由于该锁存器是利用电路结构设计来进行的容错,因此工艺节点参数的变化不会对其容错功能造成影响,即该锁存器可在任何工艺节点下进行再设计。

2 仿真验证和硬件开销比较

2.1 仿真验证

基于“双双指数电流源”故障注入模型[8],利用Cadence Spectre 工具,在TSMC 65nm CMOS 工艺下对本文构造的新型加固D 锁存器进行时序和容错后仿真,其仿真结果如图2 所示(为了更为清晰地显示恢复容错结果,该图只显示了内部节点和输出节点翻转恢复情况):当CLK=1 时,输出信号Q 随输入信号D 值的变化而变化,而当CLK=0 时,输出Q 仍然能锁存正确的值。以锁存高电平1 为例,当节点S1、S3、S4、S5、S7 和S8 分别发生单节点翻转时,观察时序波形可发现这些节点值均能被恢复从而确保输出Q 锁存正确的值。当内部敏感节点S1和S3、S1 和S4、S1 和S5、S1 和S7、S1 和S8、S3 和S4、S3 和S5、S3 和S7、S3 和S8、S4 和S5、S4 和S7、S4 和S8、S5 和S7、S5 和S8 以及S7 和S8 分别同时发生翻转时,这些节点对的值也能够被恢复,故输出Q 仍然锁存正确的值。

图2 时序和容错仿真验证

通过上述时序及容错仿真验证结果可知,本文构造的锁存器不仅能够实现正确的传输及锁存功能,还可以实现对SNU 和MNU 的恢复容错。

2.2 硬件开销比较

表1 列出了现有一些加固锁存器所用的晶体管数、敏感节点数、临界电荷Qcrit及其容错类型。传统锁存器电路如图3 所示,其仅需14 个晶体管就可实现传输和锁存功能,但是并不具有任何SNU 和MNU 恢复容错的能力。文献[9]提出的两个锁存器虽然具有较少的晶体管数和敏感节点数,但是它们均只能对SNU 进行恢复容错。相比于文献[9-10]提出的锁存器具有更多的敏感节点数,但是其仍然只能对SNU 进行恢复容错。文献[5-6,11-12]提出的锁存器电路虽然具有较少的敏感节点,但是均只能对MNU 进行屏蔽容错而无法将翻转节点恢复。文献[13-14]提出的锁存器使用了较少的晶体管和敏感节点,且实现了对MNU 的恢复容错,但是将具有更大的延时和功耗开销(见图4)。文献[7]提出的加固锁存器不仅能够实现恢复容错,而且降低了延时和功耗开销。然而,该电路所用晶体管数将急剧增多,极大地增加了电路面积。本文构造的加固D 锁存器不仅能够实现对MNU 的恢复容错,而且晶体管数相对较少;同时由于该锁存器在设计过程中使用了辐射诱导脉冲翻转机制,从而使得电路中敏感节点数要小于其节点数(其他锁存器的敏感节点数均等于其节点数)。相比于文献[13-14]构造的锁存器,本文构造的锁存器的临界电荷Qcrit被减小,这是因为本文构造的锁存器使用小尺寸设计和存在阈值损失的缘故。然而,由于本文构造的锁存器在发生翻转后仍旧可以将其恢复,因此临界电荷Qcrit的减小并不会影响其容错性能。

表1 晶体管、敏感节点数和Qcrit比较结果

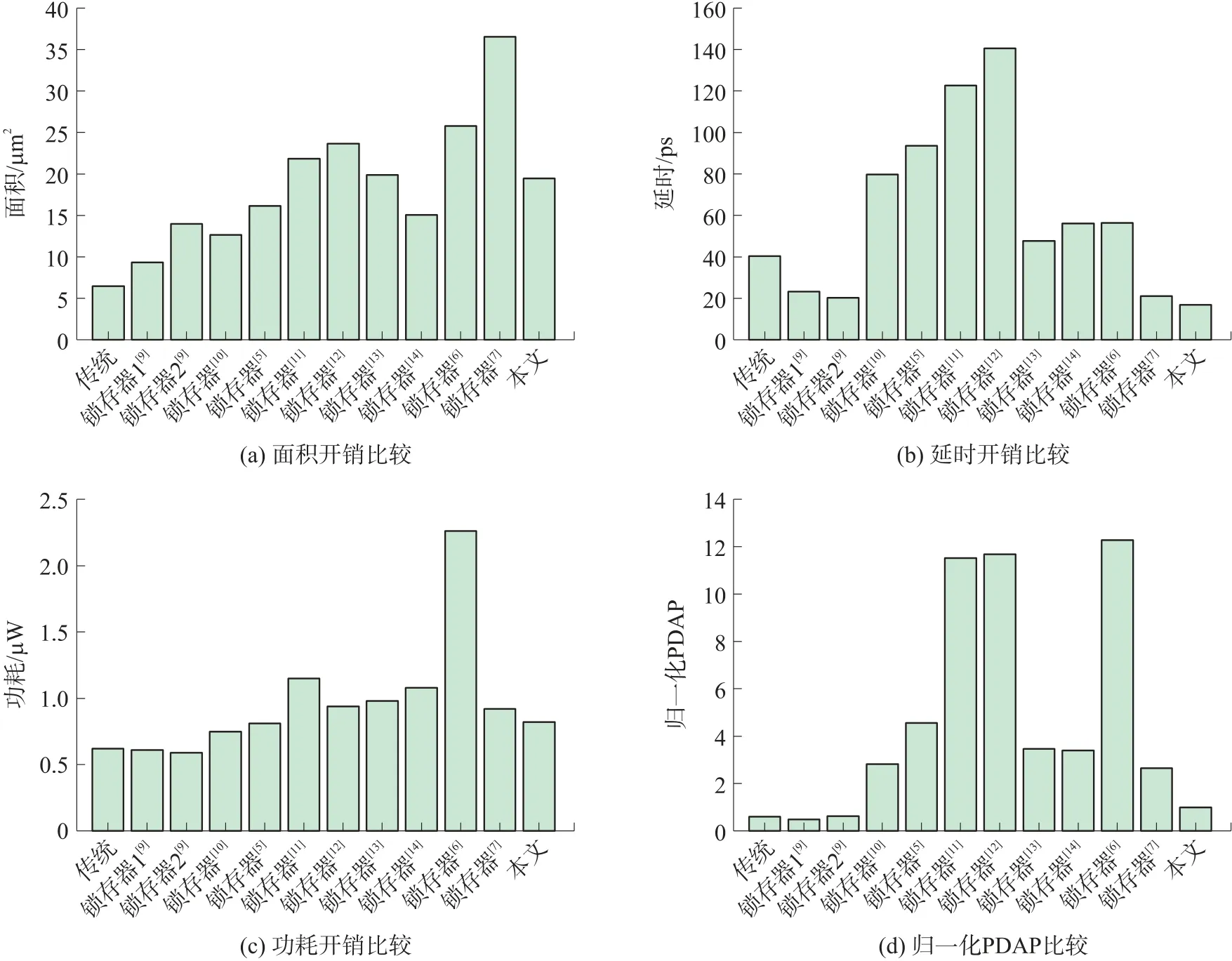

图3 传统锁存器电路

图4 对不同锁存器的面积、延时、功耗以及功耗-面积-延时之积(PDAP)硬件开销进行了对比。从图中看出,文献[9]和文献[10]提出的锁存器具有相对较小的面积、延时和功耗,但是其分别只能进行SNU 屏蔽容错和SNU 恢复容错。文献[5]和文献[6]提出的锁存器能够对MNU 进行屏蔽容错,但是其面积、延时和功耗相对较大。文献[7]构造的锁存器虽然能够对MNU 进行恢复容错并具有相对较低的延时和功耗开销,但是由于其电路中使用了较多的晶体管数(70),从而使得其面积开销最高。为了进行硬件开销的综合对比,本文使用了PDAP 这一硬件开销评价标准。图4(d)给出了不同锁存器的PDAP 比较结果。从该图中可知,本文构造的低冗余加固锁存器在所有抗MNU 锁存器中具有最小的硬件开销。相比于文献[7]、[13]和[14]提出的锁存器,本文构造加固锁存器的PDAP 可分别减少62.3%、71.2%和70.6%。

图4 硬件开销比较

3 电荷收集能力比较

为了进一步验证该电路抗MNU 的能力,图5 对不同锁存器的抗MNU 可靠性进行了比较,其中横坐标表示电路中主要节点收集的辐射诱导电荷,纵坐标表示次要节点收集的辐射诱导电荷。曲线与横、纵坐标所围面积的大小可反映该电路的抗MNU的能力[15]。从图中可看出,传统锁存器的曲线与横纵坐标都相交,因而其不具有抗SNU 的能力;文献[9]和[10]提出的锁存器曲线不与横纵坐标相交,因此具有抗SNU 的能力,但是由于所围面积较小,导致其抗MNU 的能力较差。本文构造的加固锁存器曲线与文献[5-7,11-14]锁存器的曲线重合,因而具有跟这些现有加固锁存器一样的抗MNU能力。

图5 电荷收集能力对比

4 结论

本文基于辐射脉冲翻转机制构造了一个新型低冗余抗MNU 加固锁存器,并在TSMC 65 nm CMOS工艺下进行了时序和容错功能仿真,验证结果表明该加固D 锁存器不仅时序功能正确,而且能对所有敏感节点的SNU 和MNU 进行恢复容错。与现有抗MNU 锁存器硬件参数的比较结果表明,本文构造的新型加固D 锁存器具有最小的硬件开销。