一种用于ADC 采样的高精度时钟占空比校正方法∗

2021-11-13郭仲杰苏昌勖曹喜涛

郭仲杰,刘 申,苏昌勖,曹喜涛,李 晨,韩 晓

(西安理工大学自动化与信息工程学院,陕西 西安 710048)

传统的占空比校准电路分为有反馈环路的模拟方法和无反馈的数字校正方法。文献[2]提出了脉宽控制回路,利用异或同或逻辑PD 作为相位检测器,通过低通滤波器对占空比的偏差进行不断积累,并通过共模反馈比较器来对基准电压和输出信号的共模电压进行比较来控制共模反馈电压,从而达到输出所需的共模电压来调整时钟信号占空比。在文献[3]中,通过比较低通滤波器输出的直流分量和参考电压来调整时钟信号占空比,同时降低功耗。一般来说,数字技术具有更快的稳定时间和大范围的调整范围。然而,它们的频率范围非常有限,而且比模拟信号复杂。而模拟方法则具有较高的调整精度,但是调整范围较小[4-8]。

本文采用实时动态的高精度模拟域校准方式,所提出的高速高精度占空比调整电路具有包括压控产生电路、占空比调整电路和时钟信号合成电路。通过这些电路完成对时钟信号占空比的调整,环路设计简便且不需要补偿以及低通滤波。

1 占空比变化分析及校准技术

在高速ADC 工作中,希望控制各个模块电路工作的时钟信号是稳定的占空比为50%的时钟信号。但是时钟信号在传输过程中,经过各种逻辑器件后,时钟信号的上升沿和下降沿会产生不同程度的畸变,从而导致占空比偏离50%。除此以外,由于器件的失配、PVT 变化以及制造和工艺的偏差等也会使时钟信号占空比产生进一步的偏差,为了使ADC性能达到最优,时钟占空比校准电路的性能在这里将会起到至关重要的作用。

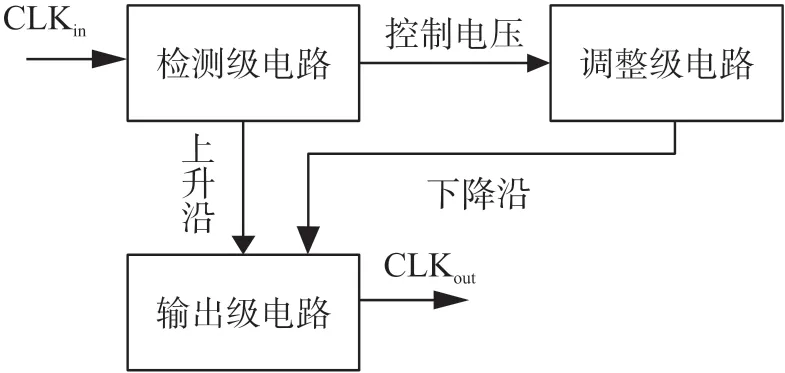

占空比校准技术分为带反馈的模拟校准方法和不带反馈的数字式校准方法。而无论那种校准方法,都有两个必不可少的模块:用于检测输入时钟信号信息并将之转换为控制电压的检测级电路以及根据控制电压转换为相应占空比调整量的调整级电路。其原理如图1 所示。

图1 占空比校准电路原理

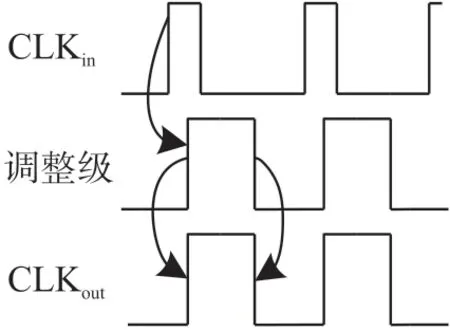

输入信号CLKin经过检测级电路后其上升沿触发输出级电路产生上升沿,输出控制电压至调整级电路,对占空比进行调整并产生下降沿至输出级电路,在输出级电路将上升沿和下降沿进行合成输出所需占空比的时钟信号。其校准时序图如图2所示。

图2 占空比校准时序

2 本文提出的占空比校正方法

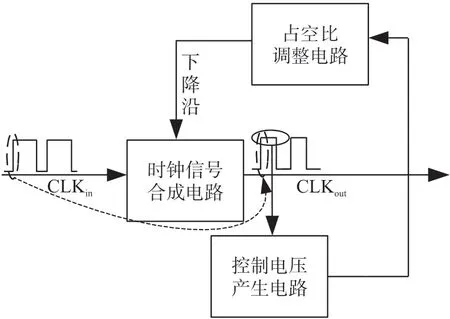

本文的占空比调整电路整体结构如图3 所示,采用环路负反馈的方式调节时钟信号的占空比。由时钟信号合成电路、控制电压产生电路、占空比调整电路组成。CLKin为输入时钟信号,CLKout为该电路最终调制后的输出时钟信号。

图3 电路整体架构原理图

外部输入进来的时钟信号CLKin首先输入到时钟信号合成电路,产生输出时钟的上升沿并通过锁存结构进行高电平保持,此时通过控制电压产生电路产生合适的电压信号促使占空比调整电路的电容进行放电,其放电速度与该控制电压相关,通过放电时间来调整输入时钟信号的脉冲宽度,并将信号反馈回时钟信号合成电路产生下降沿,从而完成输入信号的占空比调整。

2.1 基于环路负反馈的控制电压产生技术

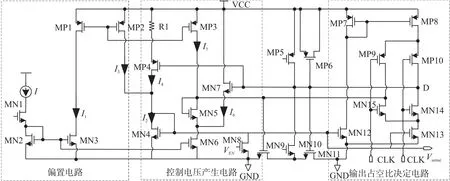

控制电压用于控制占空比调整电路尾电流源的电流大小,其输出精度影响最终占空比的输出精度。如图4 所示,为本文的控制电压产生电路,通过使用环路负反馈的方式来提高控制电压的精度,输出时钟信号CLK 以及输出时钟反向信号控制开关管的开关控制电容MP6、MN11 的充电与放电,当电路工作在稳定状态时,由于电流镜的作用,充放电速度一致,因此仅有充电时间等于放电时间,即输出时钟占空比等于50%。采用环路负反馈的方式通过调整调整管MP4 的过驱动电压来调整I4的电流大小进而不断调整控制电压的变化。

图4 控制电压产生电路

Vsense是电路产生的控制电压,用于控制图5 中电容C的放电速度。I是电路外部给的偏置电流,VEN作为电路的使能信号,为高电平时电路不工作,Vsense电压为低电平0 V;当VEN为低电平时电路正常工作,产生偏置电压Vsense。

棚室建造要少遮光:选择避风、向阳的地方建棚,坐北朝南,东西延伸。若有相邻棚,棚间距离应保持7~8m,应保持在冬至日上午9时左右,以不相互遮阴为宜。在保证棚室结构牢固,便于调控温、湿度的前提下,应适当降低棚室的高度。一般棚的高度越低,光照效果越好。要根据不同树种确定适宜的棚高,棚的高度以2.5m为底限。棚室的结构支柱要少,支柱不要太粗、太宽,应力求棚的拱杆遮光面窄,以利少遮光。适宜的大棚采光角可增加棚内光照,采光角度一般为24°~28°,后屋面的角度45°左右。

电路正常工作时,通过电流镜MN2~MN3 的电流复制I1=I,流过MP2 的电流为控制电压产生电路提供偏置,因此MP1 与MP2 的宽长比比例为k∶1,其中k比较大,因此电流镜MP1~MP2 产生的复制电流I3非常小,经过MP2、MP4、MN4 之间的电流关系如式(1)所示,则偏置电压Vsense的大小由I4决定,电流大小如式(2)所示。

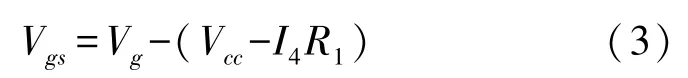

式中

在图4 中MP4 与MN7 的栅压相等,取决于流经MN7 的电流大小。电流镜MN2~MN6 的比例为1 ∶4,即流过MN6 的电流为4I。电流镜MP1~MP3的比例为1 ∶3,即流过MN6 的电流为3I,则流过MN7 的电流I6大小为I。因此其栅压与电流I的关系如式(4)所示:

2.2 延时可调的占空比调整技术

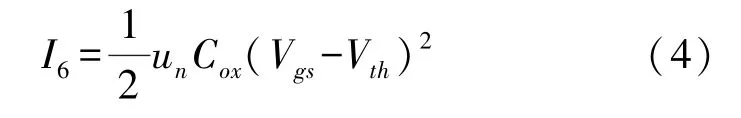

本文的占空比调整电路由两个反相器,一个电容组成。该调整电路通过控制电压调节反相器的尾电流源电流大小来实现调整反相器翻转时间,从而调整时钟信号下降沿的到来时间,实现占空比的调整。如图5 所示,放电速度由控制电压Vsense决定。

图5 占空比调整电路

通过控制电压Vsense的大小,来控制h点电压下降到反相器阈值电压的时间,再通过后级反相器,通过VA信号在时钟信号输出电路来调整输出时钟信号的下降沿时间,从而调整了时钟信号的脉冲宽度,由于MN2 不仅可以工作在饱和区,还可以工作在亚阈值区和线性区,只是相应的电流会改变,因此该电路可调的输入信号的占空比范围将变得非常大。

2.3 基于数字式的输出时钟信号合成

通过对输出时钟信号在调整级电路进行调整后,通过时钟信号合成电路合成得到最终所需要的输出信号。当输入时钟信号与输出时钟信号产生相位误差时,通过输出信号导通校准管MN,使X 点电压为低电平,从而使CLK 为高电平,并通过锁存结构对信号进行保持。当图6 中的VA为高电平时,MP10 导通,将X 点电位拉高,通过INV3 使CLK 信号置为低电平并进行保持。最终输出所需的时钟信CLK。

图6 时钟信号输出电路

3 验证结果与数据分析

本文的时钟校准电路基于0.18 μm 工艺下进行设计仿真,电源电压为3.7 V,仿真结果表明在输入100 MHz 占空比为6%与97%占空比时钟信号,可以看出,占空比校正电路将时钟信号校正为50%,且通过工艺角和温度仿真验证电路的占空比调整功能在各种环境下仿真都能保持稳定的占空比信号输出。

输入频率为100 MHz 的输入时钟下,产生占空比为50%的输出时钟,部分关键信号的输出结果如图7 所示,X2_Y 为图6 中M 处的输出结果,当为高电位时,通过锁存结构使输出时钟信号保持为高电位,并使h点电位开始放电,当放电至反相器阈值电压时A 点电位翻转,并将其反馈回时钟信号输出模块,产生输出时钟信号的下降沿,输出信号的上升沿和下降沿在信号输出模块通过锁存结构合成为输出时钟信号。

图7 时钟占空比调整过程的重要波形

为了验证电路的可靠性,在100 MHz 占空比20%输入时钟下,对电路在不同工艺角(tt,ss,ff)和温度下的输出时钟信号占空比进行仿真,其仿真数据如图8 所示,从图中可以看出输出时钟信号占空比稳定在50%,其误差小于0.28%。

图8 本文电路在不同工艺角、温度下的输出占空比

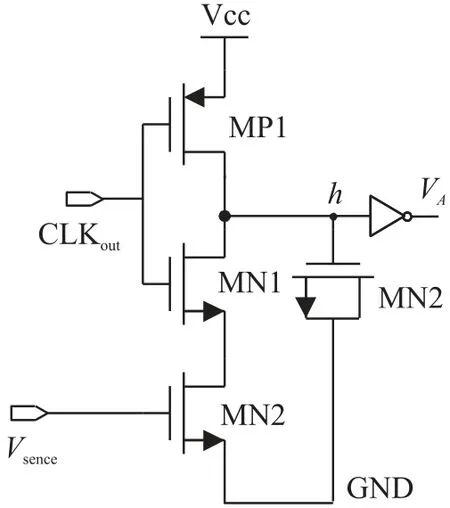

近年来,国内外对时钟信号的占空比校正电路有了深入的研究,本文与部分文献的参数对比如表1所示。可以看出本文所研究的时钟占空比校正电路有着较高的调整精度。

表1 本文电路与参考文献的参数性能对比

4 结论

本文研究了一种用于ADC 采样的高精度时钟占空比校正方法,基于0.18 μm CMOS 工艺设计了一种用于ADC 的高精度采样时钟信号占空比校准电路,通过采用环路负反馈的控制技术,提升控制电压的输出精度,并通过延时可控的调整电路对输入信号占空比进行校正并输出高精度的占空比信号,经仿真验证,输入占空比6%至97%的输入信号可以输出占空比稳定为50%的时钟信号,其输出误差小于0.28%。功耗和精度与现有文献相比,具有明显的优势。