一种基于65 纳米CMOS 工艺的77 GHz低噪声放大器设计

2021-11-04张书豪黄启俊

张书豪,何 进,李 硕,王 豪,常 胜,黄启俊

(武汉大学物理科学与技术学院,湖北 武汉 430072)

随着5G 技术的普及,信息的传输量和传输速度将再上一个台阶,这对通信系统提出了更高的要求。低噪声放大器(Low-Noise Amplifier,LNA)作为无线通信系统中构成射频接收模块的关键器件,在诸如雷达测距、卫星导航、电子对抗等领域被广泛应用[1]。

作为接收机的第一级电路,LNA 对接收到的信号进行放大,由于信号较为微弱,容易受到噪声干扰,因此LNA 需要能够抑制噪声,提高信噪比,进而提高接收机的灵敏度。近年来高性能低噪声放大器的研究在国内外取得了一定的进展,如Nawaz 等[2]采用0.13 μm SiGe BiCMOS 工艺研制了一种28/60 GHz 波段可调的LNA,分别具有16.2/15 dB 的增益和2.8/3.35 dB 的噪声系数;Li 等[3]基于22 nm CMOS 工艺设计了两款分别应用于E 波段和W 波段的LNA,其中E 波段LNA 具有20 dB 的增益和4.6 dB 的噪声系数;W波段LNA 则具有18.2 dB 的增益。近年来,LNA 的设计不断取得更低的噪声与更高的增益,这也是将来一段时间内低噪声放大器发展的方向。

本文使用65 nm CMOS 工艺设计了一种工作在77 GHz 附近的低噪声放大器,其采用四级放大器级联的方式构成,引入了反馈电感与补偿电感,对提高增益、减小噪声与回波损耗有一定的作用。仿真结果表明,本文提出的LNA 在增益与噪声系数方面有一定的优势,同时在线性度与稳定度方面也有良好的表现。

1 电路设计

1.1 电感源极负反馈技术分析

电感源极负反馈技术是LNA 设计中的一种常用的方法,采用这种技术设计的放大器往往具有较低的噪声系数和可观的功率增益。

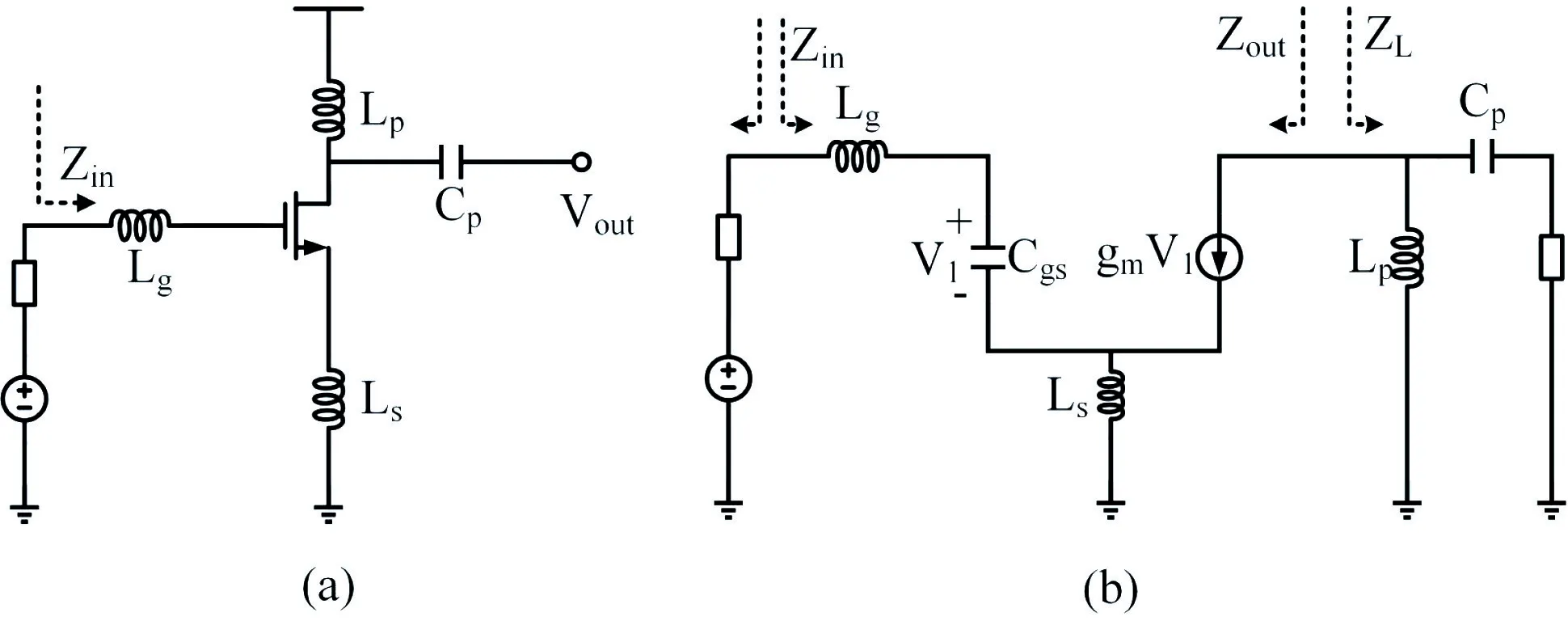

图1(a)给出了一种电感源极负反馈的基本结构,其中Ls是源极负反馈电感,Lg是栅极串联电感,由图1(b)的小信号模型可得电路的输入阻抗:

图1 (a)电感反馈共源极放大器模型;(b)小信号模型Fig.1 (a) Model of common-source amplifier with source feedback inductor;(b)Small-signal model

由上式可知,当Ls、Cgs、Lg产生谐振时,可以实现工作频段内较好的输入阻抗匹配。输入阻抗匹配时,谐振频率为[4]:

通过计算[5]可得在输入阻抗匹配时最小噪声系数:

可以看出,Lg的引入使电路在输入阻抗匹配时还获得较低的噪声系数,而引入Ls也在一定程度上缓和了阻抗匹配与噪声匹配的矛盾。为了使电路的性能达到最优,电感Ls则需要合理取值。因为电感Ls会在放大器的源极引入阻抗,如果Ls过大则会使增益降低,噪声系数增加;同时只有在Ls与栅、源极的寄生电容Cgs产生谐振时才会使回波损耗达到最低,功率匹配达到最优。

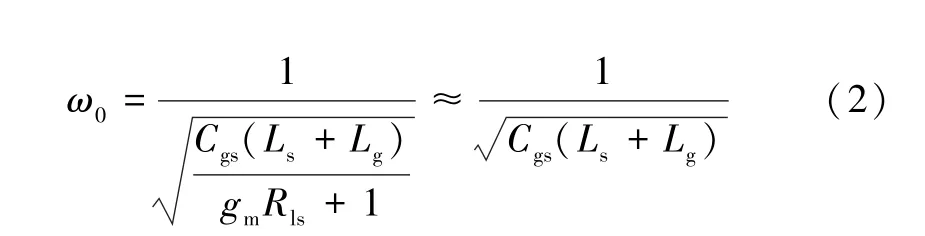

根据上述原理,本文LNA 中所用的带源极反馈电感的共源级放大器如图2 所示,其中L1和C1构成L 型匹配。在放大器源极引入的电感Ls与栅源寄生电容Cgs产生谐振,寄生电容的剩余部分则与Lg谐振,并与L 型匹配共同组成了输入端的阻抗匹配。综合增益、噪声、回波损耗等因素,最终确定Ls的值为17.5 pH。

图2 带源极反馈电感的共源极放大器Fig.2 Common source amplifier with source feedback inductor

1.2 电感补偿技术分析

本文采用四级放大器级联的方式设计LNA,其中后三级为带有补偿电感的共源共栅放大器,其电路图如图3(a)所示,为了便于计算,将晶体管寄生电容Cgd1、Cds1、Cgs2等效为C1、C2,便得到图3(b)所示的高频等效模型。

图3 (a)有补偿电感的共源共栅放大器原理图;(b)高频等效模型Fig.3 (a)Schematic of cascode amplifier with compensation inductor;(b)High-frequency equivalent model

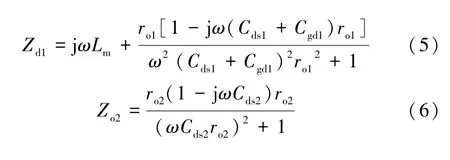

该电路的小信号模型如图4 所示,通过计算可以得到[6]:

图4 带补偿电感的共源共栅放大器小信号模型Fig.4 The small-signal model of cascode amplifier with compensation inductor

由式(4),(5),(6)可以看出,引入补偿电感Lm后,共源共栅放大器的输出阻抗随工作频率的上升而增加。输出阻抗的增加也使放大器的增益有明显提升,该放大器的增益可表述为:

经过计算与建模分析,最终确定第二级使用的补偿电感为30 pH,后两级的补偿电感为40 pH。

1.3 阻抗匹配设计

对于工作在高频段的低噪声放大器,无源器件对放大器的阻抗匹配有较大影响,因此要选择合适的阻抗匹配电路的结构,并对无源器件进行合理选择。因为本文采用四级放大器级联的方式设计电路,所以每级间都需要进行阻抗匹配。

共源级放大器隔离度通常较低,容易受到后级电路的阻抗干扰,因此本文在第一级和第二级之间采用T 型阻抗匹配,如图5(a)所示。其中C1是第一级放大器晶体管的漏极电容,C2是第二级放大器晶体管的栅极电容,C3是隔直电容,L1是漏极电感。L1、L2、C3组成T 型匹配网络,这种结构相较于传统的LC 谐振网络有更大的带宽、更高的隔离度,L1还可以降低后级信号的干扰。

本文的低噪声放大器二、三级与三、四级之间均采用相同的L 型阻抗匹配,如图5(b)所示。其中L3是漏极电感,C6是隔直电容,C4是前一级的漏极电容,C5是后一级的栅极电容。L3与C6构成LC 谐振网络,实现L 型阻抗匹配。

图5(c)所示的则是低噪声放大器的输出阻抗匹配,采用T 型阻抗匹配结构,其中C7是第四级的漏极电容。L4和C7组成低通滤波器,L4、L5、L6组成T 型阻抗匹配网络,L5和C8组成带通滤波器,共同实现了50 Ω 阻抗匹配。电路中所使用的电感均单独进行建模并仿真优化,最终确定L4=35 pH,L5=L6=40 pH,C8=180 fF。

图5 阻抗匹配电路Fig.5 Impedance matching circuit

1.4 整体设计

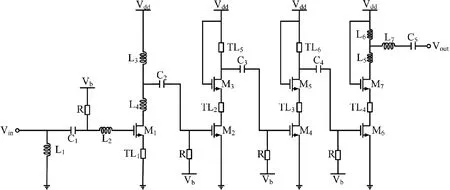

综合上文各个模块的设计方案,本文的LNA 电路图由图6 给出。第一级放大器采用共源极结构,并带有源极负反馈传输线,该传输线可以优化噪声系数,改善输入阻抗匹配;后三级放大器采用共源共栅结构,并带有级间补偿传输线,以提高增益并降低噪声系数。电路中C1~C5负责交流耦合与阻抗匹配,TL1是源极反馈传输线,TL2~TL4是级间补偿传输线,有提高增益的作用。

图6 低噪声放大器电路结构Fig.6 Low-noise amplifier circuit structure

经过仿真与优化,最终确定的晶体管尺寸为M1:22 μm;M2、M3、M4、M5:39 μm;M6、M7:42 μm,偏置电压Vb=600 mV,Vdd=1.2 V。

2 版图与后仿真结果

2.1 无源结构三维模型

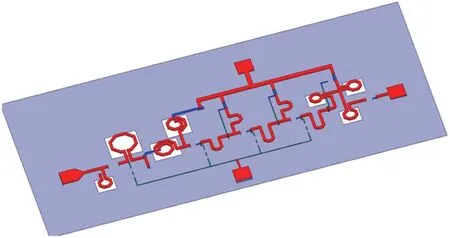

为了得到更为精确的电路性能,采用全波三维电磁高频结构仿真器对电路的无源元件(包括变压器、电容、传输线、金属连线和过孔等)构成的三维结构进行了整体电磁仿真和优化,如图7 所示。

图7 LNA 三维模型Fig.7 Three-dimensions model of LNA

将所生成的无源多端口S参数文件与晶圆厂提供的PDK 中的有源器件进行联合仿真,就可以得到后仿真电路原理图,从而获得整体LNA 设计的最终性能。

2.2 版图设计

本文采用65 nm CMOS 工艺设计版图。在符合设计规则[7]的前提下,为了确保信号路径的通畅,尽可能地降低回波损耗,设计中将所有的有源器件按一个方向排放;为了提高信号传输效率,减少金属线的传输损耗,设计时用顶层与次顶层金属实现信号线与电感等无源器件;为了减少电源噪声的干扰,所有直流电源都进行了大电容去耦合处理。图8 为本文77 GHz LNA 的版图,整个芯片版图尺寸(包括变压器、电容、传输线、金属连线和所有测试焊盘)为400 μm×860 μm,其中G-S-G 焊盘的中心间距为150 μm。

图8 77 GHz LNA 版图Fig.8 Layout of 77 GHz LNA

2.3 后仿真结果

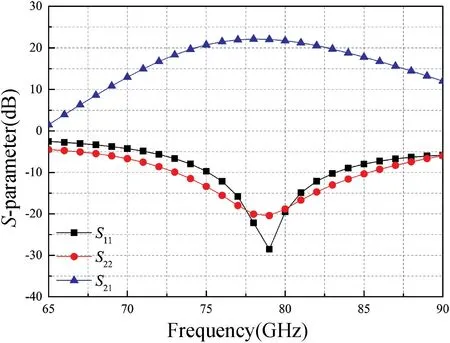

S参数仿真曲线如图9 所示,从S参数仿真结果可以看出LNA 的增益和反射情况。中心频点为79 GHz,在此处最大增益S21为22 dB,-3 dB 带宽为73.5~83.5 GHz;中心频点处输入回波损耗S11为-28.5 dB,输出回波损耗S22为-20.5 dB。而在-10 dB带宽73~85.5 GHz 的范围内S22小于-10 dB,说明LNA 输出阻抗与50 Ω 负载在较宽的频带内匹配良好,输出端的T 型阻抗匹配有效扩展了带宽。

图9 LNA 的S 参数仿真曲线Fig.9 S-parameter simulation of LNA

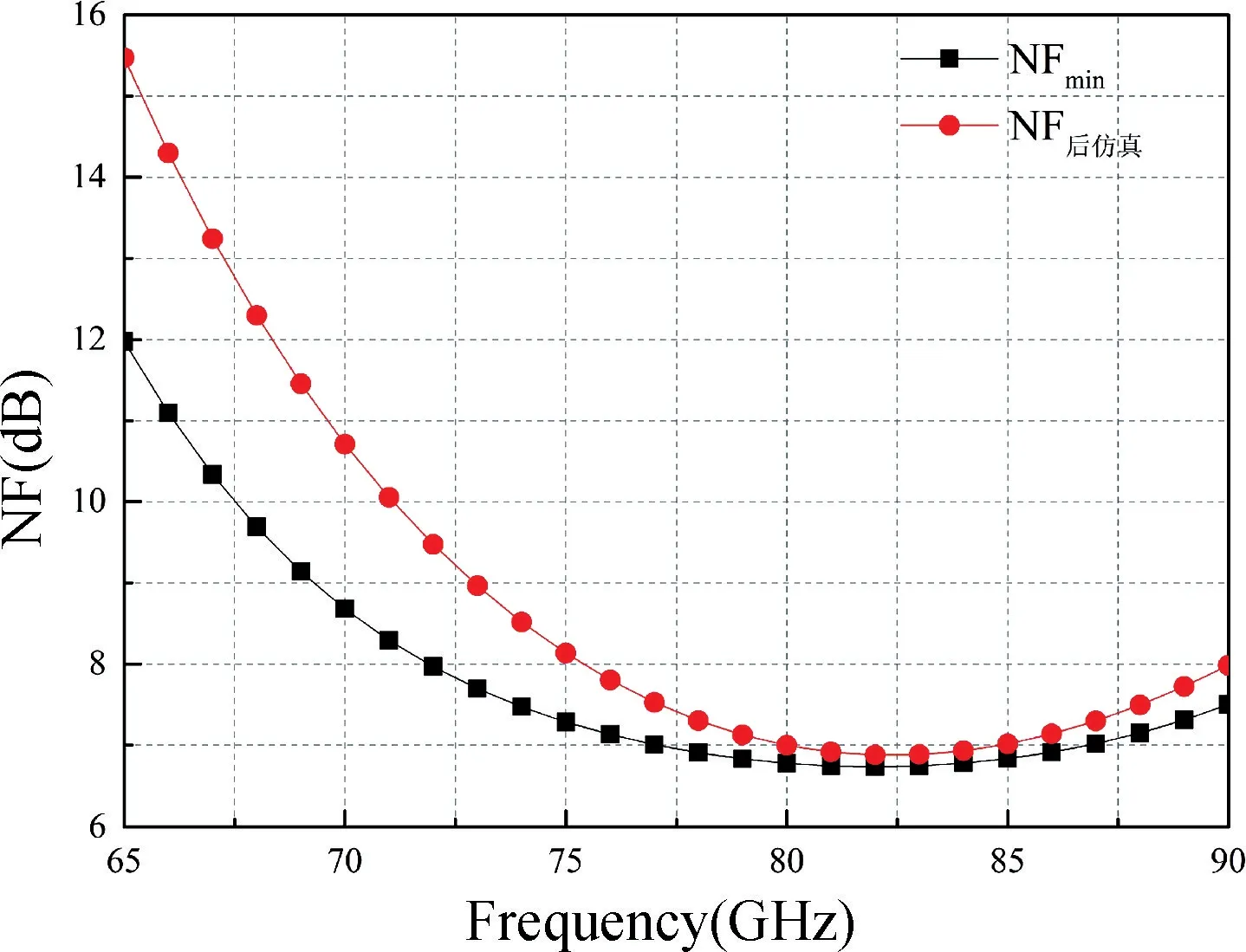

图10 给出了LNA 的噪声系数(NF)仿真结果,在79 GHz 处NF=7.1 dB。而在75~90 GHz 的范围内噪声系数小于8 dB,同时与最小噪声的对比显示,两者差别很小,说明输入噪声匹配较好。

图10 LNA 噪声系数仿真Fig.10 Noise figure simulation of LNA

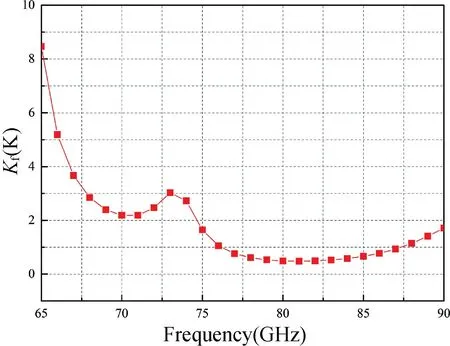

图11 给出了LNA 线性度的曲线。在中心频率处输入1 dB 压缩点为-23 dB,线性度满足应用要求。图12 为稳定因子的曲线,结果显示在65~90 GHz 范围内放大器十分稳定。本文的LNA 与其他参考文献的对比由表1 给出。

表1 本文LNA 与部分参考文献的对比Tab.1 Comparison of this LNA and other thesises

图11 LNA 线性度仿真Fig.11 Linearity simulation of LNA

图12 LNA 稳定因子仿真Fig.12 Stability factor simulation of LNA

3 结论

本文基于65 nm CMOS 工艺设计了一种77 GHz低噪声放大器。LNA 采用四级放大器级联的方式设计,引入了电感源极负反馈技术和电感补偿技术,并通过对器件尺寸的合理选择与无源器件的建模分析,使电路取得了较低的噪声与较高的增益。经过仿真验证,LNA 在1.2 V 电源电压下,功耗为41 mW,在中心频点处的增益为22 dB,噪声系数为7.1 dB,可满足应用需求。输入/输出回波损耗均小于-10 dB,说明电路的输入/输出阻抗匹配良好。同时电路拥有良好的线性度与稳定因子,证明LNA 可以稳定工作。本文的LNA 在E 波段射频接收机中有一定的应用前景。