一种新型带宽自动校准有源低通滤波器*

2021-11-02李航标

李航标

(中国西南电子技术研究所,成都 610036)

0 引 言

基于互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺的接收机由于成本低、集成度高,广泛应用于无线通信和导航系统中[1-5]。作为接收机重要组成部分,有源低通滤波器用于抑制不期望通过的信号和噪声[6-8]。有源低通滤波器的带宽主要由组成滤波器的电容和电阻决定。

文献[9]在0.18 μm CMOS工艺下,通过改变输出缓冲器电流调节滤波器特性,由于不需要大的电容阵列,减小了芯片面积,在0.13 mm2硅上实现了一款在0.3~1 MHz频率范围内可调的有源RC低通滤波器。该滤波器功耗低、面积小。文献[10]在0.13 μm CMOS工艺下实现了一款带宽在0.4~20 MHz范围可调、面向多模应用的有源RC滤波器,滤波器电阻、电容可数字控制。

随着集成电路工艺线宽不断减小, 工艺、电压、温度(Process,Voltage,Temperature,PVT)波动及芯片老化对有源滤波器带宽(或截止频率)影响越来越大[11]。以上两款有源滤波器都没有给出芯片出现PVT波动或老化时,如何应对滤波器带宽受到的影响。为了解决芯片PVT波动及老化对滤波器带宽的影响,文献[12]在0.18 μm标准工艺下,实现了一款用于ZigBee的有源RC滤波器。该滤波器使用极点级级联实现3 MHz带宽。为减小PVT波动及老化对滤波器带宽的影响,使用主-从校准策略调节滤波器带宽。从滤波器是主滤波器的复制,通过观测并调节从滤波器的频率响应,得到期望带宽的滤波器电容,并应用于主滤波器。文献[13]基于0.35 μm SiGe 双极互补金属氧化物半导体(Bipolar Complementary Metal Oxide Semiconductor,BiCMOS)工艺使用锁相环和滤波器主-从校准策略设计了一款带宽可自动调节的多模滤波器,可实现优于4%的带宽校准精度。文献[14]基于0.18 μm CMOS工艺使用主-从校准策略设计了一款用于全球导航卫星系统(Global Navigation Satellite System,GNSS)的可自动校准有源RC滤波器,可以实现5%的带宽校准精度。文献[15]使用主-从校准策略调节滤波器带宽,使用片外数字电路和软件配合片上电路检测主滤波器的时间常数变化,进行带宽校准,滤波器带宽校准精度可以达到3.4%。文献[12-16]中,滤波器校准使用主-从校准策略均存在两个弊端:第一,在主滤波器和从滤波器电路之间存在PVT和电路偏差,将主/从滤波器的校准结果使用于从/主滤波器是存在误差的;第二,CMOS工艺下,为了校准一个滤波器,在硅上多设计一个额外的类似的滤波器,必然占用更多的芯片面积。

为了解决以上问题,本文提出一种新型带宽自动校准有源低通滤波器,通过时域采样有源低通滤波器对输入的响应,并与参考电压进行比较,算法电路根据比较结果调整滤波器电容大小,自动搜索到最佳的滤波器带宽。采用直接对目标滤波器带宽进行校准,不但可以消除芯片PVT波动及老化对滤波器带宽的影响,而且可以克服主-从校准策略中引入的带宽误差,达到更高的校准精度;同时节约芯片面积,使用方便、灵活。

1 新型有源低通滤波器带宽校准原理

图1所示的电流输入电压输出有源低通滤波器,当在0时刻滤波器差分输入端正端施加一个电流脉冲+Iin、负端施加一个电流脉冲-Iin时,滤波器输出电压

VO=-Rf·2Iin(1-2·e-t/(Rf·Cf)) 。

(1)

式中:Rf和Cf是滤波器的电阻和电容,t表示时间。电阻RP1、RM1阻值均为Rf,电容CP1和CM1容值均为Cf。

图1 电流输入电压输出有源低通滤波器

用Δt表示从滤波器输入端施加电流脉冲开始到VO变成0之间的时间差,令VO= 0,则有

Rf·2Iin(1-2·e-Δt/(Rf·Cf))=0 ,

(2)

从而得到

Δt=Rf·Cfln 2=ln 2/(2π·f-3 dB) 。

(3)

由公式(2)和(3)可知,在t=Δt采样滤波器输出电压并且和0比较即可判断该时刻滤波器带宽大于期望值还是小于期望值。利用该原理可以进行滤波器的带宽校准。

由于电路响应延迟,Δt会存在偏差Δτ,从而造成校准偏差。为消除Δτ对校准精度的影响,可以采用两次校准,通过运算得到最终校准结果。

第一次校准,Δt=TCK,滤波器差分输入端正端施加一个电流脉冲+Iin,负端施加一个电流脉冲-Iin,有

TCK+Δτ=Rf·Cf1ln 2=ln 2/(2π·f-3 dB,1) 。

(4)

式中:Cf1表示第一次校准得到的滤波器电容,f-3 dB,1表示第一次校准得到的滤波器带宽。

第二次校准,Δt=2·TCK,滤波器差分输入端正端施加一个电流脉冲+0.5Iin,负端施加一个电流脉冲-1.5Iin,有

2·TCK+Δτ=2Rf·Cf2ln 2=2ln 2/(2π·f-3 dB,2)。

(5)

式中:Cf2表示第二次校准得到的滤波器电容,f-3 dB,2表示第二次校准得到的滤波器带宽。将公式(5)和公式(4)做减法运算有

TCK=Rf(2Cf2-Cf1)ln 2=ln 2/(2πf-3 dB,F)。

(6)

式中:f-3 dB,F表示经过两次校准得到的不受芯片PVT波动、老化及电路延迟影响的最终滤波器带宽。对应的有源滤波器电容为

CF=2·Cf2-Cf1。

(7)

本文基于以上校准原理,设计了一款新型的带宽自动校准有源低通滤波器。

2 新型带宽自动校准有源低通滤波器

2.1 总体设计

本文的新型带宽自动校准有源低通滤波器主要由可调带宽有源低通滤波器、采样保持电路、电荷释放电路、电压比较器、数字算法电路、时序控制电路和电流脉冲产生电路构成,如图2所示。

图2 新型带宽自动校准有源低通滤波器框图

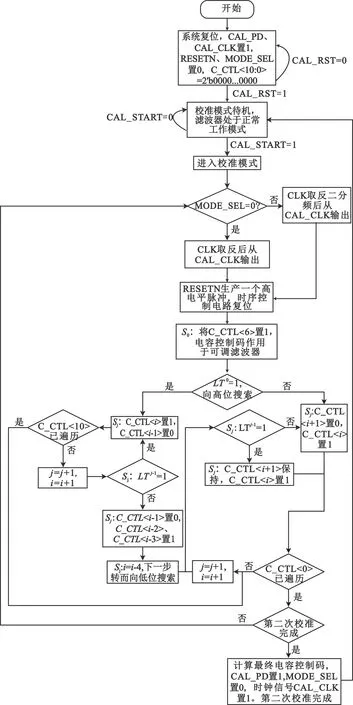

滤波器校准过程包含第一次校准和第二次校准。采用11位电容控制码C_CTL<10:0>,每次校准包含X+1个校准步,分别用S0,S1,S2,S3,…,SX表示。校准带宽不同,每次校准步X也可能不同,以确保滤波器的每一位电容控制码均遍历到,且找到和期望带宽对应的最佳滤波器电容值。时钟信号CLK的周期为TCK,频率为fCK,和滤波器期望带宽f-3 dB,F满足fCK=(2π·f-3 dB,F) / ln 2。

在每次校准的过程中,电流脉冲产生电路根据输入控制信号CTL2和MODE_SEL产生两种不同大小的恒定电流脉冲输出到滤波器差分输入端。

在信号CTL1作用下,采样保持电路在每个校准步采样滤波器的输出电压并提供给电压比较器。电压比较器将采样信号与0比较。VNP和VNM分别表示采样保持电路对VOP和VOM的采样电压。VNP>VNM时,滤波器输出电压VO> 0,电压比器输出为高电平;VNP 数字算法电路根据输入信号LT,在时钟CLK控制下,在两次校准过程中遍历电容控制码的每一位,分别搜索得到一个最优的电容控制码NC1、NC2;在校准结束时,运算得到最终的电容控制码NF=2·NC2-NC1。数字算法电路输出信号ST用于关断前级电路,避免校准过程受到前级电路输入信号的干扰;提供MODE_SEL信号,和CTL2信号一起改变电流脉冲产生电路输出电流脉冲的大小;提供复位信号RESETN和使能CAL_PD,通过或非门G0决定时序控制电路复位;提供信号CAL_PD使能电流脉冲产生电路;在两次校准过程中的每个校准步,将产生的电容控制码C_CTL<10:0>输出到滤波器。 时序控制电路在输入复位信号RST和时钟信号CAL_CLK控制下产生三个不同的信号,对整个校准过程时序进行控制。电荷释放电路在信号CTL3控制下,释放采样保持电路电容存储的电荷。 信号RESETN和CTL_PD经过或非门G0运算后可以对时序控制电路进行复位,从而复位整个校准过程。当RST=0时,在信号CAL_CLK上升沿,时序控制电路输出同步复位,信号CTL1、CTL2、CTL3都置0;当RST=1时,时序控制电路的输出在时钟CAL_CLK控制下产生同频率、同占空比、不同相位的三个时钟信号CTL1、CTL2、CTL3,其中,CTL2比CTL1滞后1个CAL_CLK周期,CTL3比CTL1滞后4个CAL_CLK周期,如图3所示。 图3 时序控制电路信号时序 如图4所示,电流脉冲产生电路中,反相器G1~G6和二输入与非门G7~G10组成控制逻辑;NMOS管M1、M2、M3、M4组成1∶1∶1∶2电流镜,PMOS管M5、M6、M7组成1∶1∶2的电流镜;NMOS管M12~M15作为压控开关,栅极高电平时导通,栅极低电平时截止;PMOS管M8~M11作为压控开关,栅极低电平时导通,栅极高电平时截止。在第一次校准时,MODE_SEL=0;第二次校准时,MODE_SEL=1;校准过程开始后,CAL_PD=0;校准过程开始前和结束后,CAL_PD=1。当CAL_PD=1时,BN=PUP=AN1=AP2=1,B=PDN=AN2=AP1=0,MOS开关M8 ~ M15全部截止,没有电流流入或流出节点VP、VM。 (a)数字逻辑电路 (b)充放电电路图4 电流脉冲产生电路 在第一次校准时,CAL_PD = 0,MODE_SEL = 0。当CTL2 = 1时,AN1 = AN2 = B = PDN = 0,AP1 = AP2 = BN = PUP = 1,M10和M15导通,M8、M9、M11、M12、M13、M14截止,电流2·I1经路径1对节点VP充电,电流2·I1经路径2对节点VM放电。当CTL2=0时,AP1=AP2=B=PDN=0,AN1=AN2=BN=PUP=1,M11和M14导通,M8、M9、M10、M12、M13、M15截止,电流2·I1经路径1’对节点VP放电,电流2·I1经路径2’对节点VM充电。 在第二次校准时,CAL_PD = 0,MODE_SEL = 1。当CTL2 = 1时,AN1 = AN2 = BN = PDN = 0,AP1 = AP2 = B = PUP = 1,M9、M10、M12、M15导通,M8、M11、M13、M14截止,电流2·I1经路径1对节点VP充电,电流I1经路径3对节点VP放电,两电流在节点VP叠加,结果大小为2·I1-I1=I1的电流对节点VP充电;同时,电流2·I1经路径2对节点VM放电,电流I1经路径4对节点VM充电,两电流在节点VM叠加,结果大小为2·I1-I1=I1的电流对节点VM放电。当CTL2=0时,AP1=AP2=BN=PDN=0,AN1=AN2=B=PUP=1,M9、M11、M12、M14导通,M8、M10、M13、M15截止,电流I1经路径3,电流2·I1经路径1′,在节点VP叠加,电流I1+2·I1=3·I1对节点VP放电;电流2·I1经路径2′,电流I1经路径4,对节点VM充电,结果大小为3·I1的电流对节点VM充电。 电荷释放电路在信号CTL3控制下,释放采样保持电路电容电荷。如图5所示,NMOS管M8、M9组成1∶4电流镜,PMOS管M10和M11组成1∶5电流镜,RH和RL为两个电阻。开关K1和K2截止时,恒定电流20·I2流过M11、RH、RL到地,节点VOH和VOL的电压由电流I2和电阻RH、RL决定。CTL3=1时,K1和K2导通,电荷释放电路通过路径5对节点NM充电,节点NM电压升高;节点NP通过路径6放电,节点NP电压降低。信号CTL3=0时,开关K1和K2截止。经过充放电后,在节点VOH和VOL之间保持一定的电压差。偏置电流I1=I2=50 μA。 图5 电荷释放电路 滤波器可调电容CM1和CP1结构相同,如图6所示。KP0,KP1,KP2,KP3,…,KP10和KQ1,KQ2,KQ3,…,KQ10都是压控开关,高电平控制导通,低电平控制截止。GP0,GP1,GP2,…,GP10是反相器。KPi导通时,KQi截止;KPi截止时,KQi导通,i=0,1,2,…,10。CD是固定容值电容。电容C0,C1,C2,C3,…,C10根据开关的导通(或截止)接入(或不接入)滤波器。其中,C1= 2C0,C2=22C0,C3=23C0,…,C5=25C0,C6=25C0,C7=26C0,…,C10=29C0,C0的大小决定了滤波器带宽校准的精度。滤波器带宽 f-3dB=1/(2πRfCf) 。 (8) 式中:Rf为RP1、RM1的阻值,均为2.2 kΩ;Cf为电容CP1、CM1的容值, (9) 当CD=0.48 pF,C0=0.01 pF,控制码C_CTL<10:0>所有位为1时,滤波器最大电容为11 pF;当控制码C_CTL< 10:0 >所有位为0时,滤波器最小电容为CD。 图6 滤波器可调电容 电路启动后,系统复位到初始状态。此后,如果信号CAL_RST保持为0,则系统一直保持初始状态不变。当CAL_RST从0变成1,系统复位释放,进入校准模式待机状态。此后,当信号CAL_START由0变成1,系统进入校准模式。校准模式开始时,信号MODE_SEL=0,系统先进行第一次校准。CLK信号取反后由CAL_CLK输出提供给时序控制电路,然后信号RESETN产生一个高电平脉冲,时序电路复位。电容控制码总共11位,算法从中间的6位开始,先向高位逐位搜索,再向低位搜索,直到控制码最低位C_CTL<0>被遍历到。算法流程如图7所示。其中,用LTj-1表示在Sj步,Sj-1步最后一次CTL3=1时,D触发器锁存的比较器的输出结果CMPOUT信号。 图7 算法流程图 第一次校准结束,得到滤波器电容控制码NC1。然后进行第二次校准,信号MODE_SEL置1,信号CLK取反二分频后从CAL_CLK输出给时序控制电路。信号RESETN产生一个高电平脉冲复位时序控制电路,然后执行第二次校准。第二次校准与第一次类似,第二次校准使用的时钟信号CAL_CLK的占空比不变,但时钟周期是第一次的两倍。第二次校准结束后,得到滤波器电容控制码NC2,最终对芯片PVT波动、老化及电路延迟均不敏感的滤波器电容控制码为NF=2·NC2-NC1。信号CAL_PD置1,MODE_SEL置0,时钟信号CAL_CLK置1,算法再次进入校准模式待机状态。 本文新型带宽自动校准有源低通滤波器在65 nm CMOS工艺进行设计和实现。其中,可调有源滤波器、时序控制电路、采样保持电路等大小为860 μm ×790 μm,如图8中A所示;数字算法电路大小为80 μm×80 μm,如图8中B所示。 图8 带宽自动校准有源低通滤波器版图 图9给出了典型情况(tt工艺角,1.2 V电源电压,27 ℃)下滤波器40 MHz带宽校准时算法执行过程的仿真波形图。滤波器电容用11位数字码控制。根据fCK=(2π·f-3 dB,F)/ln 2,输入时钟信号CLK频率为362.6 MHz。从图中可以看出,系统复位后,电容控制码初始值为2′b 010_1100_0011。1.5 μs时,信号CAL_START由低电平拉高,带宽校准启动;在4.5 μs时,第一次带宽校准结束,得到电容控制码NC1= 2′b 000_1100_1101;在7 μs时,第二次带宽校准结束,得到电容控码NC2= 2′b 000_1100_1111;7.5 μs时,整个校准结束,得到电容控制码NF=2′b 000_1101_0001,满足NF=2·NC2-NC1。 图9 40 MHz带宽校准算法搜索过程 40 MHz带宽校准完成后,对滤波器在典型情况下进行交流仿真,得到其-3 dB带宽为39.739 MHz,如图10所示。滤波器电阻Rf=2.2 kΩ,滤波器低频增益约为67 dB。 图10 校准后40 MHz带宽 期望带宽40 MHz,根据公式(8)和(9)可以计算出在控制码NF=2′b 000_1101_0001下滤波器的理论带宽为44.933 MHz,自动校准得到带宽为39.739 MHz。电路本身存在寄生效应,造成滤波器实际电容大于理论计算数值,从而使得理论计算带宽大于自动校准得到的带宽,但自动校准得到的带宽更接近期望带宽。由公式(8)可以计算出,期望带宽对应的期望滤波器电容为1 809 fF,自动校准带宽对应的滤波器电容为1 820 fF,两者相差约11 fF,略大于滤波器使用的最小电容10 fF,其偏差由电路的寄生效应和仿真误差引起。 表1给出了典型情况下在8~50 MHz期望带宽范围内,滤波器校准输入时钟信号CLK频率、校准后的带宽及误差,可以看出在8 MHz、20 MHz和30 MHz校准误差只有0.4%,在40 MHz和50 MHz带宽校准误差略有升高,但滤波器带宽校准误差总体不大于0.7%。 表1 滤波器带宽校准误差 本文提出了一种新型带宽自动校准有源低通滤波器。通过时域采样滤波器对于输入电流脉冲的响应,并将采样电压与参考电压进行比较,算法电路根据比较结果调整滤波器电容大小,直到搜索到最佳的滤波器带宽。在算法电路控制下进行两次校准,最终可以得到对PVT波动、芯片老化和电路响应延迟不敏感的精确的滤波器带宽。在65 nm CMOS工艺下设计了一款带宽自动校准有源低通滤波器,仿真结果显示,该有源低通滤波器可以自动校准,自适应地搜索到最佳的滤波器带宽,校准精度较高。该自动校准有源低通滤波器电路设计通用化,具有良好的工程实用性。在上位机控制下随时可以对滤波器带宽进行校准,滤波器使用灵活,应用范围广泛。2.2 时序控制电路

2.3 电流脉冲产生电路

2.4 电荷释放电路

2.5 滤波器可调电容

2.6 搜索算法

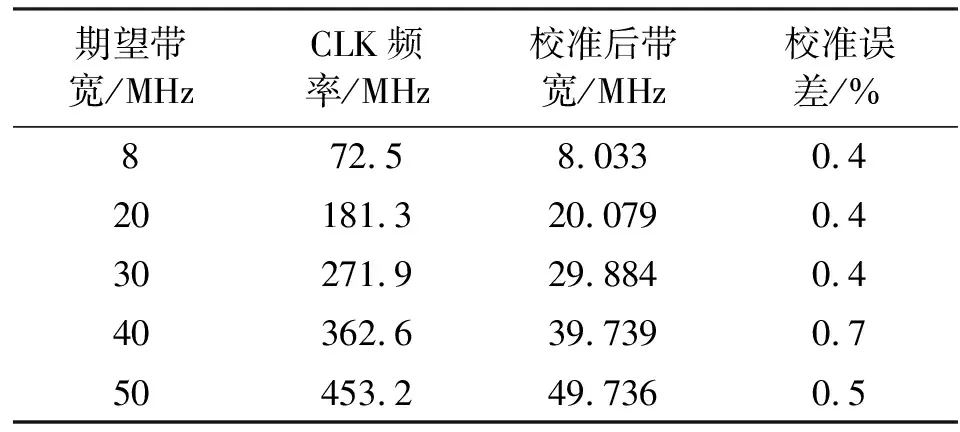

3 实验结果与分析

4 结 论