某视频处理终端骚扰功率整改

2021-11-01张露华

张露华

(福建省产品质量检验研究院,福建 福州 350002)

电磁兼容(Electromagnetic Compatibility,EMC)是一门新兴的综合性学科,是使电气装置或系统在共同的电磁环境条件下,既不受电磁环境的影响,也不会干扰环境[1]。电磁兼容的三要素是骚扰源、耦合途径和敏感设备。PCB板上安装的时钟信号是一种引起PCB板电磁兼容问题的常见且重要的辐射源,良好的时钟电路设计是PCB板的电磁兼容设计的关键。文章从一个视频处理终端骚扰功率频点超标案例出发,对如何降低时钟(骚扰源)的干扰进行分析,提出解决方案并进行验证该方案的有效性。

1 骚扰功率测试原理和方法

标准GB13837规定,对于有关设备不测量骚扰场强而是测量其骚扰功率,因此骚扰功率测试是绝大多数AV类产品(收音机和电视机除外)产品在认证时的EMC测试项目之一[2]。

通常环境下,当频率超过30 MHz时,设备所产生的骚扰能量通过辐射传播到被骚扰的接收机,结果表明,大部分能量是由靠近设备的电源线及其他连线向外辐射的。因此,可用被测设备电源线和其他连线上的骚扰功率来定义其骚扰电平,这一功率近似等于由套在这些连线上的合适的吸收钳在吸收功率最大位置上的测量值。

被测设备置于高度为0.8 m的非金属台上,距其他金属物体或人体至少0.8 m,被测馈线应在台子上平直展开,其长度要足够放置吸收钳和必要时调整吸收钳的位置以获取最大辐射值。将吸收钳套在被测馈线上,其电流变换器一端应朝向被测设备,以便测量馈线上的骚扰功率。骚扰功率的测量原理图如图1所示。

图1 骚扰功率的测量原理

测试时,干扰信号的传输路径为:首先吸收钳将捕获的干扰转换成电流形式,再通过同轴线缆传输到测量接收机,然后依次用吸收钳测量长度超过25 cm的屏蔽或非屏蔽连接线,这些连接线是连接至被测设备的各自独立单元上,最后滑动吸收钳,依次寻找每条线缆上吸收功率最大的位置,该位置的读数即为这条线缆的最大骚扰电平。

2 视频处理终端端骚扰功率超标问题

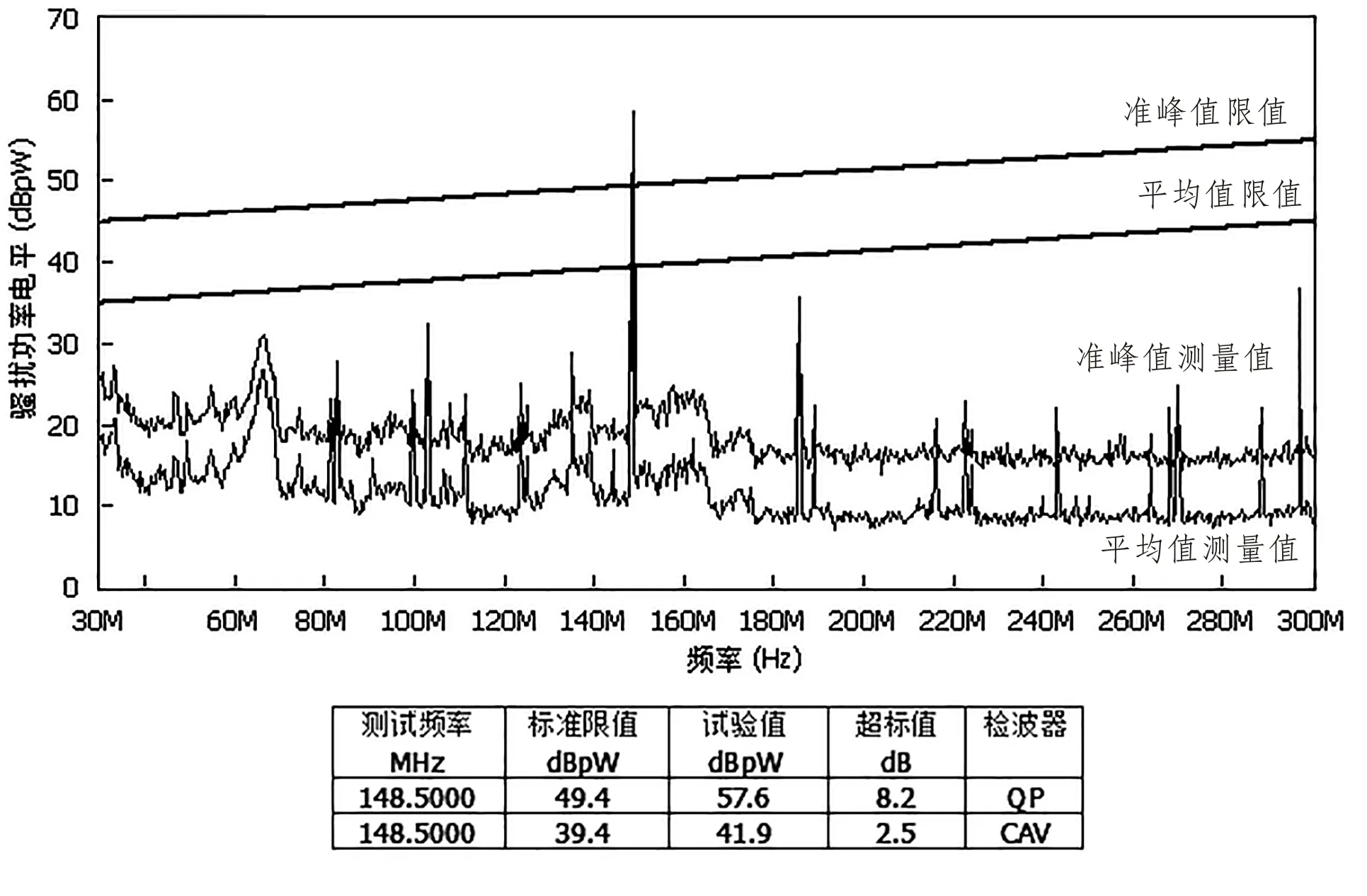

对某视频处理终端按照GB/T 13837-2012标准要求,播放标准垂直彩条信号。其电源端口和HDMI端口的骚扰功率测试图形和超标频点测试值分别如图2(a)和图2(b)所示,上下两根曲线分别代表准峰值和平均值的限值。从测试结果看148.5 MHz频点测试不合格,且该频点从图形上看是属于“单根刺”形状的窄带波形,可能是时钟频率干扰导致。

图2(a) 电源端口骚扰功率测试结果

3 分析整改

对机内主板上的各时钟信号进行分析,发现机内一块转接板上有用到一颗148.5 MHz的有源晶振,如图3所示。

图3 内机主板

首先考虑改善整机及I/O接口外壳接地,用万用表测量整个机壳的接地情况,采用锉刀将机壳外层绝缘漆刮除,并用导电胶布保证各部分机壳间的良好搭接,用导电泡棉良好连接各I/O接口外壳与金属外壳。重新进行测试,测试曲线没有下降,该整改方式无效。

接下来对该148.5 MHz有源晶振的电路原理图进行分析:靠近晶振的电源引脚设计了两个去耦电容,容值分别为1 u跟0.01 u。晶振的时钟输出端跟CPU之间串联一个220 Ω的匹配电阻。

有源晶振的典型电路原理图如图4所示。

图4 有源晶振的典型电路原理

(1)电源通过一个磁珠后接入晶振引脚,这样可以降低电源噪声对时钟输出频率的影响。晶振电源的去耦电容一般选3个,电容值之间最好相差一个数量级(如1 uF、0.1 uF、0.01 uF并联),这样可以过滤更宽频率范围内的电源噪声。

(2)输出端串联一个小电阻R1,主要有两个作用:一是进行阻抗匹配,减小回波干扰及导致的信号过冲。阻抗不匹配的时候会产生信号反射,有源晶体的输出阻抗通常都很低,而信号源的输入端在芯片内部结构上通常是运放的输入端,这个运放的输出阻抗都在兆欧以上。二是减少谐波,有源晶体输出的是方波,在阻抗严重不匹配的情况下,会更容易引起谐波干扰。加入电阻R1与输入电容构成RC积分平滑电路,将方波转换为近似正弦波,虽然信号的完整性受到影响,但由于该信号还要经过后级放大、整形后才作为时钟信号,所以可以在保证性能的基础上减少谐波干扰。因此R1的大小需要根据输入端的阻抗、输入等效电容,有源晶体的输出阻抗等因素选择。有时,不同批次的板子特性不一样,需要在实际测试过程中调整确定以达到最佳状态。

(3)输出电阻R1后端一般还会预留设计电容C4,C4与串联电阻R1组成RC滤波电路,减少时钟信号的过冲,C4值可根据实验情况进行调整。通过对有源晶振的典型电路图分析,尝试对转接板上晶振电路进行调整,先是在电源端增加一个容值为0.1 uF去耦电容,测试曲线有所下降但仍不符合要求;接着调整时钟线上串联电阻的阻值,发现加大或减小该电阻阻值时,电源端口超标频点的测试值会有明显变化,不断修改该电阻阻值,反复测试,发现当串联电阻值为100 Ω时,改善最明显,测试结果符合要求且还有约3 dB的余量。因余量不是很大,继续增加整改措施验证,在匹配电阻后端增加一个滤波电容,不断调整容值,当电容容量为470 pF时,测试余量达到5 dB以上。

4 测试结果分析

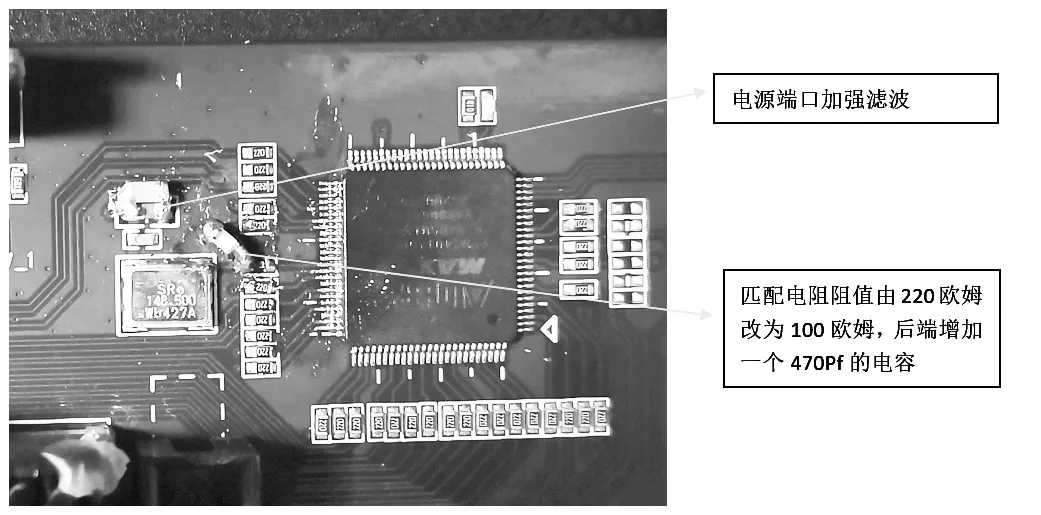

对转接板上晶振电路进行如下处理:(1)调整时钟信号线上匹配电阻阻值,由阻值220 Ω调整为100 Ω;(2)输出线上匹配电阻后端增加电容滤波,组成RC匹配滤波电路,电容容量为470 pF;(3)晶振电源处增加一个容值为0.1 uF去耦电容。

按照以上措施对主板整改如图5所示。

图5 整改后的机内主板

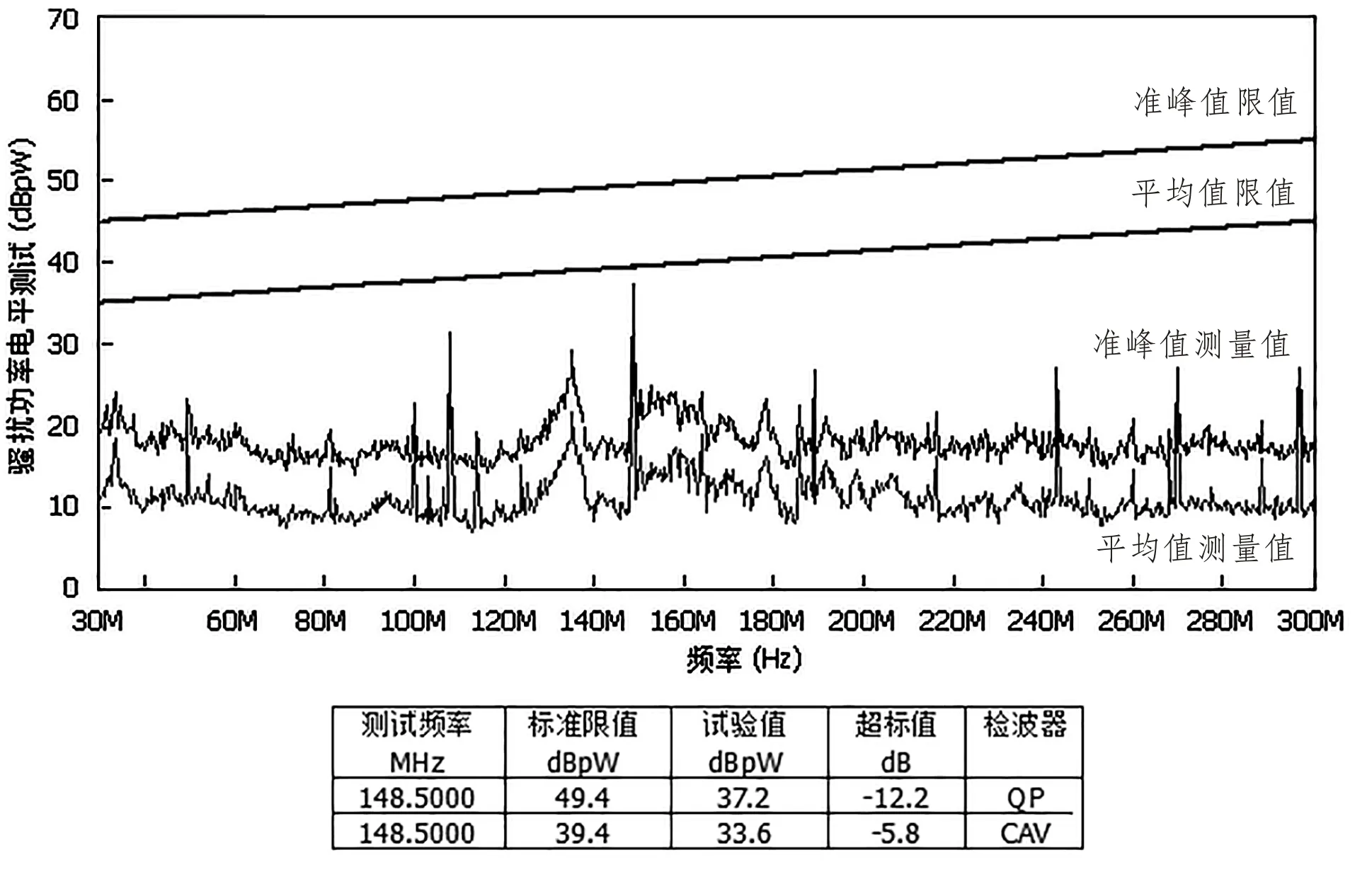

整改后该视频处理终端电源端口和HDMI端口的电源端骚扰功率最终测试结果分别如图6(a)和6(b)所示。原先

图6(a) 整改后电源端口骚扰功率测试结果

5 结语

做好时钟信号的匹配和电源供电口的滤波是解决时钟噪声干扰的常用措施,从原理图来看,前期设计时按照典型电路(见图4)设计,做好滤波电容预留,实际测试过程中可以通过调整滤波电容和时钟线上的匹配电阻值来达到最佳EMC效果。超标的148.5 MHz已符合标准限值要求,并且余量达到5 dB以上,通过测试。

图6(b) 整改后HDMI端口骚扰功率测试结果