DQPSK调制解调系统的FPGA实现

2021-10-20冯雪峰禹永植

冯雪峰,禹永植

(哈尔滨工程大学信息与通信工程学院,黑龙江 哈尔滨 150001)

数字相位调制方式具有较高的抗噪性能和较高的频带利用率且在有衰落和多径现象的信道中也有较好效果[1-2]. 四相相对相移键控(differential quadrature reference phase shift keying,DQPSK)作为多进制相位调制中的一种,拥有抗相位模糊、频带利用率高、频谱特性好、电路实现简单、综合性价比高等突出优点而成为卫星和有线电视等多种应用场景中的调制方式. 现场可编程门阵列(field programmable gate array,FPGA)具有功能强大,开发方便快捷,成本低,可不断修改编程等特点,将基带信号用FPGA芯片进行DQPSK的调制和解调,可以最大化的减小成本和产品体积,而且更加容易根据需求进行修改,满足实际的工程需求[3-5]. 本文在FPGA中设计了一种DQPSK调制解调系统实现方案,并在Vivado中进行了行为仿真,该方案具有较好的可行性[6-8].

1 DQPSK调制解调系统的整体设计

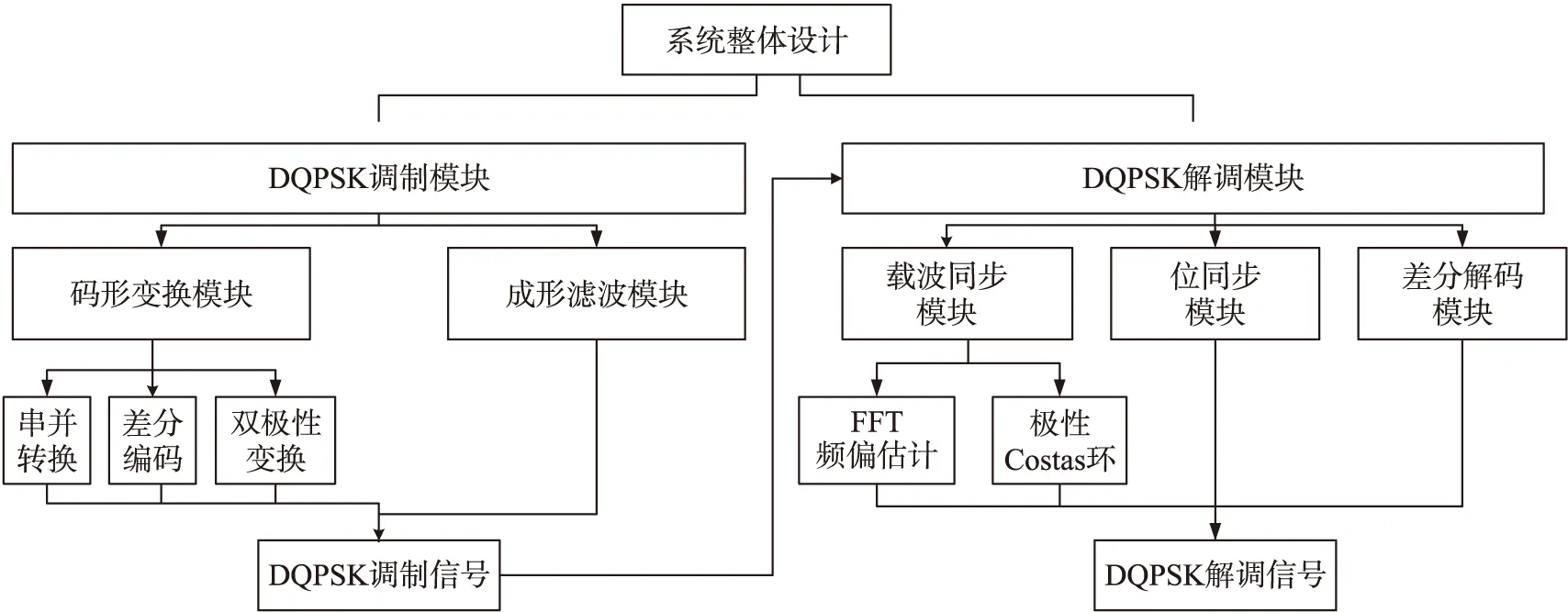

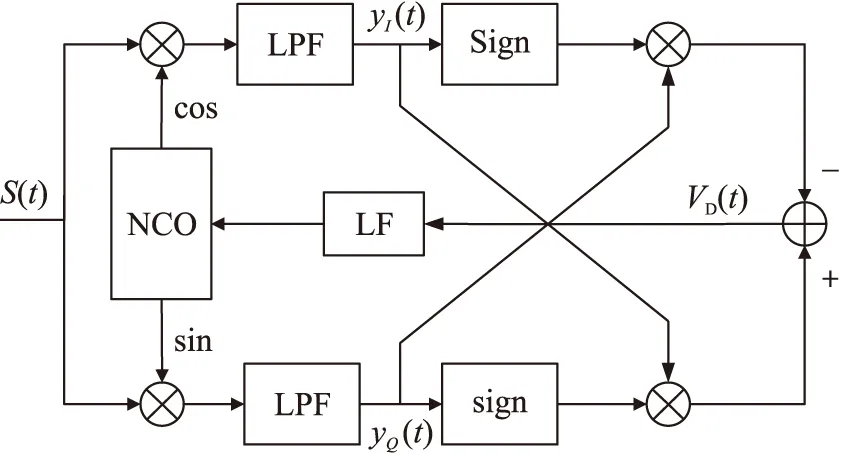

DQPSK调制解调系统分为两大部分:DQPSK调制和DQPSK解调,如图1所示. DQPSK调制包括数字控制振荡器(numerically controlled oscillator,NCO)模块、串/并转换模块、差分编码模块、成形滤波模块等[9-10]. DQPSK解调包括快速傅立叶变换(fast Fourier transform,FFT)频偏估计模块、载波同步模块、位同步模块、差分解码模块等.

图1 DQPSK调制解调系统设计框图Fig.1 Design block diagram of DQPSK modulation and demodulation system

2 DQPSK调制系统的原理及设计

数字相位调制技术即相移键控是一种载波相位随着基带信号的变化而在不同相位之间切换的调制方式. 而正交相移键控(quadrature phase shift keying,QPSK)是多进制调制技术中比较常用的,它将每两个信息比特组合成一个码元,可以看作是I、Q两路正交的二进制相移键控(binary phase shift keying,BPSK)信号调制后相加得到的,因此在相同传输速率下,拥有更高的频带利用率[11-13]. QPSK有4种不同的载波相位,且有两种取值方案,两种方案的相位相差45°. QPSK信号可表示为[14-15]

(1)

ωc是调制载波频率;φn是在第n个码元时基带信号代表的相位;Ts是码元宽度;g(t)是码元的时域信号波形. 令I(t)=∑g(t-nTs)cos(φn),Q(t)=∑g(t-nTs)sin(φn),则有

S(t)=I(t)cos(ωct)-Q(t)sin(ωct).

(2)

为了克服QPSK调制传输解调时可能出现的相位180°变化,衍生出了DQPSK相位调制方式. 首先对基带信号进行差分编码,将绝对相位转换成相对相位再进行调制,以解决相位翻转的情况. 再对差分编码后的数据进行极性变换、插值和成形滤波等处理. 最后将两路信号分别与载波信号相乘再相加得到已调信号. 本文的DQPSK信号调制流程框图如图2所示.

图2 DQPSK信号调制框图Fig.2 DQPSK signal modulation block diagram

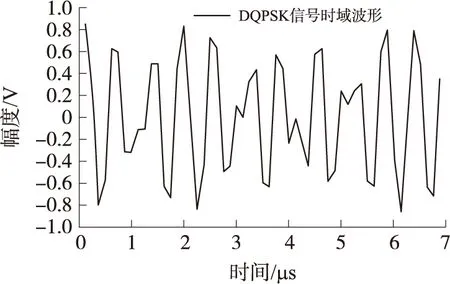

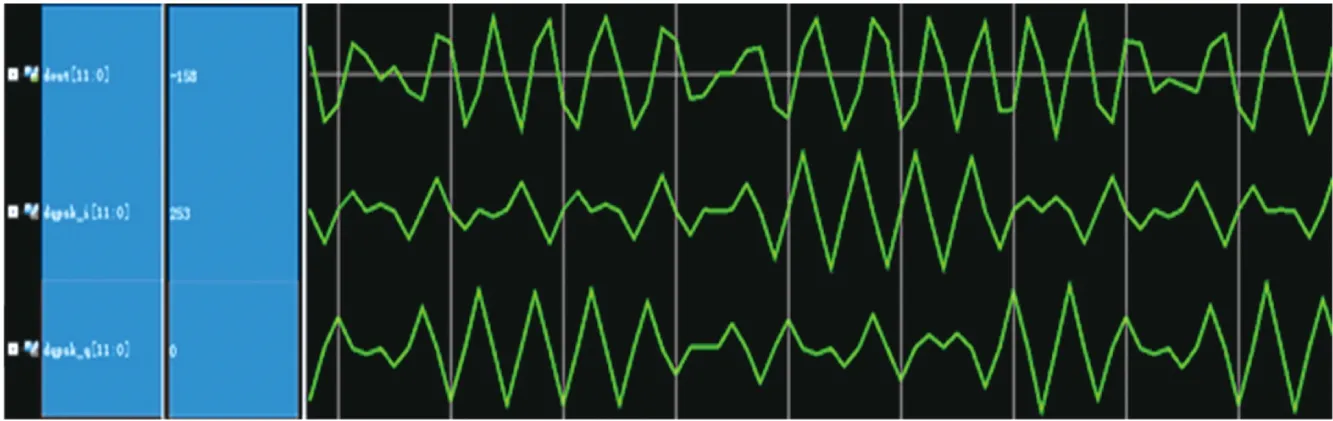

将DQPSK调制系统在Matlab中和Vivado中实现并进行仿真,定义系统采样频率为8 MHz,载波频率为 2 MHz,码元速率为1 MHz. 得到图3和图4分别为Matlab和Vivado中生成的DQPSK信号时序波形.

图3 DQPSK已调信号Matlab时序仿真Fig.3 Matlab timing simulation of DQPSK modulated signal

图4 DQPSK已调信号FPGA时序仿真Fig.4 FPGA timing simulation of DQPSK modulated signal

2.1 成型滤波模块

因为基带信号在时域上是有限的而在经过傅里叶变换后会在频谱上拥有无限的宽度,这会延伸到其他码元,造成码间串扰,增加误码率. 成形滤波器可以消除码间串扰,并且使调制信号在通带外快速衰减,大大地提高频带利用率. 本文中选择平方根升余弦滚降滤波器作为成形滤波器,其频域传输函数为

(3)

式中,α为滚降系数取值范围为[0,1],Ts是码元持续时间,f为信号频率. 随着α的增大,时域波形的衰减越快,带内的震荡变化越小,但是占用的频带带宽越大. 本文综合考虑码间串扰与频带利用率,选择滚降系数α为0.6.

2.2 差分编解码模块

为了克服QPSK信号在传输和解调过程中的相位翻转问题,使用差分编码将绝对码转换成相对码进行传输. 在差分编码中,上一个时间输出的数字基带信号与这一个时间输入的数字基带信号有异或的关系,可以根据真值表进行逻辑判断,进行Verilog程序编写.

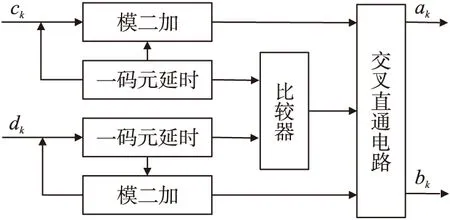

接收端显然也要将解调出来的相对码进行差分解码,差分解码器的原理图如图5所示. 两路输入信号ck、dk分别与其前一码元ck-1、dk-1进行模二加,再通过比较器来得到ck-1⊕dk-1的结果,进而控制ak、bk的取值.

图5 差分解码器原理图Fig.5 Schematic diagram of differential decoder

3 DQPSK解调系统的原理及设计

通过QPSK解调可以将基带信号从高频QPSK调制信号中分离出来. 解调的方法基本上分为相干解调和非相干解调,通常情况下相干解调的性能更好而非相干解调的电路更加简单. 在本文中的DQPSK解调采用的是相干解调的方式,在接收端根据接收数据产生一个与调制信号的载波同频同相的本地参考载波,再将调制信号与本地参考载波相乘来解调出基带信号. DQPSK解调系统主要由FFT频偏估计、载波同步、位同步、差分解码和并串转换等模块组成. 其中的核心部分是载波同步,载波同步设计的优劣直接关系到系统的解调结果. 本文中采用基于极性Costas环的QPSK载波同步跟踪算法,并利用FFT频偏估计算法进行频偏估计,提高载波同步的性能. DQPSK解调系统的设计框图如图6所示,其中LPF为低通滤波器,PD为鉴相器,LF为环路滤波器.

图6 DQPSK解调系统框图Fig.6 Block diagram of DQPSK demodulation system

3.1 载波同步模块设计

信号通过无线信道会受到影响,故接收端接收到的信号存在频率偏移. 接收端在用相干解调方式解调信号时,需要产生与接收信号同频同相的本地载波,载波同步的目的就是提取这样的载波.

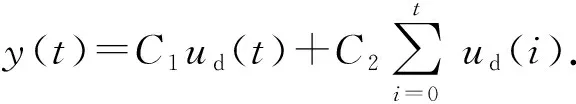

对于QPSK信号,常用的直接提取相干载波的方法主要有四次方环法、四相Costas环法与极性Costas环法等. 考虑到前两种算法需要使用大量乘法器,运算复杂,资源消耗大,而极性Costas环结构简单,易于硬件电路实现. 本文使用基于极性Costas环的载波同步方式,其工作原理如图7所示.

图7 极性Costas环工作原理Fig.7 Working principle of polar Costas ring

设图7中的输入信号为DQPSK调制信号,UI(t)和UQ(t)是本地振荡器根据鉴相误差输出的两路正交信号,这两路信号的幅度相等而相位相差180°. 其中ωc为载波频率,φ0为初始相位,θe(t)为相位误差,为UI和UQ.

S(t)=I(t)cos(ωct+φ0)-Q(t)sin(ωct+φ0),

(4)

UI(t)=cos[ωct+φ0+θe(t)],

(5)

UQ(t)=-sin[ωct+φ0+θe(t)].

(6)

将输入信号分别与本地振荡器输出的同相和正交信号相乘,再分别通过低通滤波器将混频后的信号中的高频分量滤除,得到包含同相支路误差信息的信号yI(t)和包含正交支路误差信息的信号yQ(t),

(7)

(8)

符号函数运算和相乘器、相加器构成了等效鉴相器,鉴相器输出

VD(t)=yI(t)sign[yQ(t)]-yQ(t)sign[yI(t)].

(9)

以Kd表示鉴相增益,根据yI(t)、yQ(t)的取值,VD的等效鉴相特性如下式,鉴相特性曲线以π/2为周期.

(10)

图8为载波同步在Matlab中仿真时的极性Costas环输出的本地NCO信号的频率,设载波频率为2 MHz,频率偏移为500 MHz. 由图8可知本地NCO的输出频率迅速收敛到载波频率,环路载波捕获跟踪性能良好.

图8 载波捕获跟踪过程Fig.8 Carrier acquisition and tracking process

3.2 FFT频偏估计模块设计

极性Costas环在小频偏下能够比较精确地获取信号的同步载波,但其环路捕获带宽较窄,当信号的载波频偏一旦超出环路的捕获范围,系统的解调性能会急剧恶化. 因此对于高动态场景中存在大多普勒频偏的QPSK信号,需要对其进行频偏估计处理. 本文中采用FFT频偏估计方法,基本思想是当对接收信号进行快速傅里叶变换后,对其离散频谱图进行分析,可以在一定精度下得到被估计信号的频率大小,再辅助极性Costas环进行载波估计.

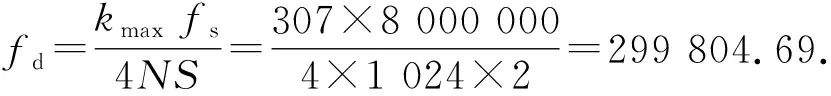

直接FFT测频法根据信号的频谱来将信号的载波频率在一定范围和精确度下计算出来,因为快速傅里叶变换计算信号频谱时间短且计算复杂度很低,所以本文中使用FFT算法来进行信号频率的估计. 将QPSK信号经过FFT变换后会得到离散的信号频谱,用采样时钟除以进行快速傅里叶变换的点数即可得到了频率分辨率. 再找出离散的信号频谱中拥有最大的幅度的谱线位置,就可以计算出大致的信号载波频率. 设y(k)在FFT后得到离散谱线最大值位置为kmax,则得到的载波频率为:

(11)

图9 FFT算法仿真图Fig.9 FFT algorithm simulation diagram

3.3 位同步模块设计

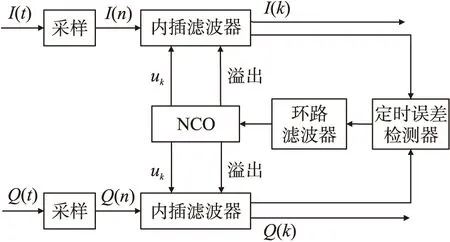

位同步也称码元同步,它是数字通信中特有的一种同步,并且在基带和频带传输中都需要位同步. 本文中的基于Gardner的位定时同步算法采用插值滤波的原理来实现位定时同步及最佳抽样点判决. 基于Gardner的位同步原理是找出两个码元的最佳采样点,从而得到这两个码元的幅度和正负情况,再找到两个码元的过渡点是否为零,最终提取出定时误差. 基于Gardner算法的位同步环路包括采样、内插滤波器、定时误差检测器、环路滤波器以及本地载波发生器NCO组成,其中载波同步模块输出的I(t)、Q(t)两路信号经过采样后,再进入到内插滤波器模块进行内插处理,其原理框图如图10所示.

图10 Gardner环工作原理框图Fig.10 Working principle block diagram of Gardner ring

e(n)=yI(n-1/2)[sign(yI(n))-sign(yI(n-1))]+yQ(n-1/2)[sign(yQ(n))-sign(yQ(n-1))].

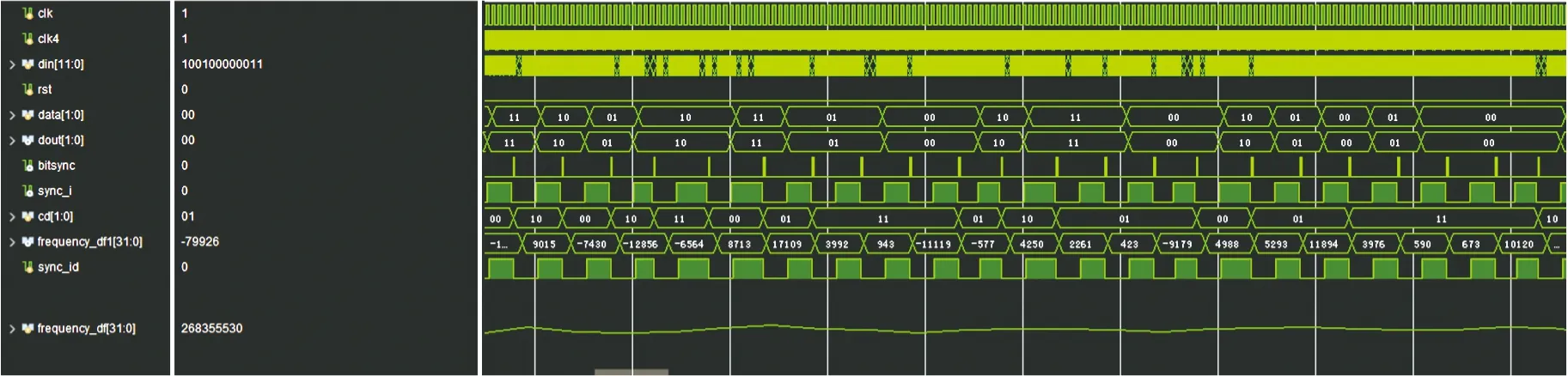

如果位同步成功,则定时误差e(n)值为0;当采样时刻落后于真实的码元时,e(n)值大于0,反之则小于0. 环路滤波器会弱化信号中高频分量对定时误差的影响,使其更加平稳,对整个环路的跟踪捕获性能有重要调节作用. NCO模块是一个相位数值递减器,根据输入的相位来产生插值基点mk和小数间隔μk,完成对位定时同步的调整控制. DQPSK解调系统通过对输入调制信号的载波同步、FFT频偏估计辅助、位同步和差分解码,最后得到了解调后的基带信号. 图11是解调系统的仿真输出波形,通过输入基带信号data与解调后的基带信号dout的对比,可以看出解调结果符合预期.

图11 解调系统仿真波形Fig.11 Simulation waveform of demodulation system

4 结论

本文研究分析了DQPSK调制解调的原理,通过Vivado软件进行开发和仿真,用硬件编程语言完成了DQPSK调制解调系统在FPGA中的实现,提出了一种可在工程上实现的DQPSK调制解调设计方案. 该方案充分利用FPGA的IP核资源,且能够克服相位模糊,可用于大多普勒频偏场景,具有良好的应用场景.