采用单元电路法的4THz单片集成混频器设计*

2021-10-15唐家轩李少甫何婷婷余蒋平唐颖颖

唐家轩,李少甫,何婷婷,余蒋平,唐颖颖

(西南科技大学 信息工程学院,四川 绵阳 621010)

0 引 言

低频段太赫兹(Terahertz,THz)技术在国内外日趋成熟,面临更高探测精度和通信速率等应用需求,高频段频谱资源的利用在世界各国具有较大竞争力。目前太赫兹时域和频域光谱检测技术在应用方面仍然存在不足[1~3]。自由电子激光器(free electron laser,FEL)和量子级联激光器(quantum cascade laser,QCL)可以解决太赫兹辐射源功率低、频谱分辨率低等面向实际应用的难题。作为高分辨率太赫兹谱仪中的重要组件,需要研究设计太赫兹谐波混频器。2016年,Bulcha B T等人设计了基于QCL的1.8~3.2 THz宽带谐波混频器[4]。美国宇航局联合 VDI 研究出 3~5 THz四次谐波混频器,主体电路集成在2 μm砷化镓基片上,这是目前为止工作频率最高的混频器[5]。国内关于混频器的报导多集中在1 THz以下频段,2020年,电子科技大学的徐一朋和纪东峰分别设计了两种1 THz单片集成混频器[6~7],进一步拓展了混频器的工作频率,验证了太赫兹较高频段混频器自主设计的可行性。

本文自主研究设计了用于偶次谐波混频的肖特基二极管,还设计了性能优异的波导—悬置微带过渡电路和滤波器,混频器主体电路集成在3 μm厚的砷化镓薄膜上。

1 混频器单元电路设计

1.1 肖特基二极管设计优化

二极管的本征截止频率可由式(1)计算得到

fs=1/2πRsCj0

(1)

根据式(1),需要通过合理的设计来降低零偏结电容Cj0和级联电阻Rs,提高二极管的本征截止频率。二极管的级联电阻Rs主要包括外延层电阻Repi,缓冲层中的扩散电阻Rspread,缓冲层电阻Rbuffer,设计时需要尽量降低这三部分阻抗,从而减小信号在二极管内部间的能量损耗。二极管的零偏置结电容Cj0可由式(2)计算得出[8],外延层电阻Repi可由式(3)和式(4)计算得出[9]

(2)

(3)

(4)

缓冲层趋肤深度可由式(5)计算得出

(5)

式中σbuf为缓冲层电导率,μ0为自由空间磁导率,f为二极管工作频率。计算得到工作频率为4 THz时,趋肤深度为0.658 μm,设计二极管缓冲层厚度为1 μm。为尽可能地降低缓冲层电阻,设计缓冲层掺杂浓度为5×1018cm-3。

Tang A Y等人发现采用垂直沟道结构可以减弱二极管内部结构在高频工作条件下引入的涡流效应、临近效应[10],本次肖特基二极管的设计依然采用垂直沟道结构。初步建立平面垂直沟道二极管的三维模型后,还需优化二极管的三维封装结构以降低二极管的寄生参量。如图1所示,具体做法为合理地减小空气桥厚度和宽度,减小空气桥和掺杂层之间的耦合电容Cfe,Cfb;合理设计焊盘间距,减小两焊盘之间的耦合电容Cpp和空气桥寄生电感Lf;减薄衬底厚度,减小两焊盘之间的耦合电容Cpp1;减薄金属焊盘厚度可以降低焊盘与缓冲层之间的耦合电容Cpad。待其他单元电路设计完成后,仿真混频器整体电路性能,不改变其他电路结构,不断调节二极管各处结构,仿真比较分析整体电路性能,实现二极管的最优化设计。

图1 肖特基二极管高频寄生参量分布

如图2所示,最终在HFSS中建立了尺寸为21.4 μm×7 μm×4.9 μm的二极管三维模型,为保证信号从肖特基接触流向欧姆接触,需要避免金属焊盘与外延层接触,同时保证足够的欧姆接触面积,设计金属焊盘与外延层之间的距离为0.2 μm。此外,设计衬底长度略长于缓冲层长度,避免在实际制作中二极管两侧的爬坡金属和缓冲层、外延层接触。

图2 反向并联二极管模型

如图2所示,由于两只二极管在结构上完全对称,根据二极管三维模型尺寸,如图3所示,利用半导体仿真软件SILVACO 1︰1构建单管肖特基结模型,并正确调用迁移率模型、隧穿模型、复合模型等[11],仿真得到二极管的I-V特性曲线。对I-V特性曲线进行理论分析计算,可进一步得到二极管的反向饱和电流Is和理想因子n。

图3 肖特基二极管管芯模型

根据式(6)计算得到理想因子n

(6)

式中q为元电荷,k为玻尔兹曼常数(1.37×10-23J/K),ΔV为二极管两端电流分别为10 μA和100 μA对应的电压差值,T为绝对温度。

计算出理想因子n后,在线性区任取一点,根据式(7)可计算出二极管的反向饱和电流Is

Is=I(V)exp-(qV/nkT)

(7)

反向击穿电压可由式(8)计算得出

Vbr=60(Eg/1.1)3/2(ND/1016)-3/4

(8)

式中Eg为半导体材料的禁带宽度,砷化镓材料的禁带宽度为1.42。

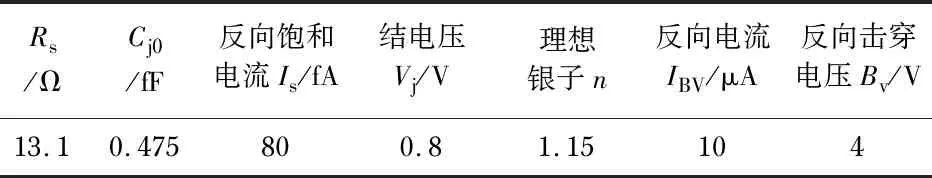

如表1所示,结合半导体软仿和理论分析计算,得到了自主设计的肖特基二极管SPICE参数理论参考值。由于未能对自主设计的二极管进行实物测试,表1中所列的部分SPICE参数值还比较理想。

表1 肖特基二极管SPICE参数理论参考值

1.2 射频过渡电路设计

射频信号经标准波导WM57(3.3~5 THz)输入,射频信号通过E面探针过渡结构耦合到悬置微带线上。为了方便装配和固定主体单片电路,在波导右侧伸出一段砷化镓基片搭在石英基片上。采用EPO-TEK®H20-HC银胶,使波导右侧微带与屏蔽腔壁接触,实现射频信号和直流分量的接地[12]。射频过渡电路模型及仿真结果如图4所示,在3.4~4.4 THz频段范围内端口1的回波损耗优于15 dB,传输损耗小于2.3 dB,满足超宽带混频器的设计要求,可用于整体电路设计。

图4 射频过渡电路设计优化结果

1.3 本振双工器设计

1.3.1 滤波器设计

本振滤波器和中频滤波器均采用开口谐振单元结构,如图5所示。本文对文献[7]提出的开口谐振环滤波器结构加以改进,将纵向对称的开口谐振环拆成纵向非对称的开口谐振单元,基于开口谐振单元的滤波器结构简单紧凑,通过金属线枝节之间的耦合效应、金属线和基板边缘的耦合效应引入了更多的电容和电感,进一步提升了滤波器的带外抑制特性。

图5 滤波器结构改进示意

本振滤波器设计优化结果如图6所示,在0~20 GHz中频频率范围内,信号通过该滤波器产生的传输损耗小于0.06 dB,回波损耗优于30 dB,本振信号通过该滤波器产生的传输损耗小于0.8 dB,回波损耗优于15 dB,对混频产生的二次谐波信号抑制大于29 dB,回波损耗接近于0 dB,有效反射了混频产生的本振二次谐波信号,使其重新进入管对参与混频,提高了信号能量的利用率,可用于整体电路设计。

图6 本振滤波器设计优化结果

中频滤波器采用5880软基片,中频滤波器模型和仿真优化结果如图7所示。该滤波器在1~50 GHz频率范围内,带内插损小于0.2 dB,回波损耗优于30 dB,对本振频率范围内的信号抑制度大于35 dB,可用于整体电路设计。

图7 中频滤波器设计优化结果

1.3.2 跨传输线本振双工器模型验证

射频信号输入频率与本振信号输入频率差距过大时,传统的高次谐波混频电路不再适用,需要提出新的电路结构来抑制混频产生的高次谐波分量[13]。为降低本振电路设计难度和整体电路复杂度,将砷化镓电基片做成异形,设计了混合悬置微带线,中频滤波器采用微带线,利用混合传输线对信号的衰减来保证混频器三个端口间的高隔离度,减轻了本振滤波器设计难度。

本振双工器由本振过渡结构、本振滤波器和中频滤波器组成,将靠近二极管的一端设为端口1,本振波导输入设为端口2,中频输出设为端口3,跨传输线的本振双工器三维模型及隔离性能仿真结果如图8所示。仿真结果表明S21和S31均优于20 dB,S参数仿真结果表明在1 700~4 400 GHz范围内该双工器的隔离性能较好。

图8 跨传输线本振双工器设计优化结果

2 混频器整体电路仿真设计

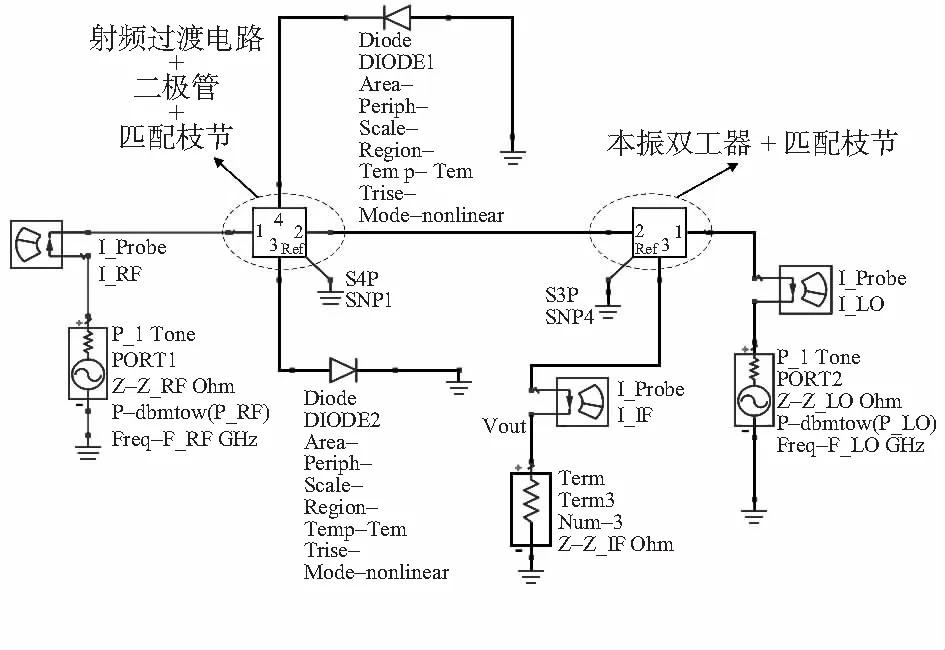

在HFSS软件中完成对射频过渡、反向并联二极管对、本振双工器的最优化设计后,将各个单元电路的仿真结果以SNP文件形式导入到ADS中,对整体电路优化仿真。经过反复仿真优化,完成二极管两端匹配枝节的设计,可先将整体电路看成两部分,在ADS中搭建的整体电路模型如图9所示。

图9 ADS中混频器整体电路模型

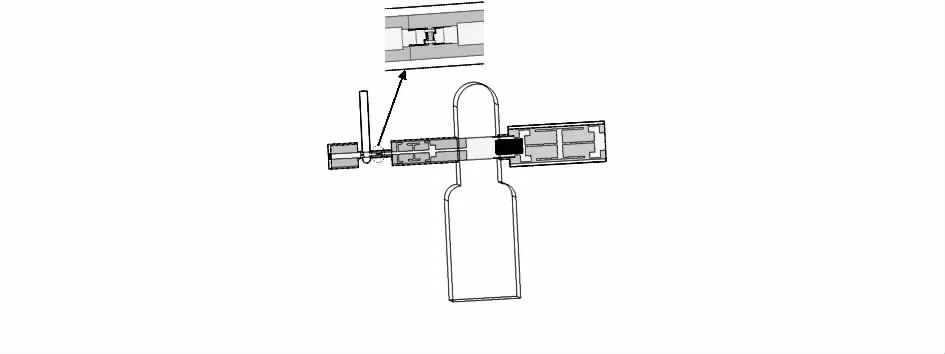

在HFSS软件中将匹配枝节和各个单元电路拼接,再对整体电路模型进行仿真,这一步仿真周期长,最终导出S5P文件,在ADS中进行谐波平衡分析。若仿真结果未达到设计要求,需要重新调节二极管两端的匹配枝节,直到S5P文件在ADS中的仿真结果达到设计要求,即完成设计,最终混频器的三维模型如图10所示。采用仅固定基片两端而让主体电路悬空放置的方式,避免了导电胶对高频电路结构的影响,减轻了实际装配对混频器性能的恶化,同时保证了基片的稳定放置。值得说明的是,在3.4~4.4 THz频段内,由于主体砷化镓电路传输线的单位传输损耗较大,严格限制了异形砷化镓基片的长度,保证了薄基片切割的成品率。

图10 完整混频器三维模型

混频器最终仿真结果如图11所示,混频器输入信号在3.4~4.4 THz范围,本振驱动动率5 dBm时,单边带下变频损耗在57.3~64.3 dB范围内,射频回波损耗优于11 dB。混频器变频损耗曲线在3.4~4.0 THz频率范围内平坦度较好,且变频损耗优于60 dB,整体电路性能较为稳定。

图11 整体电路仿真结果

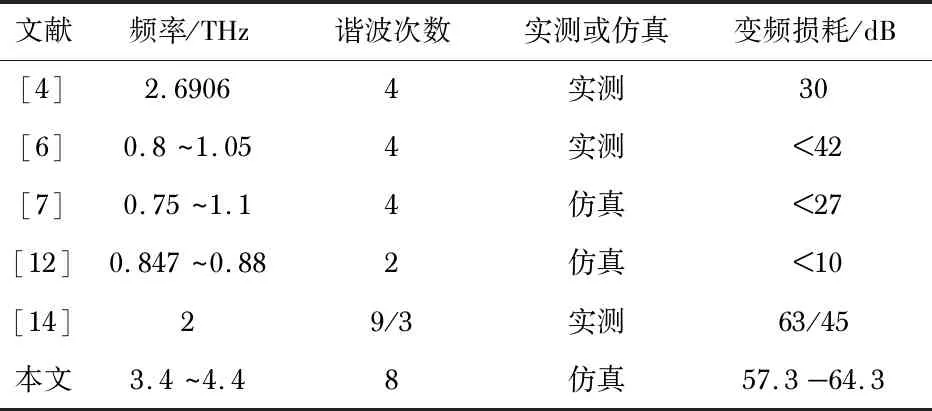

表2列出了本文设计结果与国内外相关文献报导的混频器性能比较。

表2 较高频段谐波混频器性能比较

3 结 论

本文提出了采用混合传输线的主体电路结构,仿真结果表明:混频器三个端口之间的隔离度较好。利用HFSS软件对混频器各单元电路进行了仿真优化设计,再联合ADS软件对混频器整体电路进行仿真优化,整体电路仿真结果较好。本文初步验证了3 THz以上高次谐波混频器自主设计的可行性,结果具有重要意义。与国内加工单位沟通,自主设计的混频二极管是可加工的,受限于混频器的加工成本和加工周期,暂时还未能进行实物测试。此外,受限于当前国内二极管的加工工艺,自主设计的二极管截止频率仍然有限。今后的研究将集中于肖特基二极管的设计和实测,得到更加准确的二极管SPICE参数,提高混频器仿真结果的准确性。